近日,日本Rapidus 首席執(zhí)行官 Atsuyoshi Koike 在接受《日經(jīng)新聞》采訪的時候表示,與目前其他日本公司生產(chǎn)的標(biāo)準(zhǔn)芯片相比,2nm芯片的成本將增加十倍。Rapidus是日本政府支持的半導(dǎo)體財團(tuán),其成立目的是超越世界領(lǐng)先的芯片制造商。他們認(rèn)為,其2nm 芯片對日本至關(guān)重要,因為其中一些芯片將用于對國家安全至關(guān)重要的高性能計算應(yīng)用,而其他芯片也能用于自動駕駛汽車和機(jī)器人等創(chuàng)新民用應(yīng)用。

“2nm 芯片將比當(dāng)今先進(jìn)節(jié)點(diǎn)制造的芯片貴得多,與當(dāng)今日本制造的‘主流’芯片(45nm)相比,價格上漲十倍,這是一個巨大的飛躍。”Atsuyoshi Koike說。不過,即使如此貴,Atsuyoshi Koike預(yù)計,在他們于2027 年開始 量產(chǎn)2nm之后,也有公司愿意為此買單。

芯片的成本構(gòu)成

眾所周知,隨著 SoC 變得越來越復(fù)雜,圍繞它們的經(jīng)濟(jì)因素也變得越來越復(fù)雜。其中包括要集成的功能和 IP、上市速度、功率和性能規(guī)格、金屬層數(shù)、存儲器的配置方式和使用的存儲器數(shù)量以及目標(biāo)市場等所有內(nèi)容。其中每一個都有一個價格,并且它們加起來可以是一個非常大的數(shù)字。

Synopsys也在一篇博客文章中表示,每個芯片設(shè)計項目都是獨(dú)一無二的,但有五個基本因素會影響總體成本:

第一是內(nèi)容庫(Content Libraries);據(jù)介紹,所謂內(nèi)容庫由芯片設(shè)計項目中使用的第三方IP組成,包括常用功能、輸入和輸出(I/O)電路以及片上存儲器。內(nèi)容庫許可費(fèi)各不相同,但可能高達(dá)數(shù)千萬美元。此外,公司還必須支付每個芯片的使用費(fèi),這應(yīng)該計入項目預(yù)算。

第二是EDA工具;EDA工具可用于虛擬布局電路、模擬操作和驗證性能。EDA 軟件有多種形式,包括本地、云托管和軟件即服務(wù) (SaaS)。定價可以基于許可、基于使用或兩者的組合。此外,EDA 工具還需要強(qiáng)大的計算機(jī)和大量存儲容量,這意味著需要投資本地或云基礎(chǔ)設(shè)施。

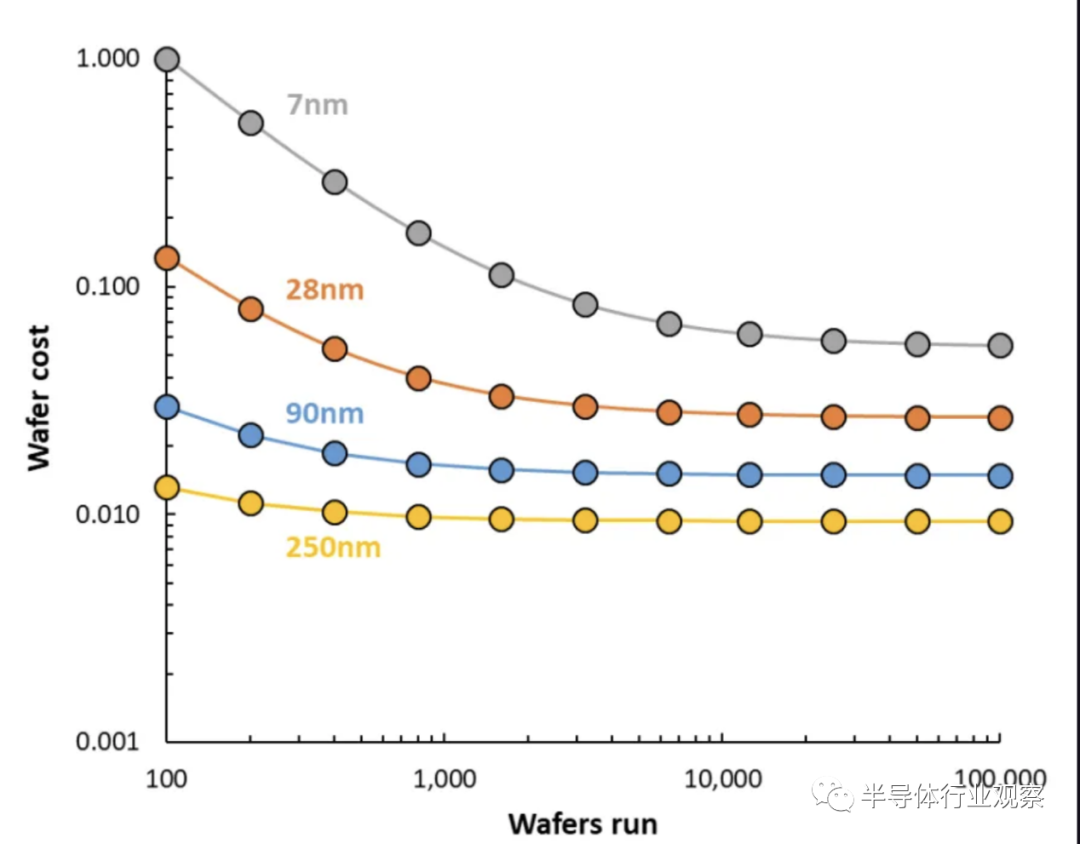

第三是制造芯片的代工廠按硅片收費(fèi);芯片越小,組織在每個晶圓上可以獲得的芯片就越多。然而,隨著芯片尺寸變小,其他設(shè)計成本(例如研發(fā)成本)也會變得更高。控制芯片設(shè)計成本意味著在高效晶圓使用和現(xiàn)實研發(fā)之間找到平衡。

第四是時間;產(chǎn)品進(jìn)入市場的速度越快,項目的整體投資回報率就越高。除了設(shè)計芯片所花費(fèi)的時間之外,公司還必須考慮流片和代工生產(chǎn)之間的滯后時間。每個設(shè)計都存在缺陷,在生產(chǎn)開始之前,設(shè)計師和晶圓廠必須解決這些缺陷。

最后,生產(chǎn)前的最后一步包括預(yù)測新芯片的需求并向代工廠承諾訂單。這是一項復(fù)雜且高風(fēng)險的操作。如果您訂購的芯片太少,您將出現(xiàn)供應(yīng)短缺并可能會損失銷售;如果您訂購太多,您可能會在未使用的庫存上浪費(fèi)數(shù)千甚至數(shù)百萬美元。

此外,工藝的良率,芯片設(shè)計的質(zhì)量和封測,也都是芯片的成本構(gòu)成,由此可見,計算芯片的成本,并不是一件簡單的事情。

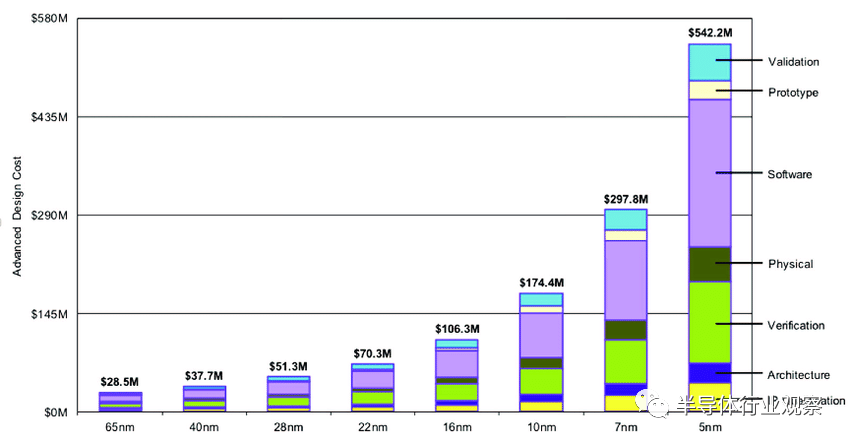

相關(guān)資料顯示,在主流節(jié)點(diǎn)(40 納米到 65 納米)上,如果從頭開始,新芯片的價格大約為 4000 萬美元到5000萬美元之間。但這些節(jié)點(diǎn)的良率很高,而且軟件開發(fā)成本也較低,且這些芯片在功能上并不處于領(lǐng)先地位,那就意味著往更先進(jìn)的工藝前進(jìn),成本會繼續(xù)飆升。這從IBS提供的數(shù)據(jù)可以看到。如圖所示,進(jìn)入到5nm時代,芯片的設(shè)計成本可以飆升到5.4億美元,在工藝?yán)^續(xù)往后走,成本的繼續(xù)升高是可以預(yù)期的。

不同工藝節(jié)點(diǎn)下的芯片設(shè)計成本

2nm,貴在哪里?

要討論2nm貴在哪里,如上所述,這同時是一個復(fù)雜的問題。

不過,據(jù)筆者從相關(guān)供應(yīng)鏈了解到。進(jìn)入了這些先進(jìn)工藝,無論是IP,還是EDA工具,其成本的提高都是能夠理解的。而進(jìn)入到這些先進(jìn)芯片,因為一次性流片成本較高,這就使得相關(guān)驗證成本水漲船高,這從IBS提供的上圖可以看到,進(jìn)入到2nm芯片時代,設(shè)計的成本是可以預(yù)期的。

值得一提的是,伴隨著這些先進(jìn)工藝而生的是先進(jìn)制造和封裝工藝,這帶來的成本也是不容忽視的。

以制造端為例,根據(jù)IBS對晶圓廠的先進(jìn)工藝投資測算,如果要建設(shè)一個3nm工藝,月產(chǎn)4萬片的晶圓生產(chǎn)線,成本約為150億到200億美元。據(jù)臺灣聯(lián)合報之前報道,臺積電將斥資 1 萬億新臺幣(約合 339 億美元)在臺灣臺中市建造一座晶圓廠,生產(chǎn) 2 納米芯片。Rapidus首席執(zhí)行官Atsuyoshi Koike此前在接受采訪時曾表示,公司需要投入2萬億日元用于研發(fā)才能開始試生產(chǎn)2nm,然后需要投資3萬億日元才能開始量產(chǎn)2nm芯片。

其中,EUV***和相應(yīng)配套材料的成本增加,必然會是一個重要影響因素。

從DUV往EUV***推進(jìn)的時候,作為芯片制造的主要成本之一的環(huán)節(jié)光刻成本有了新的提升。但在即將進(jìn)入的high na euv光刻制造時代,單臺***的制造成本將會從1億多直接飆升到三億多。雖然芯片在制造中使用的EUV的層數(shù)不會太多,例如據(jù)相關(guān)報道,在3nm工藝的時候,會采用多大25層EUV光刻曝光工藝。由此可見,這在進(jìn)入2nm時代,勢必會帶來成本的提升。

進(jìn)入到EUV時代,還有一個輔料需求增加,且成本會飆升,那就是掩模組(mask set)。

按照Semianalysis的報道,在 90nm 至 45nm 的代工工藝節(jié)點(diǎn)上,掩模組的成本約為數(shù)十萬美元。28 納米工藝的價格已超過 100 萬美元。對于 7nm,成本增加超過 1000 萬美元,而現(xiàn)在,當(dāng)我們跨越 3nm 障礙時,掩模組將開始進(jìn)入 4000 萬美元范圍。

晶圓成本的變化

關(guān)于芯片制造成本的飆升,我們可以從臺媒泄露的臺積電在相關(guān)晶圓報價上略知一二。

據(jù)Digitimes報道,與 N5(5 納米級)生產(chǎn)節(jié)點(diǎn)相比,臺積電將把使用其領(lǐng)先的 N3(3 納米級)工藝技術(shù)加工的晶圓的價格提高 25%。換而言之,采用臺積電領(lǐng)先的 N3 制造技術(shù)加工的一塊晶圓將花費(fèi)超過 20,000 美元 。作為對比,N5 晶圓的成本約為 16,000 美元,如下圖所示。

報道進(jìn)一步指出,臺積電將為其即將推出的 2nm 節(jié)點(diǎn)進(jìn)一步提高芯片生產(chǎn)價格。新的晶圓價格預(yù)估表明,臺積電將對 2nm 芯片每片晶圓收取 25,000 美元的費(fèi)用。

誰在競爭2nm?

正因為2nm無論是芯片設(shè)計還是建造晶圓廠成本都是如此昂貴,所以可以預(yù)期的是,僅有少量的廠商能夠跨入2nm這個階段。在Fabless方面,我們認(rèn)為英偉達(dá)、蘋果、高通、MTK和博通等領(lǐng)先廠商會是首批使用2nm的客戶。在晶圓制造方面,則和大家所了解的一樣,除了臺積電、三星和Intel以外,文章開頭提到的日本Rapidus會是其中的一個玩家。

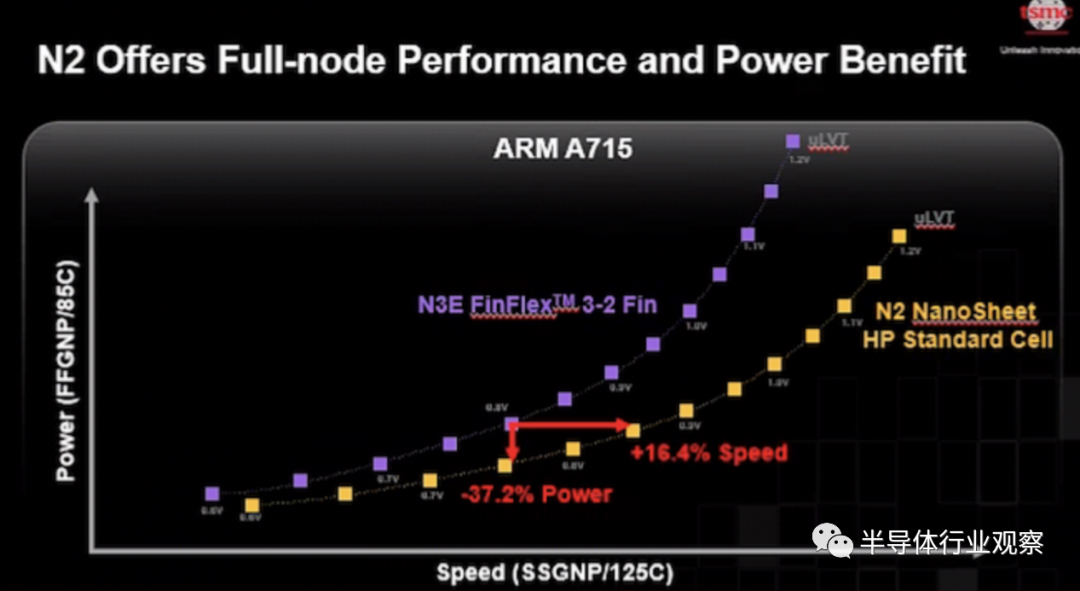

首先看臺積電方面,他們在去年首先推出初始版本的2nm工藝是該代工廠第一個使用環(huán)柵 (GAAFET) 晶體管的節(jié)點(diǎn),臺積電將其稱為 Nanosheet 晶體管。與當(dāng)前 FinFET 晶體管相比,GAAFET 的優(yōu)勢包括降低漏電流(因為柵極位于溝道的所有四個側(cè)面),以及調(diào)整溝道寬度以獲得更高性能或更低功耗的能力。

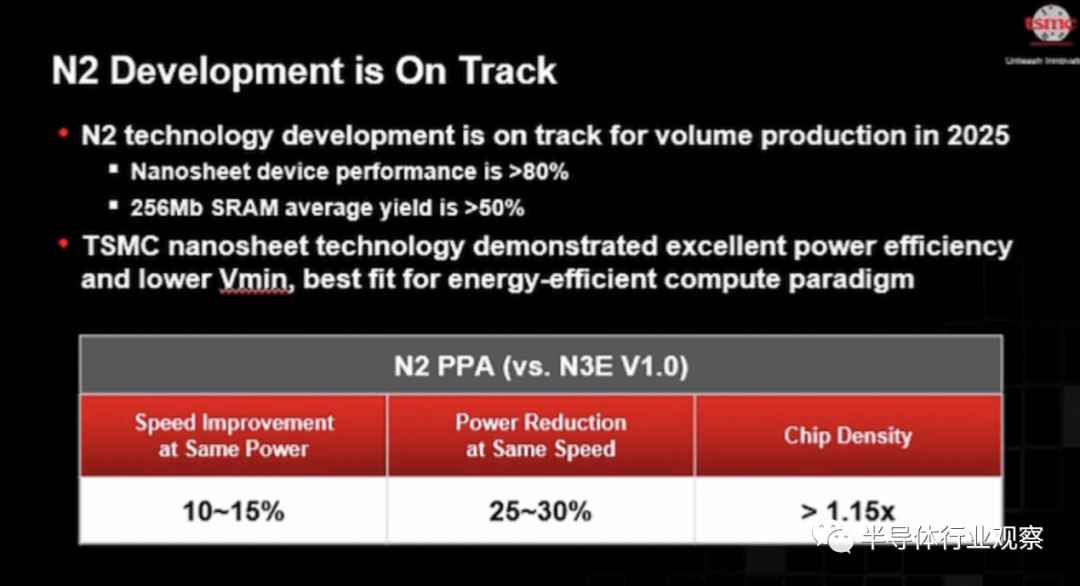

臺積電去年推出這項技術(shù)時表示,在相同功耗和復(fù)雜度的情況下,可以將晶體管性能提升10%到15%,或者在相同時鐘和晶體管數(shù)量的情況下,將功耗降低25%到30%。該公司還表示,N2 將提供比N3E高 15% 以上的“混合”芯片密度,這比去年宣布的 10% 密度增加有所增加。

在今年的技術(shù)大會上,臺積電表示,N2技術(shù)開發(fā)已步入正軌,該節(jié)點(diǎn)將于2025年進(jìn)入大批量生產(chǎn)(可能是2025年很晚)。該公司還表示,在進(jìn)入 HVM 兩年前,其 Nanosheet GAA 晶體管性能已達(dá)到目標(biāo)規(guī)格的 80% 以上,256Mb SRAM 測試 IC 的平均良率超過 50%。

臺積電的 N2 系列將在 2026 年的某個時候升級,屆時該公司計劃推出其 N2P 制造技術(shù)。N2P 將為 N2 的 Nanosheet GAA 晶體管添加背面電源軌技術(shù)。公司還在準(zhǔn)備 N2X——一個專為高性能計算 (HPC) 應(yīng)用(例如需要更高電壓和時鐘的高端 CPU)量身定制的制造工藝。

在三星方面,他們也表示,公司也將于將于 2025 年開始大規(guī)模生產(chǎn)用于移動應(yīng)用的 2nm 芯片。三星還將在2026年提供用于高性能計算的2納米芯片生產(chǎn),并在2027年提供汽車芯片的工藝。

該公司表示,與去年推出的 3nm 工藝相比,其 2nm 工藝的性能和能效分別提高了 12% 和 25%,是芯片制造商中率先做到這一點(diǎn)的。三星表示,其 2nm 工藝還提供比 3nm 工藝小 5% 的芯片。該公司還表示,將于 2027 年開始量產(chǎn)采用 1.4 納米工藝的芯片。

來到Intel,他們在今年三月初的一場會議上透露,公司已經(jīng)完成了其 1.8 納米和 2 納米制造工藝開發(fā)。該公司將于 2024 年開始在內(nèi)部和第三方產(chǎn)品中使用 1.8 納米和 2 納米制造工藝。他們表示,Intel 18A 每瓦性能提高 10%。Intel 20A 的每瓦性能提高了 15%。

至于rapidus,他們則計劃通過和IBM、IMEC等機(jī)構(gòu)合作,以推進(jìn)其2nm研發(fā)。

毫無疑問,在技術(shù)以外,這是一場當(dāng)之無愧的金錢競賽。

審核編輯:劉清

-

存儲器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163598 -

EDA工具

+關(guān)注

關(guān)注

4文章

264瀏覽量

31712 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1001瀏覽量

54811 -

SoC芯片

+關(guān)注

關(guān)注

1文章

608瀏覽量

34865 -

EUV光刻機(jī)

+關(guān)注

關(guān)注

2文章

128瀏覽量

15094

原文標(biāo)題:2nm,貴在哪里?

文章出處:【微信號:晶揚(yáng)電子,微信公眾號:晶揚(yáng)電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

2nm芯片貴在哪里?誰在競爭2nm芯片?

2nm芯片貴在哪里?誰在競爭2nm芯片?

評論