復位的用途

復位信號幾乎是除了時鐘信號外最常用的信號了,幾乎所有數字系統在上電的時候都會進行復位,這樣才能保持設計者確定該系統的系統模式的狀態,以便于更好的進行電子設計,并且在任意時刻,確保使用者總能對電路系統進行復位,使電路從初始的狀態開始工作。

總結下來用途如下:

「使電路在仿真時具有可知的初始值」 :通常在仿真時未給入初試狀態又未經復位,那么這段代碼的初始值是不定態,會經常會出現X或者Z,也就未知態。

「使實際電路在復位后從確定的初始狀態開始運行」 :在數字系統中,很多電路都要求從給定的初始狀態上開始運行,避免電路工作于不可預知的狀態,并因此導致異常或者致命的故障。

「使電路在陷入異常狀態時能通過復位回到可控的初始狀態」 :通常一個設計者無法保證所設計的數字邏輯電路在任何情況下都不會發生異常或者出現故障,假如電路無法自己返回正常狀態,可以使用復位電路,強制使電路從初始狀態開始工作。

盡管復位極為重要,但是復位電路在設計中是最常忽視的方面。一個不正確設計的復位本身可以表現為一個不可重復的邏輯錯誤。

復位電平的選擇

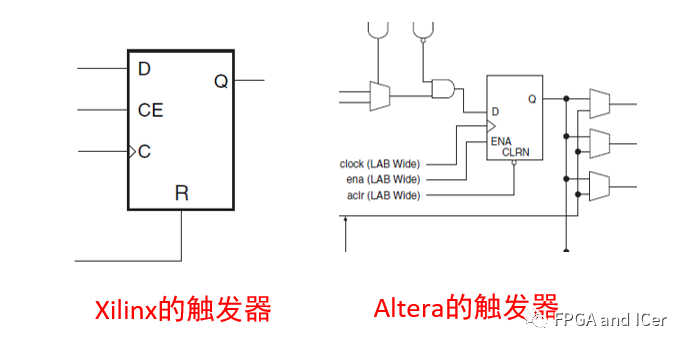

有關復位電平,實際上是與FPGA芯片內部的觸發器結構有關,在之前的博文有提到過。作為xilinx 7系列觸發器,其 R 端口既可用作同步置位/復位端口,也可用作異步預設/清除端口,但無論哪種方式,都是「高電平有效」。Altera的是「低電平有效」。

不同公司的觸發器結構

如果RTL代碼采用了低電平有效的復位模式,綜合器將在復位信號驅動寄存器SR控制端之前的插入一個反相器(interver)。你必須使用一個查找表(look up table)來實現反向器,以利用LUT的輸入端口。低電平有效的控制信號帶來的額外的邏輯可能拉長了執行時間(runtime),將導致更低的FPGA資源利用率,也將影響時序和功耗。

同步復位

同步低復位

同步低復位的代碼如下:

modulereset( inputclk, inputrst, input[1:0]in, outputreg[1:0]out ); always@(posedgeclk)begin if(rst=='b0) out<=?'d0?; ????????else? ????????????out?<=?in?; ????end endmodule

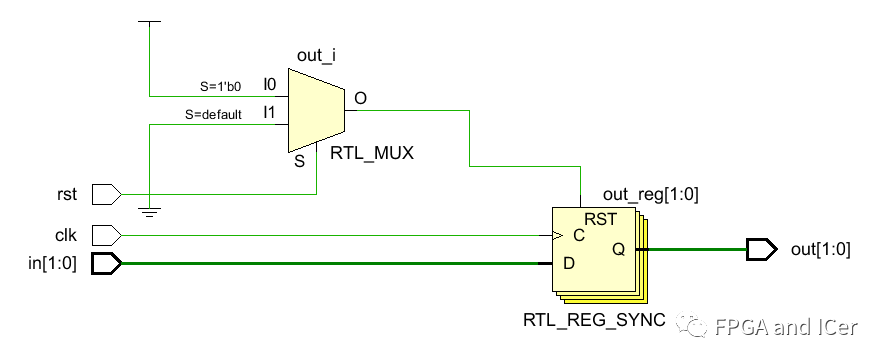

在使用vivado RTL 分析對應的電路結構如下:

RTL電路結構

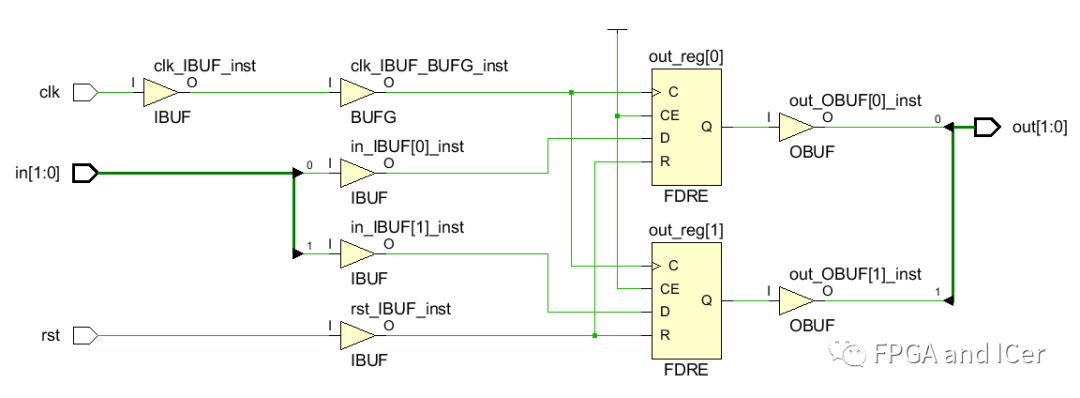

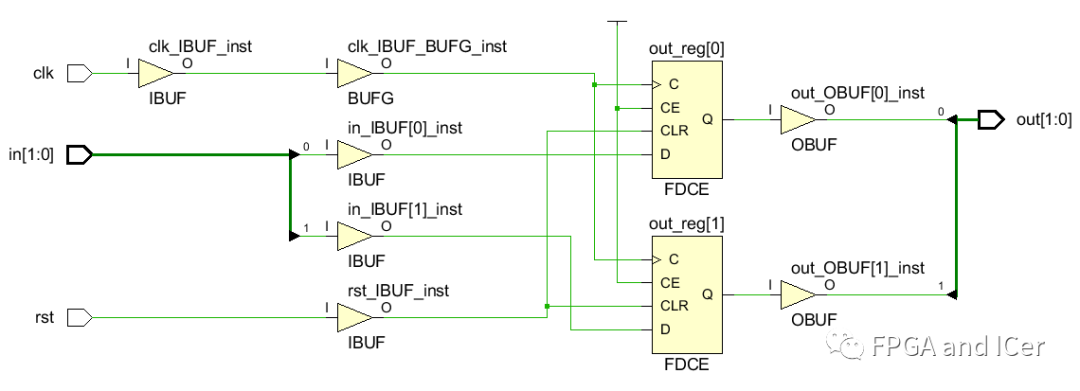

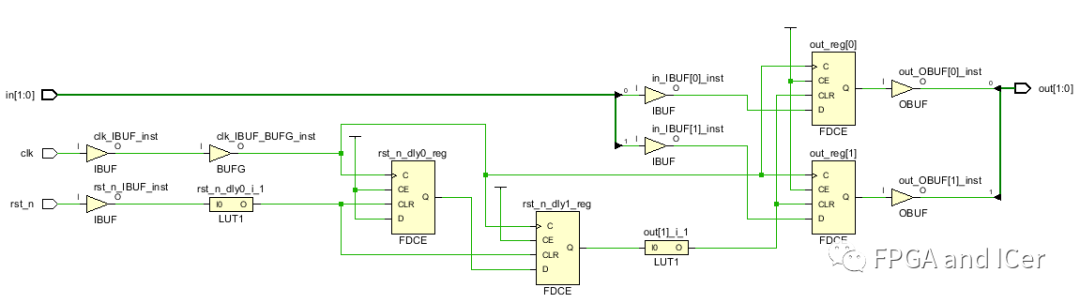

使用vivado綜合后結構如下:

綜合后的實際電路

由于xilinx的器件結構中的觸發器為高復位,所以會引入LUT實現復位信號的功能,引入額外的邏輯資源。

同步高復位

同步高復位的代碼如下:

modulereset( inputclk, inputrst, input[1:0]in, outputreg[1:0]out ); always@(posedgeclk)begin if(rst=='b1) out<=?'d0?; ????????else? ????????????out?<=?in?; ????end endmodule

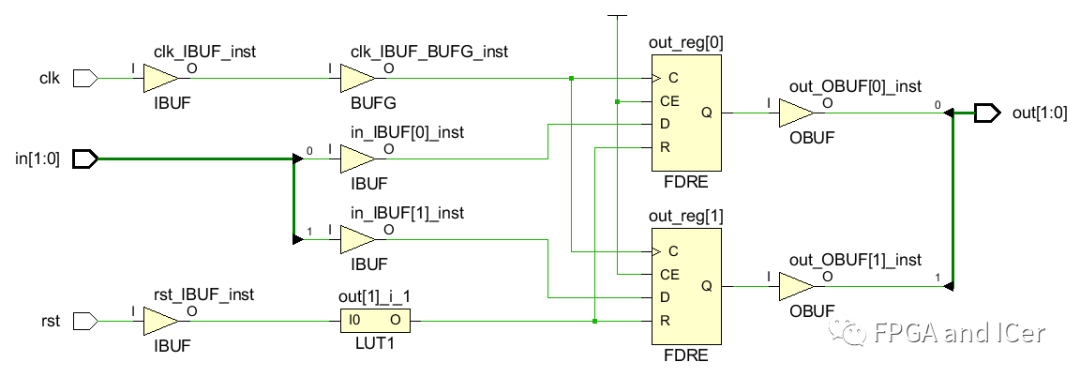

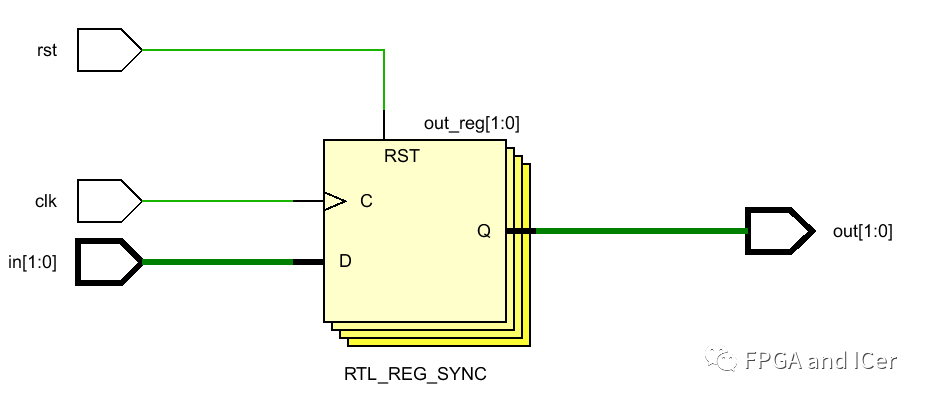

在使用vivado RTL 分析對應的電路結構如下:

RTL電路結構

使用vivado綜合后結構如下:

綜合后的實際電路

由于xilinx的器件結構中的觸發器為高復位,所以在使用同步高復位時,直接會將復位信號連接到復位輸入端。

同步復位的優缺點

「同步復位的優點:」

有利于仿真器仿真;

設計的系統全部是同步時序電路,有利于時序分析,可綜合出更高性能的電路;

由于同步復位信號是被時鐘啟動(Launch)和鎖存(Latch),而啟動和鎖存的時鐘彼此同步,所以復位信號的到達時間(Arrival Time)和所需時間(Required Time)就能很輕易地確定并進行正確的時序裕度(slack)分析。

可以濾除高于時鐘頻率的復位毛刺,保證系統更加穩定;

對于邏輯器件內部的資源存在同步復位的端口時,使用同步復位時會節省FPGA的邏輯資源。

「同步復位的缺點:」

對于邏輯器件的目標庫內的 DFF 都只有異步復位端口的情況,如果采用同步復位的話,綜合器就會在寄存器的數據輸入端口插入組合邏輯,這樣就會一方面額外增加 FPGA 內部的邏輯資源,另一 方面也增加了相應的組合邏輯門時延,因此較難綜合出更高性能的電路。

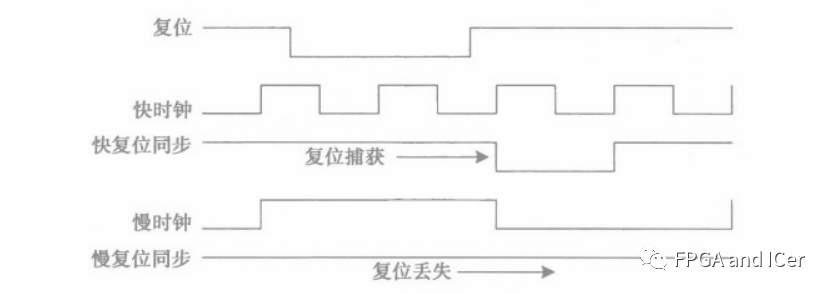

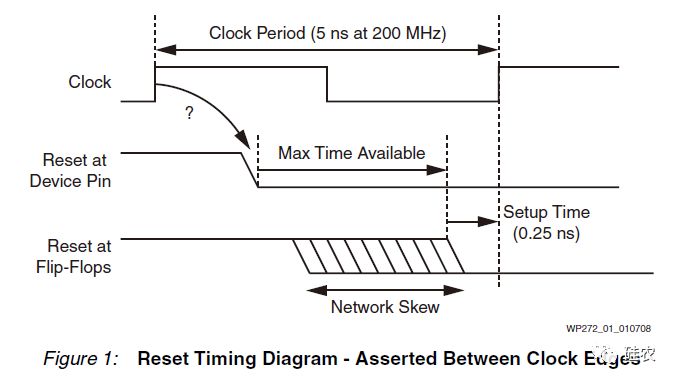

復位信號的有效時長必須大于時鐘周期,才能真正被系統識別并完成復位。同時還要考慮諸多其他因素(諸如時鐘偏移、組合邏輯路徑延時、復位延時等),所以復位信號有時需要脈沖展寬,用以保證時鐘有效期間有足夠的復位寬度(此處可當做單信號的跨時鐘處理,類似單信號的跨時鐘處理方式)。

復位丟失示例

上圖為快時鐘的同步信號傳輸給慢時鐘后造成復位丟失,具體解決方法可參考單信號的快時鐘域轉慢時鐘域的跨時鐘處理方法。

某些情況不太適用同步復位

在一些情況中,在出于節省功耗的目的而使用門控時鐘時,就可能出現問題。在復位信號發出時,時鐘可能關閉。在這種情況下只能使用異步復位,并在時鐘恢復前移除復位信號。

又如不同的芯片在復位的時候不能把自身的總線接口重置成三態或者輸入狀態,而是總線上有多個芯片同時通過接口將數據輸出到總線,總線上將出現電平沖突,嚴重時可能導致接口損壞。因此,在這種時候,同步復位就不太適用。

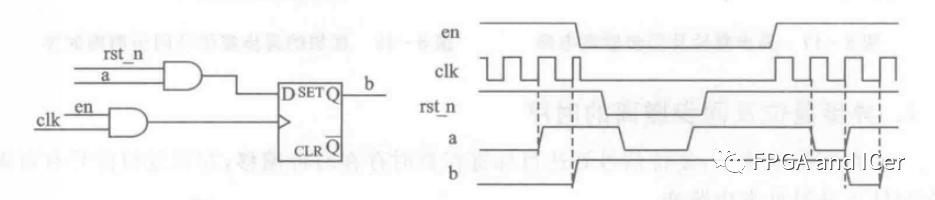

門控時鐘導致同步復位丟失

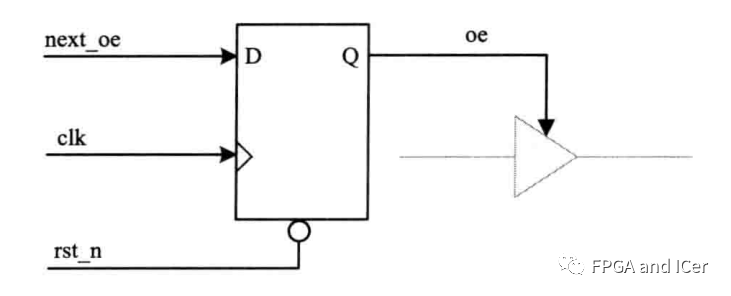

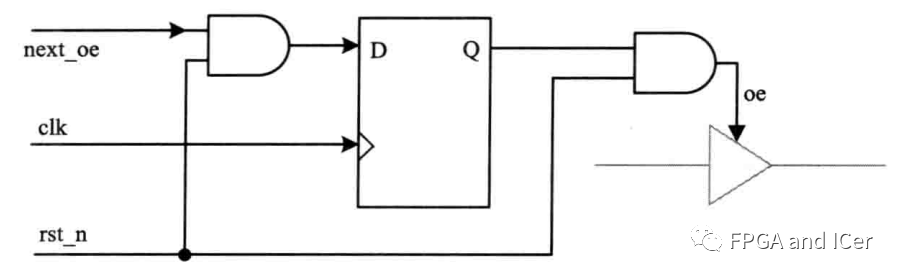

如果 ASIC/FPGA有內部三態總線,需要時鐘來產生復位。為了阻止芯片上電時內部三態總線出現競爭,芯片應當有下圖所示的異步上電復位。

輸出使能的異步復位

當然也可以使用同步復位信號,但是也必須使用復位信號直接撤銷三態使能。

用于輸出使能的同步復位

這種同步技術的優點是能簡化復位–高阻這一路徑的時序分析。

異步復位(完全異步)

異步低復位

異步低復位的代碼如下:

modulereset_async( inputclk, inputrst_n, input[1:0]in, outputreg[1:0]out ); always@(posedgeclkornegedgerst_n)begin if(rst_n=='b0) out<=?'d0?; ????????else? ????????????out?<=?in?; ????end endmodule

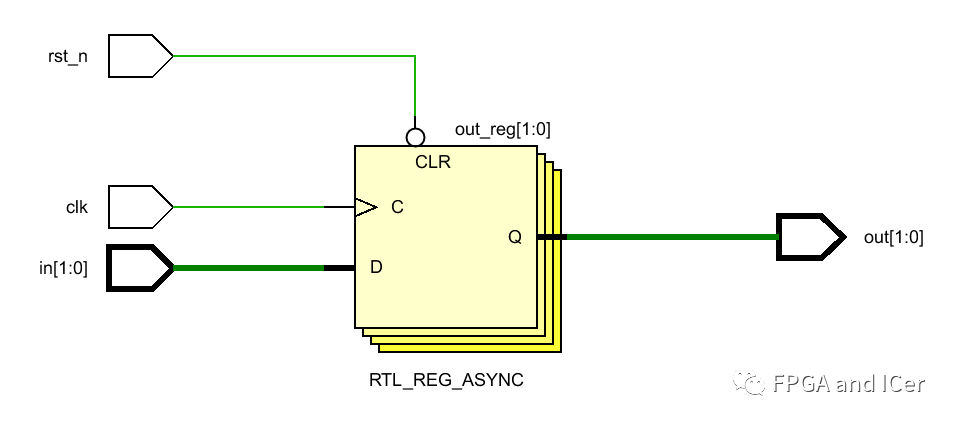

在使用vivado RTL 分析對應的電路結構如下:

RTL電路結構

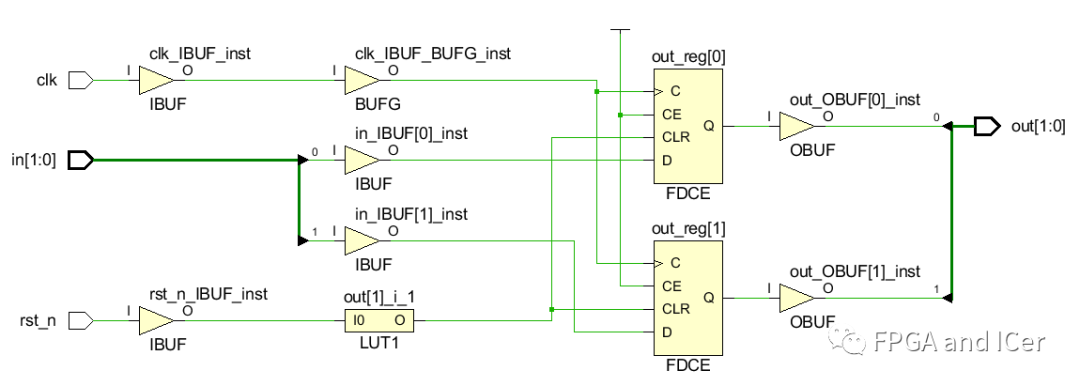

使用vivado綜合后結構如下:

由于xilinx的器件結構中的觸發器為高復位,所以會引入LUT實現復位信號的功能,引入額外的邏輯資源。

異步高復位

異步高復位的代碼如下:

modulereset_async( inputclk, inputrst, input[1:0]in, outputreg[1:0]out ); always@(posedgeclkorposedgerst)begin if(rst=='b1) out<=?'d0?; ????????else? ????????????out?<=?in?; ????end endmodule

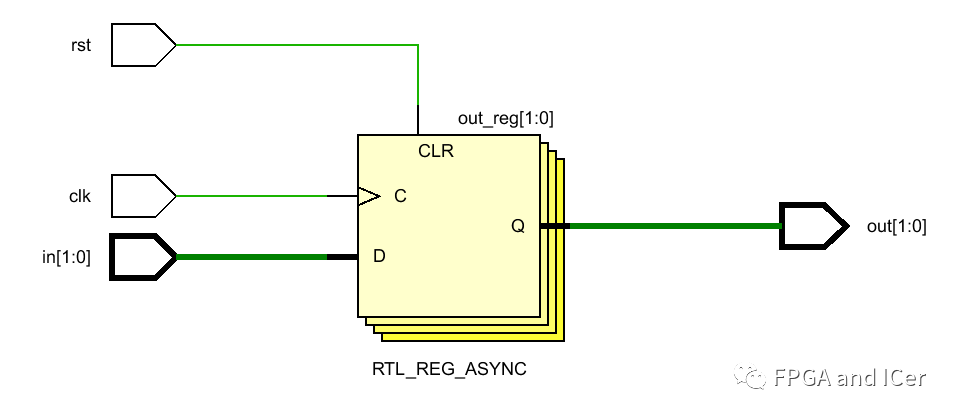

在使用vivado RTL 分析對應的電路結構如下:

使用vivado綜合后結構如下:

這里綜合后也沒有引入新的組合邏輯資源,在該層次看并沒有什么影響,「但是Xilinx FPGA綜合規則中:有和沒有異步復位的寄存器不能被包裝在一個Slice,不同異步復位的寄存器不能被包裝在一個Slice,這就導致在Slice中的資源無法充分利用從而造成資源浪費。」

異步復位的優缺點

「異步復位電路的優點:」

大多數目標器件庫的DFF都有異步復位端口,因此采用異步復位可以節省資源。

設計相對簡單,異步復位信號識別方便,而且可以很方便的使用FPGA的全局復位端口GSR。

「異步復位電路的缺點:」

所有異步信號的缺點也同時等效是異步復位信號的問題,復位信號從本質講就是一個頻繁使用的控制信號,因此可以總結其缺點如下。

復位信號容易受到毛刺的影響;

因為是異步邏輯,無法避免地存在亞穩態問題。

靜態定時分析比較困難,靜態時序分析一般是針對同步設計的,都是基于時鐘周期來分析時序的。

對于 DFT(可測性設計)設計,如果復位信號不是直接來自于 I/O 引腳,在 DFT 掃描 和測試時,復位信號必須被禁止,因此需要額外的同步電路。

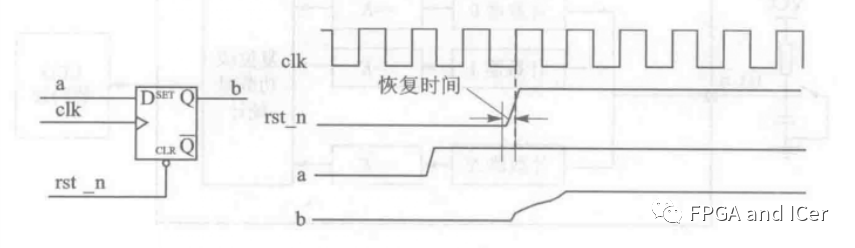

復位信號的“建立時間”與“保持時間”

由于復位信號實現了對D觸發器的控制(置位信號同理),所以但是本質上也是實現了控制相關物理電路進行開關實現置位或者復位,由于異步復位與系統時鐘毫無關系,不考慮其余因素時,異步復位可以在任意時刻撤除。但復位信號恰好在時鐘沿附近時,復位(置位)信號同樣也要滿足相應的“亞穩態窗口”的不能移除的需求,滿足寄存器的“建立時間”與“保持時間”。

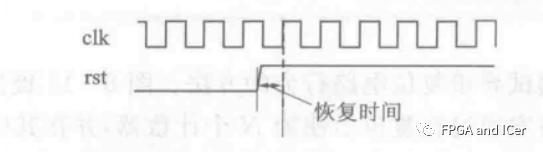

「恢復時間:」 如果復位信號在時鐘有效沿之前撤消,并且離時鐘有效沿非常接近,再加上時鐘有效沿到達各個觸發器有一定時間差(clock skew),那么極有可能一部份觸發器仍處于復位狀態中而對時鐘沿沒有響應,而一部份觸發器對時鐘有響應,那么從這一個時鐘開始,電路的狀態已經出錯了。

「移除時間:」 如果復位信號在時鐘有效沿之后撤消,并且離時鐘有效沿非常接近,再加上時鐘有效沿到達各個觸發器有一定時間差(clock skew),那么極有可能一部份觸發器從復位狀態中恢復并響應了時鐘,而一部份觸發器沒有響應,那么從這一個時鐘開始,電路的狀態已經出錯了。

下圖中異步復位信號有足夠的恢復時間,異步復位能正常釋放。

當異步復位信號在時鐘上升沿附近撤除時,導致觸發器的輸出為亞穩態,亞穩態前文已經討論過了,亞穩態在電路中的危害是顯而易見的。

恢復時間不足造成的亞穩態問題

如果你想讓某個時鐘沿起作用,那么你就應該在 “恢復時間” 之前是異步控制信號變無效;如果你想讓某個時鐘沿不起作用,那么你就應該在 “去除時間” 過后使控制信號變無效。

我覺得這里其實本質上就是要避開觸發器的建立時間和保持時間,避免在亞穩態窗口附近寄存器的雙鎖存結構和復位結構同時作用,這將會引入亞穩態。

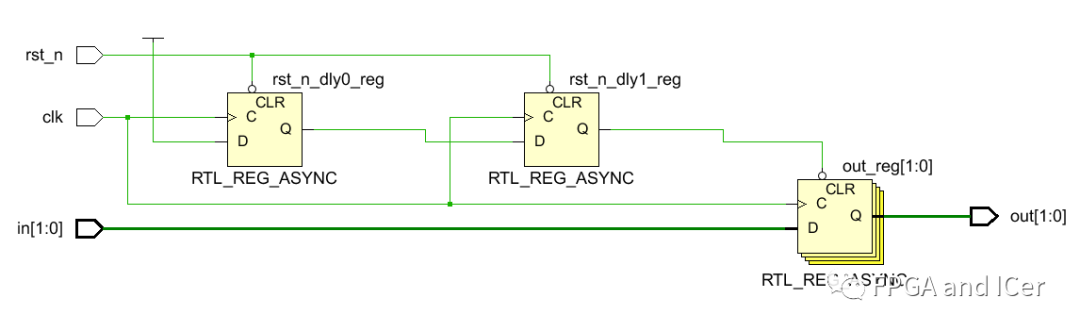

異步復位同步釋放

異步確立和同步釋放的復位電路通常會提供比完全異步或完全同步復位更可靠的復位。

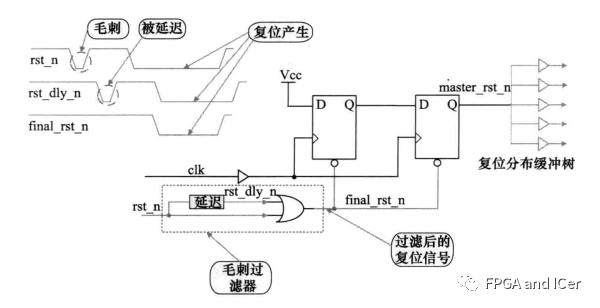

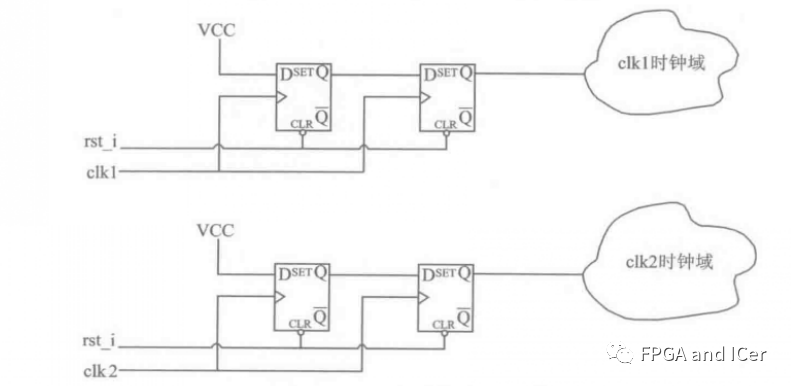

電路結構如下圖所示:

異步復位同步釋放電路結構

根據結構可寫出代碼如下:

modulereset_async_and_free_sync( inputclk, inputrst_n, input[1:0]in, outputreg[1:0]out ); regrst_n_dly0,rst_n_dly1; always@(posedgeclkornegedgerst_n)begin if(rst_n=='b0)begin rst_n_dly0<=?'d0?; ????????????rst_n_dly1?<=?'d0?; ????????end ????????else?begin ????????????rst_n_dly0?<=?'d1?; ????????????rst_n_dly1?<=?rst_n_dly0; ????????end ????end ????wire?rstn?=?rst_n_dly1; ????always?@?(posedge?clk?or?negedge?rstn)?begin ????????if?(rstn?==?'b0) ????????????out?<=?'d0?; ????????else? ????????????out?<=?in?; ????end endmodule

在使用vivado對應的電路結構如下:

使用vivado綜合后結構如下:

異步復位、同步釋放優點

異步復位、同步釋放具有異步復位和同步的優點,主要是:

快速復位。只要復位信號一有效,電路就處于復位狀態。

有效捕捉復位。即使是短脈寬復位也不會丟失。

有明確的復位撤銷行為。復位的撤離是同步信號,因此有良好的撤離時序和足夠的恢復時間。

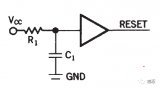

過濾復位毛刺

異步復位對毛刺很敏感,這就意味著任何滿足觸發器最小復位脈沖寬度的輸入都能引起觸發器復位。如果復位線受到毛刺的影響,這就真的成為問題了。在設計中,可能沒有足夠高頻的采樣時鐘來檢測復位上的小毛刺;下面將會介紹過濾掉毛刺的方法。該方法需要一個數字延時來過濾毛刺。復位輸入引腳也必須是施密特觸發器引腳才有助于毛刺過濾。下圖顯示了復位毛刺濾波器的電路和時序圖。

復位毛刺過濾

為了加人延時,一些生產商提供了用于延遲且能夠手動實例化的宏單元。如果沒有這樣的宏單元,設計人員就需要在優化后的已綜合設計中手動加入延時。第二種方法需要創建一個包含較慢緩沖器的模塊,再多次實例化該模塊以達到所期望的延遲。基于這種思想,可以產生許多變種的解決辦法。

由于該方法使用了延遲鏈,因此一個缺點是所產生的延遲會隨著溫度、電壓和工藝而變化。必須注意確保延遲在所有PVT環境下都能滿足設計要求。

不“復位” 可以嗎?

如果針對Xilinx FPGA的設計應用,我覺得不進行 “復位” 是可以的,不必要的數據信號可以不進行“復位”,這樣可以節省資源,在xilinx的白皮書中也是這樣建議的:

當一個Xilinx的FPGA芯片被重新配置時,每一個單元都將被初始化。在某種意義上講,這是一個上電之后的“終極的”全局復位操作,因為它不僅僅是對所有的觸發器進行了復位操作,還初始化了所有的RAM單元。隨著Xilinx FPGA芯片內部的嵌入式RAM資源越來越多,這種“終極的”全局復位操作越來越有意義。對所有的RAM單元進行預定義,在軟件仿真和實際操作中都是非常有幫助的,因為這樣避免了在上電時采用復雜的啟動順序來清除存儲單元內容的操作。

通常可以將設計分為兩部分,控制路徑和數據路徑

部分數據路徑的初始值并不重要,此時的重置是不必要的。

只在設計中需要獲得有效幀信號或設計回到已知良好狀態的部分使用外部復位。

雖然在這里提到了不進行復位,但是不得不注意的是Xilinx的FPGA在上電后會對芯片內的資源進行復位,所以即使相關寄存器不進行復位,在芯片上電后也是能知道恢復到了芯片設置的默認狀態的。在xilinx平臺,部分復位設計實際是沒有多大意義的。

無復位電路

編寫代碼使得輸入做一級寄存處理,然后再將寄存輸出的結果輸出給out寄存器,此時對out這個寄存器不做復位處理。編寫代碼如下:

modulenoreset( inputclk, inputrst_n, input[1:0]in, outputreg[1:0]out ); reg[1:0]in_r; always@(posedgeclk)begin if(rst_n=='b0)begin in_r<=?'d0?; ????????????//out?<=?'d0?; ????????end ????????else?begin ????????????in_r?<=?in; ????????????out?<=?in_r; ????????end ????end endmodule

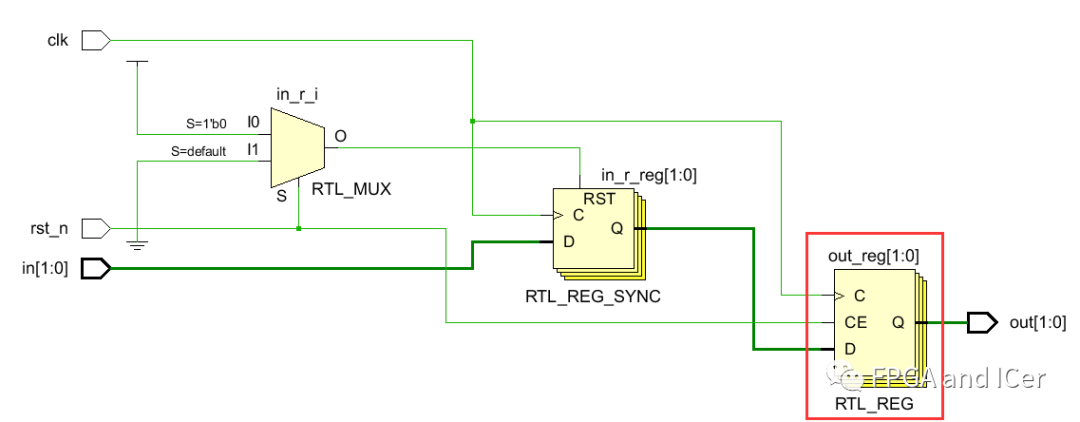

在使用vivado RTL分析后對應的電路結構如下,從結構圖中可以看到,第二級的輸出寄存器沒有添加相關復位信號控制邏輯資源。

使用vivado綜合后結構如下,對輸出寄存器沒有設置復位,在綜合分析時會自動設置復位信號為無效。

復位網絡

在一個設計中,無論是同步復位還是異步復位,其扇出數量往往僅次于時鐘網絡。復位網絡通常會被布線在全局網絡上,在布線的時候需要控制各個路徑的時鐘偏移保持在大致相等的水平上,使復位能“同時”撤離。

下圖為一個樹狀全局復位網絡。

樹狀全局復位網絡

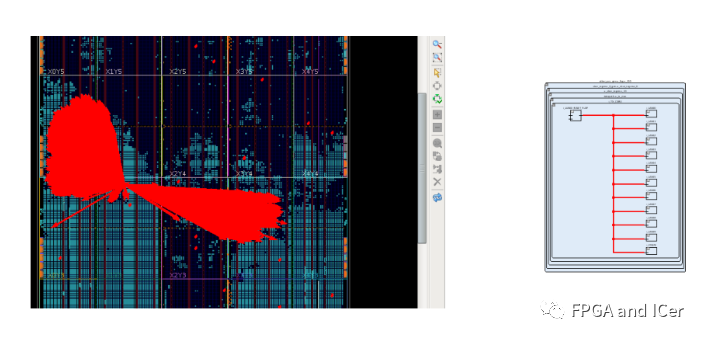

當復位信號驅動的模塊和信號過多時,會導致扇出過大,從而使得布局布線變得困難。下圖為一個全局復位網絡的例子,從圖中可以看出,復位信號扇出很大,資源分布散亂,從而給布局、布線帶來很大的困難,增加了EDA的編譯負擔。

復位網絡扇出過大

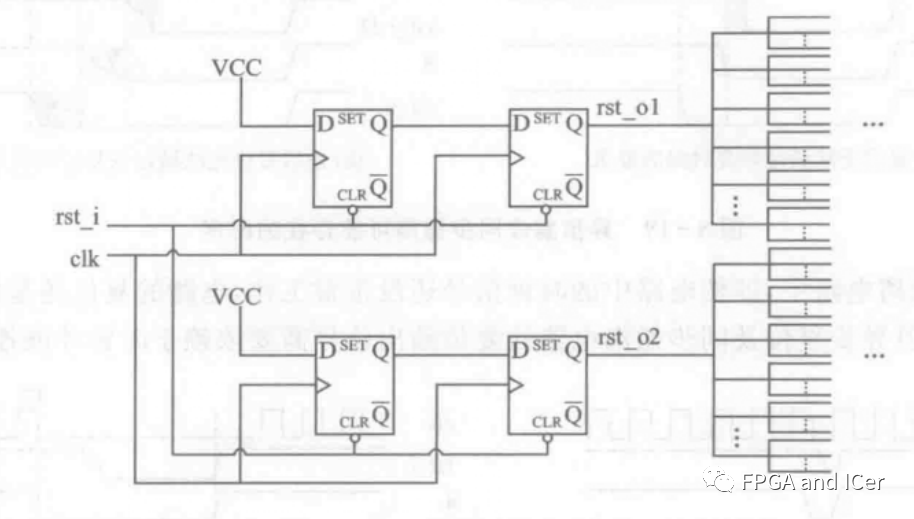

考慮下圖的復位方案也會存在,由于rst_ol和rst_o2在撤離時可能存在一個時鐘周期的偏差,因此,在實際電路系統中,該方式有可能導致復位失敗,與前文提到的亞穩態的多個同步器道理相同。

多個復位同步器網絡

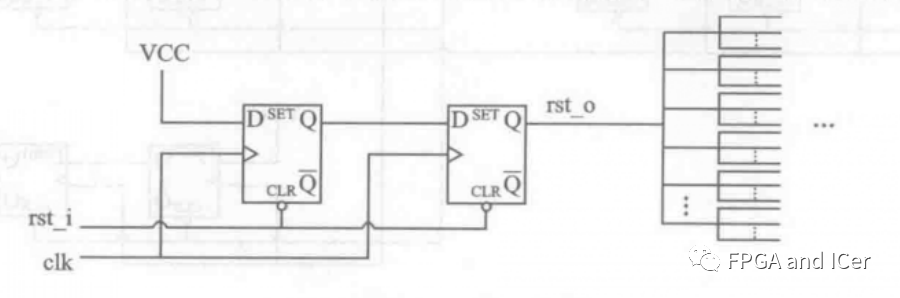

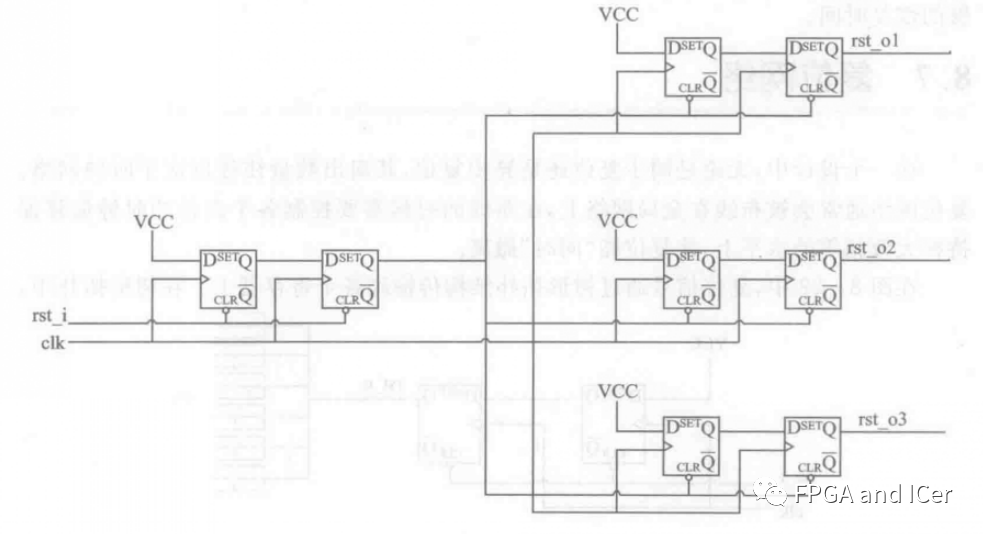

比較合理的設計如下圖:

模塊化復位同步網絡

圖中的復位電路首先用兩級寄存器對復位進行同步,得到根復位信號后再對其用復位同步器進行分發。由于同步后的根復位信號不會帶來亞穩態的問題,因此,在分發根復位信號時再次使用兩級寄存器對根復位信號進行同步和分發是很安全的。

根復位信號經過復位同步器分發后,各個子復位網絡是各自獨立的,并且扇出的數量比根復位網絡要小很多。在布局布線的時候,這些子復位網絡需要一一進行約束和時序分析。一般情況下,在設計的頂層代碼中劃分專門的復位模塊,由該模塊統一處理電路所需要的所有復位信號,使復位的方案更加清晰安全。在設計中,將復位電路的處理分散到各個底層模塊是不安全的,有可能導致不同模塊間的復位行為不一致,使電路因復位失敗而工作在異常的狀態上。

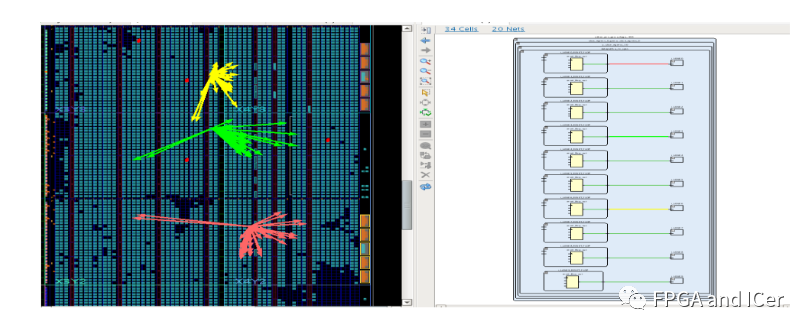

模塊化復位網絡

上圖為使用模塊化的復位的布局布線的結果,可以看到,復位信號經過模塊化的處理后,降低了扇出,更有利于提高電路的工作性能。

多時鐘域的復位

在多時鐘域電路中,合理的復位處理方式應如下圖所示。各個時鐘域的復位信號由各自的時鐘進行同步。在每個時鐘域內,電路總是能被正確地復位。

小結

本文分析了復位的用途,通過同步復位和異步復位兩個示例表示了在Xilinx FPGA中的不同復位的編寫方法綜合出的實際電路,指導我們在實際應用中去合理的進行復位設計,同時引入了恢復時間和去除時間的概念,進一步解釋了在復位時,復位信號和時鐘信號應該遵守的相關約定,進而結合異步復位的優點和同步復位的優點,介紹了異步復位同步釋放的復位設計方法,在最后介紹了合理的復位網絡設計與多時鐘域的復位設計。根據本文的分析,可以小結一下關于復位的相關操作的注意事項以及復位設計的小技巧:

異步確立和同步釋放的復位電路通常提供比完全異步或完全同步復位更可靠的復位。

復位電平的選擇跟芯片結構有關,根據具體使用的芯片屬性選擇合適的復位電平。

建議采用異步復位同步化(異步復位同步釋放處理)。

全局復位并不是最佳方式,可使用模塊化方式去處理復位信號。

并不是所有時序電路都要加復位,但對于控制信號以及必須知道初始狀態的情況,必要的復位是不可少的。

對每個獨立的時鐘區域必須利用一個分開的復位同步器。

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601809 -

驅動器

+關注

關注

52文章

8154瀏覽量

145999 -

反相器

+關注

關注

6文章

310瀏覽量

43243 -

Xilinx

+關注

關注

71文章

2163瀏覽量

121005 -

時鐘

+關注

關注

10文章

1720瀏覽量

131362 -

RTL

+關注

關注

1文章

385瀏覽量

59699 -

觸發器

+關注

關注

14文章

1995瀏覽量

61049 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

39780 -

復位信號

+關注

關注

0文章

53瀏覽量

6299

原文標題:數字設計小思 - 談談復位那些事

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

在FPGA開發中盡量避免全局復位的使用?(2)

FPGA的理想的復位方法和技巧

Xilinx FPGA的同步復位和異步復位

【PUC、POR】MSP430的復位信號

你真的會Xilinx FPGA的復位嗎?

復位信號是什么意思?復位信號的作用?詳解Xilinx FPGA復位信號那些事

復位信號是什么意思?復位信號的作用?詳解Xilinx FPGA復位信號那些事

評論