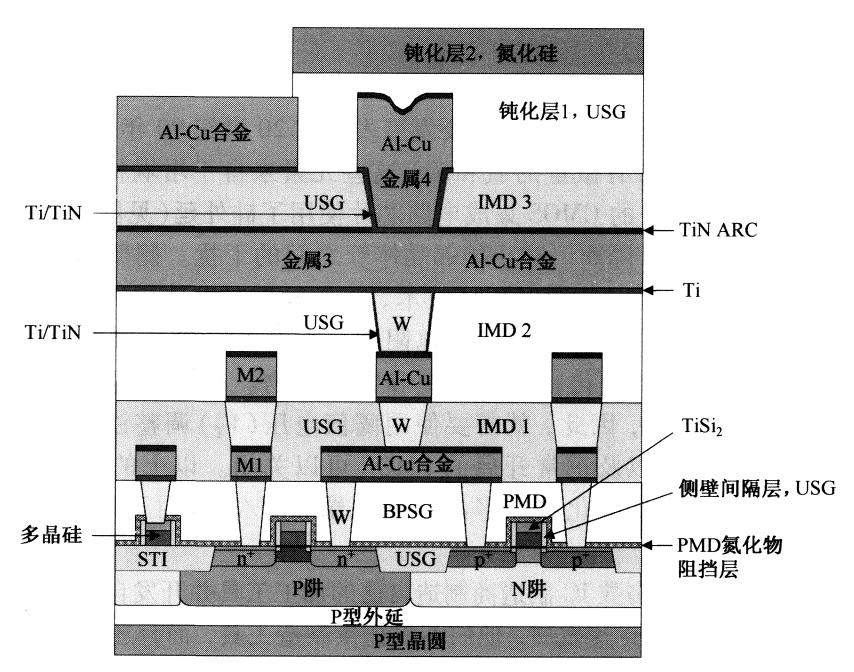

CMOS集成電路芯片加工技術的幾個主要發展發生在20世紀90年代。從CZ法單晶硅晶棒上切割下來的硅晶圓都含有微量的氧和碳,這些元素來自于坩堝材料。為了消除這些雜質并提高芯片的性能,先進的CMOS集成電路芯片使用了硅外延(見下圖)。淺溝槽隔離(見下圖)取代了LOCOS隔離以防止相鄰晶體管之間的干擾。側壁間隔層用于形成抑制亞微米器件熱電子效應的輕摻雜漏(LDD)技術,并形成自對準硅化物以減少柵極和局部連線的電阻。由于硅化物具有比多晶硅低的電阻率,所以可以提高器件的速度并降低功耗。20世紀90年代最常用的硅化物是硅化鈣和鈦硅化物。在此期間,IC芯片的電源電壓逐漸從12V降低到3.3V,因此,就需要使用閾值電壓調整注入過程,以確保正常關閉的NMOS可以打開,以及正常開啟的PMOS可以關閉。以上的工藝流程顯示了一個自對準硅化物工藝過程,鈦硅化物在多晶硅柵頂端和源/漏同時形成。源/漏硅化物降低了接觸電阻。

20世紀90年代以前,大多數IC制造商制造自己的加工工具并開發自己的IC工藝。半導體設備公司在20世紀90年代迅速發展,他們不僅提供制造工具,而且還給IC制造廠提供整合的工藝流程。能夠在同一主機下運行不同工藝的配套工具在IC產業界非常受歡迎。因為單晶圓處理系統有更好的晶圓對晶圓均勻性控制,所以被廣泛使用。而批處理系統具有較高的產量,所以現在仍然用在許多非關鍵性工藝中。

20世紀90年代,光刻技術的曝光波長從紫外光(UV)降低到248nm的深紫外光(DUV)范圍。因為負光刻膠無法將小于3um的線條圖形化,所以光刻中使用了正光刻膠。步進機取代了其他的對準和曝光系統,而整合的晶圓軌道機一步進機系統可以在一個工藝流程中執行光刻膠涂敷、烘烤、對準曝光以及顯影。所有的圖形刻蝕都是等離子體刻蝕過程,而濕法刻蝕仍然廣泛應用于整面全區薄膜去除、測試晶圓的刻蝕和清洗,以及CVD薄膜的質量控制工藝中。立式高溫爐因為占據更小的面積和更好的污染控制而成為主導。快速熱處理(RTP)系統因為有更好的熱積存控制而應用于離子注入后退火和金屬硅化物的形成工藝中。濺射取代了蒸發成為金屬沉積工藝的一種選擇,直流磁控濺射系統是現在最常見的金屬物理氣相沉積(BVD)系統。

由于晶體管的數量顯著增加,單層金屬已不再足以連接硅表面上的微電子元器件,因此使用了多層金屬互連。常用CVD鎢沉積填充狹窄的接觸窗和金屬層間接觸孔,并以栓塞的形式連接不同的導電層。鈦和氮化鈦被廣泛用于阻擋層和鎢的附著層。鈦也同時用于鋁銅合金的焊接層以減少接觸電阻,而且氮化鈦也成為抗反光薄膜(ARC)的一種選擇。

BPSG普遍用于金屬沉積前的電介質(PMD)。通過添加硼的硅酸鹽玻璃,玻璃化再流動溫度可以從約1100攝氏度降低到800攝氏度。這有助于減小熱積存,因為當特征尺寸縮小時,熱積存也必須減小。PE-TEOS和O3-TEOS工藝廣泛用于STI電介質CVD、側壁間隔層和互連。鎢栓塞工藝中,CMP工藝通常用于從晶圓表面移除大量的CVD鈞金屬層。CMP也廣泛用于硅玻璃表面的平坦化,以達到更好的光刻分辨率使后續的金屬沉積過程更容易。下圖顯示了20世紀90年代中期工藝技術制造的CMOSIC芯片橫截面示意圖。

審核編輯:劉清

-

半導體

+關注

關注

334文章

27026瀏覽量

216370 -

接觸電阻

+關注

關注

1文章

106瀏覽量

11909 -

LDD接口

+關注

關注

0文章

6瀏覽量

7435 -

CMOS芯片

+關注

關注

3文章

38瀏覽量

8411 -

DUV

+關注

關注

1文章

55瀏覽量

3680

原文標題:半導體行業(一百九十二)之ICT技術(二)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

仿真技術在半導體和集成電路生產流程優化中的應用

簡述半導體超純水設備工藝流程及標準參考分析

倒裝晶片的組裝工藝流程

半導體制造工藝流程及其需要的設備和材料

泛林集團自維護設備創半導體行業工藝流程生產率新紀錄

功率半導體分立器件工藝流程

半導體圖案化工藝流程之刻蝕(一)

半導體行業之ICT技術的工藝流程

半導體行業之ICT技術的工藝流程

評論