經過半導體制造(FAB)工序制備的電路圖形化晶圓容易受溫度變化、電擊、化學和物理性外部損傷等各種因素的影響。

為了彌補這些弱點,將芯片與晶圓分離后再進行包裝,這種方法被稱為“半導體封裝(Packaging)”。與半導體芯片一樣,封裝也朝著“輕、薄、短、小”的方向發展。但是,當將信號從芯片內部連接到封裝外部時,封裝不應起到阻礙作用。

封裝技術包括“內部結構(Internal Structure)技術”、“外部結構(External Structure)技術”和“表面安裝技術(Surface Mounting Technology,簡稱 SMT)”。

1. 封裝發展趨勢

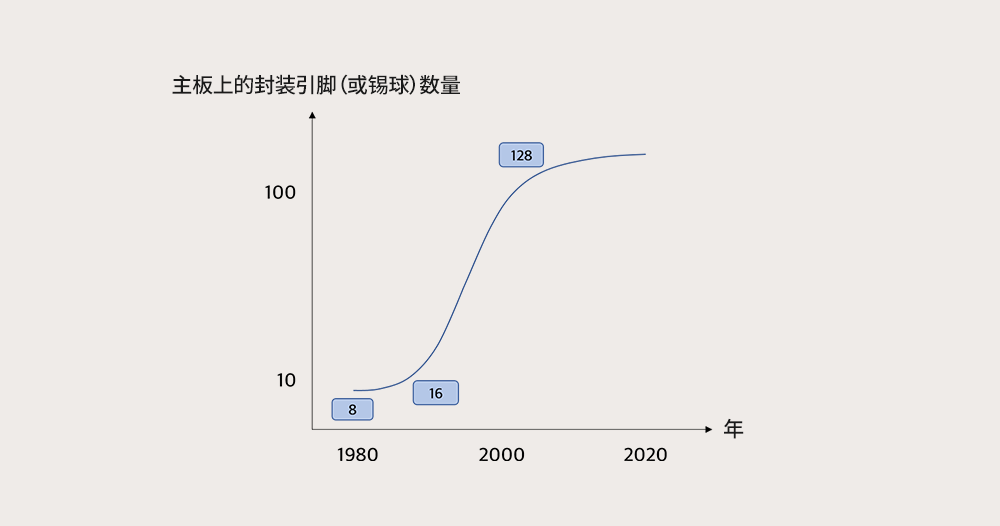

<圖1>焊接在主板上的半導體封裝引腳(或錫球)數量的變化

開發新的半導體封裝,首先必須改變封裝在主板上的安裝方式和外部形式。其次,還要改變封裝的內部結構和材料。當封裝結構越復雜時,焊接在主板上的引腳(Pin)或錫球(Ball)數量就越多,引腳間距就越小。目前,封裝與主板之間的接點數量已迅速接近其極限與飽和點。

2. 封裝結構

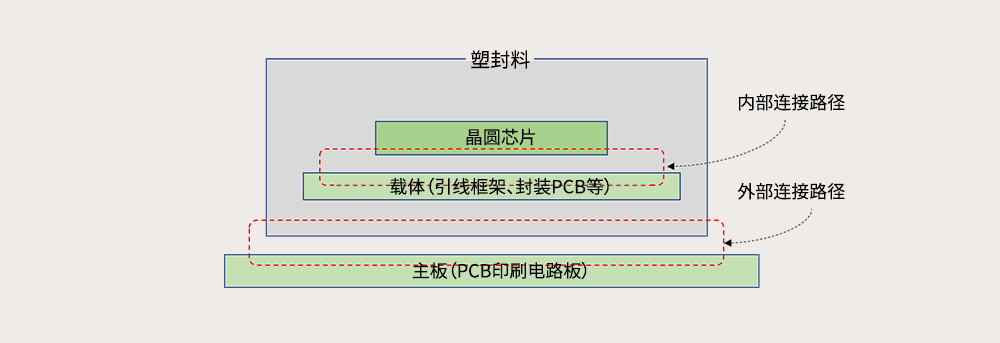

<圖2>半導體封裝的內部和外部結構

半導體封裝包括半導體芯片、裝載芯片的載體(封裝PCB、引線框架等)和封裝這些器件的塑封料。

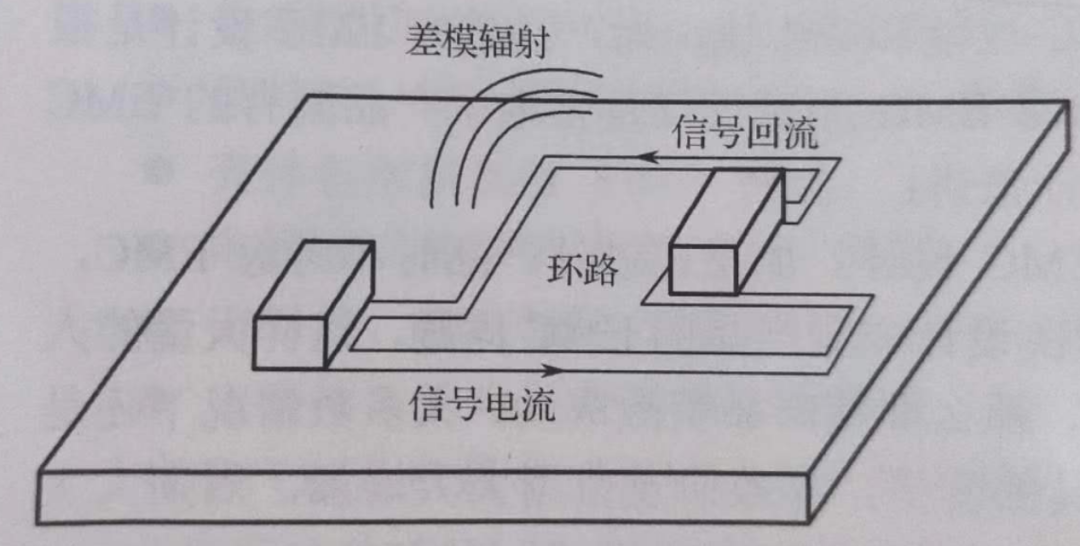

此外,內部和外部連接路徑用于將信號從內部芯片連接到外部。無論是內部還是外部連接,該連接過去都是使用線(導線或引線框架)進行的,但近來普遍使用點(緩沖墊或錫球)。同時,塑封料在排除內部熱量和保護芯片免受外部損傷方面起著重要作用。

3. 決定封裝類型的三要素:內部結構、外部結構和貼裝

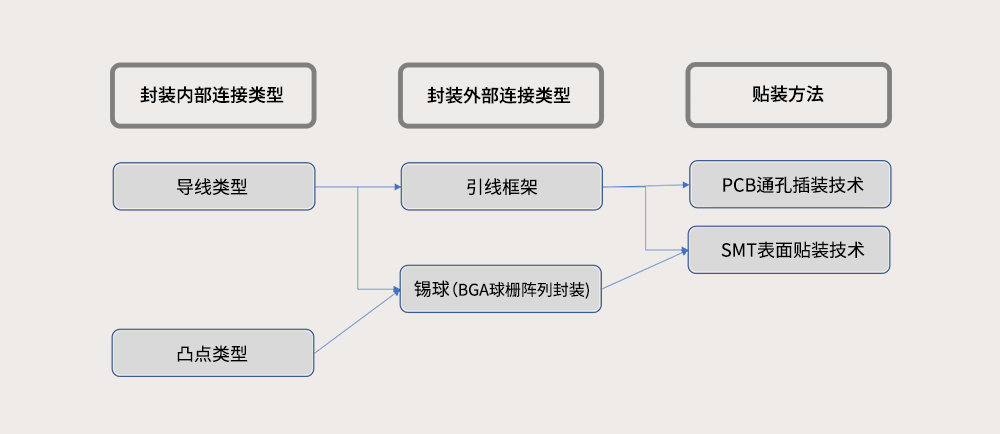

<圖3>封裝內部連接類型、外部連接類型和貼裝方法的示意圖

直到上世紀80年代末,普遍采用的封裝內部連接方式是引線鍵合(Wire Bonding),即用金線將芯片焊盤連接到載體焊盤。然而,隨著封裝尺寸減小,封裝內金屬線所占體積也就隨之增大。為了解決這個問題,沒有拆除金屬線,而是用凸點(Bump)代替金屬線進行內部連接。當然,這并不意味著引線鍵合方法完全不可用。

當使用凸點連接時,需要采用凸點連接(Bump Attaching)工藝和環氧樹脂填充(Under-Fill)方法代替裝片(Die-Attaching)和引線鍵合工藝。 外部連接方式也已從引線框架改為錫球。這是因為引線框架和導線有同樣的缺點。過去采用的是“導線-引線框架-PCB通孔插裝”,而現在最常用的是“凸點-球柵陣列(Ball Grid Array, 簡稱 BGA)-表面貼裝技術”

4. 內部封裝類型

4.1 無引腳半導體(Wireless Semiconductor):倒裝芯片(Flip chip)

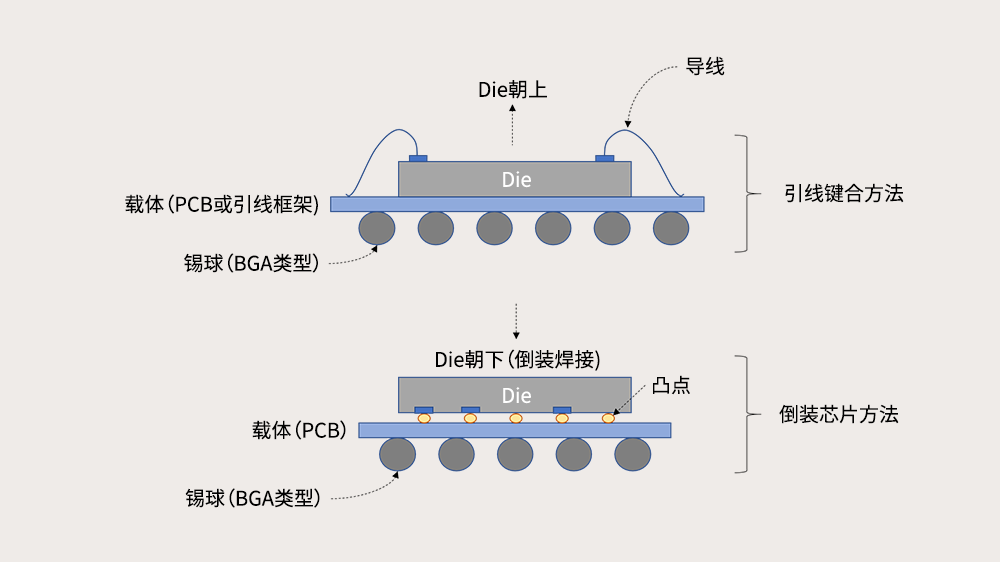

<圖4>引線鍵合類型和倒裝芯片類型之比較

半導體封裝還可以根據內部結構分成引線類型(Wiring Type)與倒裝芯片類型(Flip Chip Type)。引線方法將芯片朝上,通過引線鍵合與載體連接起來。而倒裝芯片方法是將芯片朝下,并把直徑極小的錫球(被稱為凸點Bump的導電金屬)連接到焊盤上。

因此,倒裝芯片方法不需要用長的導線,即可使半導體芯片連接于基板上,具有信號傳輸距離短、粘附力強的特性。這可以說是一項改善引線鍵合缺陷的創新技術。 倒裝芯片最大的優點是能減少封裝尺寸,改進功耗和信號傳輸過程。由于其長度較短,受到電阻和周邊噪音的影響較小,所以速度更快。

因此,凸點材料使用哪種金屬也很重要。目前最常見的是焊料或黃金。倒裝芯片的另外一個關鍵點在于用哪種環氧樹脂來填充凸點和載體之間的空隙。此外,倒裝芯片不使用占用大面積的導線,可以減小成形后的芯片尺寸,因此它被廣泛應用于手機等小型電子設備。

也就是說,隨著封裝在主板上的焊墊(Footprint)面積的減小,它更多地被應用于高密度基板技術上。智能手機等小型電子設備的出現,給封裝技術帶來了重大轉變。

4.2 在芯片之間制作垂直導通孔的三維封裝技術:硅通孔(Through Silicon Via,簡稱 TSV)

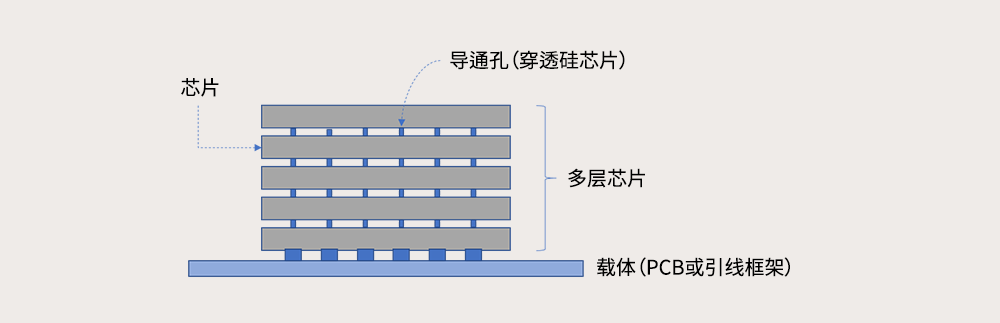

<圖5>采用穿透硅芯片的導通孔的三維封裝技術

為提高芯片封裝的密度,我們采用堆疊多個半導體芯片的多層封裝。晶圓級的多芯片封裝方式有引線鍵合(Wire Bonding)和硅通孔(TSV)兩種方式。硅通孔是堆疊芯片之后,在芯片鉆出垂直通孔并通過硅貫通電極連接信號線。其優勢在于信號傳輸速度快,封裝密度高。

與處理單個芯片的二維封裝技術相比,硅通孔(TSV)可以被視為三維封裝技術。如果用導線連接多層芯片,則形成階梯堆疊結構,面積會增加約兩倍。但硅通孔(TSV)可以像公寓樓一樣形成垂直堆疊結構,只需要大約1.2倍的芯片面積。由于硅通孔(TSV)技術具有更高的空間使用效率,應用范圍正逐漸擴大。

5. 外部封裝類型和貼裝方法 – 基于封裝與外部連接的方式

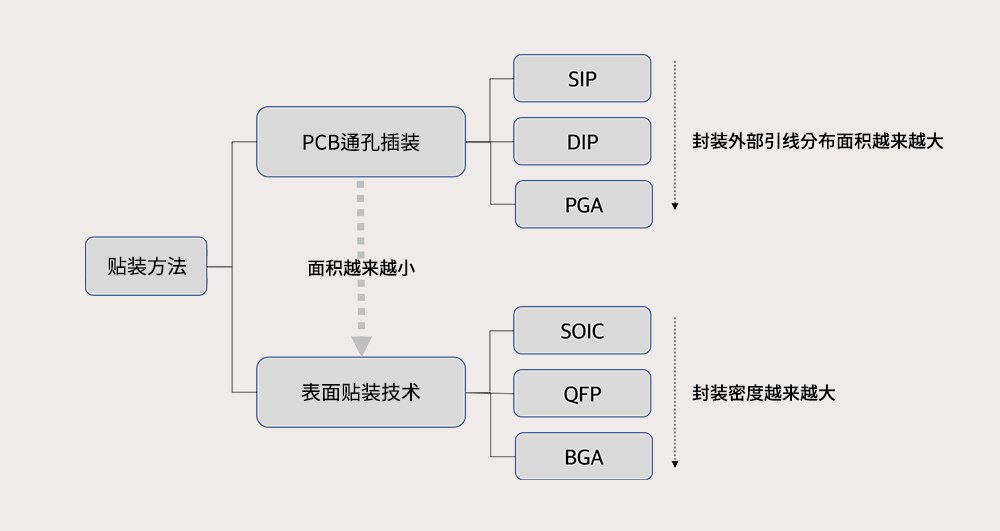

<圖6>外部封裝類型和貼裝方法

5.1 外部封裝類型

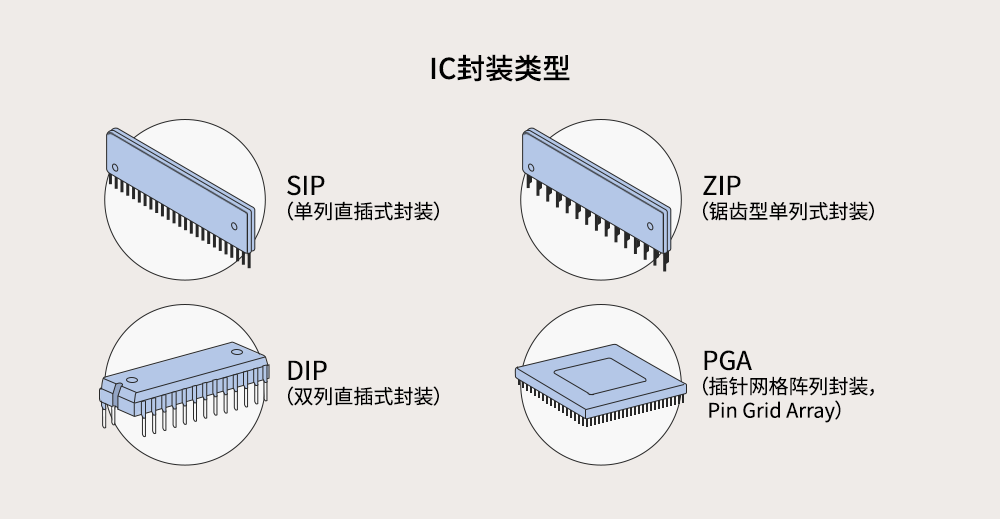

<圖7>IC封裝類型

封裝芯片種類多樣。以引線框架類型為例,有適用于PCB通孔插裝的浸漬式(Dipping),其開發順序為SIP1、ZIP2、DIP3和PGA4。然而,由于其減少占用主板焊墊面積的能力極其有限,目前僅在某些情況下使用。 在引線框架類型中還有一種小外形(Small Outline,簡稱 SO)封裝技術它屬于表面貼裝技術,通過彎曲引線來提高集成度。

目前已發展到SOIC和SOJ(J型引腳小外形封裝)并得到廣泛應用。除此之外,方型扁平式封裝(Quad Flat Package,簡稱 QFP)被用于CPU芯片上。隨后,封裝技術從引線框架類型變為球形,逐漸派生出球形觸點陣列(BGA)。目前,球形已成主流。

5.2 貼裝方法

封裝組裝方法主要分為表面貼裝技術(SMT)和PCB通孔插裝技術。顧名思義,表面貼裝技術(SMT)就是通過焊接將芯片固定在主板表面上,而PCB通孔插裝技術是將芯片引腳插入主板相應的安裝孔,然后與主板的焊盤焊接固定。 然而,由于主板上的安裝孔所占面積太大,為實現“輕薄短小”的封裝,貼裝方法已發展成為無孔表面貼裝技術。

在引線框架方法中,從一開始就開發了SO型(SOIC和SOJ)和TSOP用于表面安裝。BGA類型的球本身就是用于安裝在主板上的,因此也適用表面貼裝方法。

審核編輯:劉清

-

連接器

+關注

關注

98文章

14317瀏覽量

136163 -

芯片設計

+關注

關注

15文章

1001瀏覽量

54812 -

smt

+關注

關注

40文章

2883瀏覽量

69058 -

半導體封裝

+關注

關注

4文章

253瀏覽量

13724 -

PCB走線

+關注

關注

3文章

133瀏覽量

13902

原文標題:半導體封裝三要素:內部結構、外部結構、SMT

文章出處:【微信號:閃德半導體,微信公眾號:閃德半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式系統的三要素

單片機工作基礎三要素

力的三要素是什么?什么是力?

凹槽型光耦選型三要素

決定半導體封裝類型的三要素

決定半導體封裝類型的三要素

評論