這篇文章簡要介紹CEA-Leti發布用于Chiplet 3D系統的硅光Interposer工藝架構,包括硅光前端工藝 (FEOL)、TSV middle工藝、后端工藝 (BEOL) 和背面工藝。

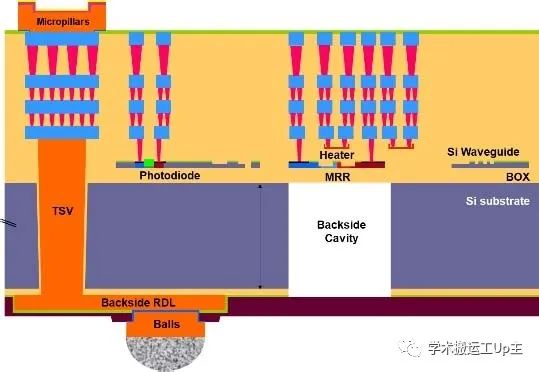

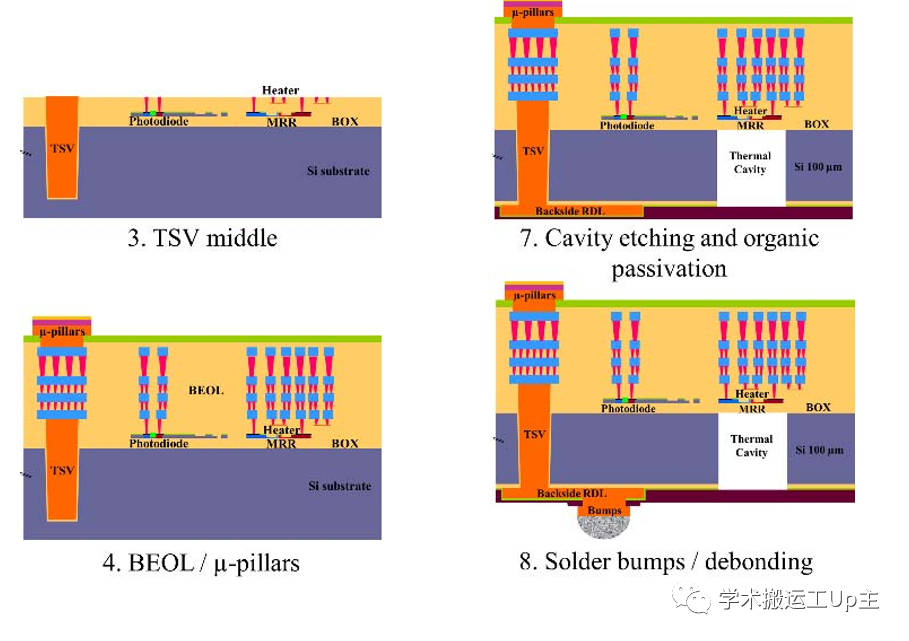

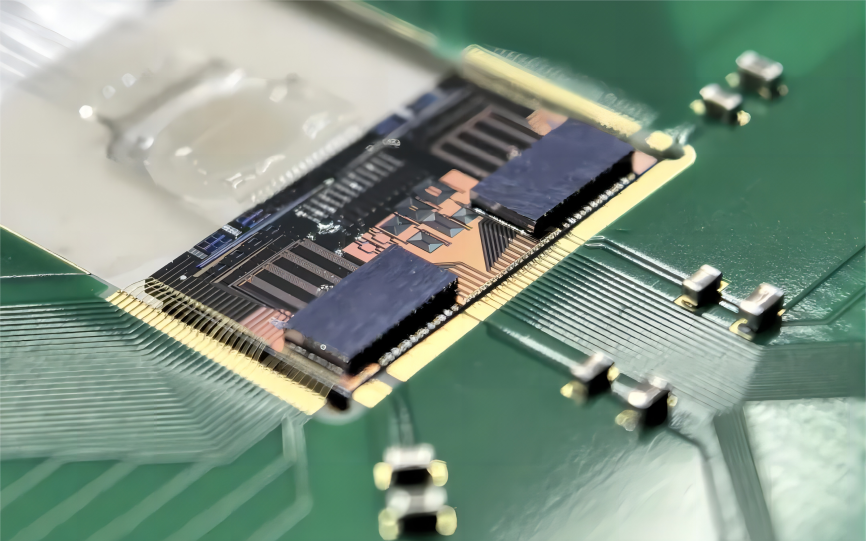

下圖展示了Interposer的技術橫截面,其中包括μ-pillars、BEOL層、有源光子器件、背面空腔、TSV、RDL 和焊球。

1. 硅光前端工藝

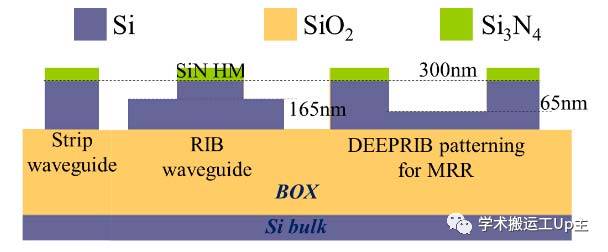

硅光子器件是在 CEA-LETI 的 200mm 工藝平臺在絕緣體上硅 (SOI) 晶圓上制造的。該晶圓有 800nm 厚的埋層氧化物 (BOX)/頂部具有 310nm 厚的硅層。制造從各種注入步驟開始,主要用于定義 MRR 的 PN 和 PIN 結以及 MRR 和光電二極管的電氣接觸。然后使用 Si3N4 硬掩模對硅光波導進行圖案化。采用3級DUV光刻(193nm和248nm)定義3種硅的厚度,獲得波導走線和單偏振光柵耦合器(SPGC),共有300nm厚波導和165nm厚Rib-slab波導,以及具有300nm厚環形波導和65nm 厚的深刻蝕波導。下圖展示了硅光子器件的不同硅厚度。

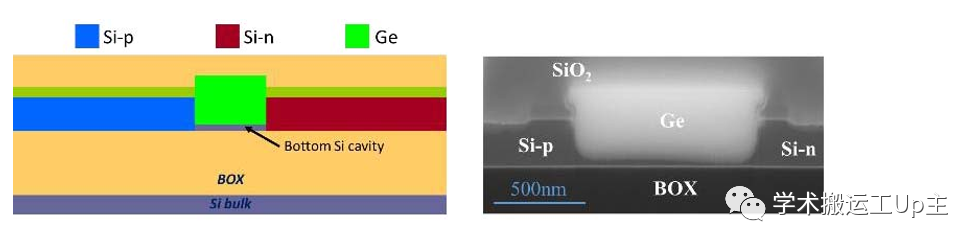

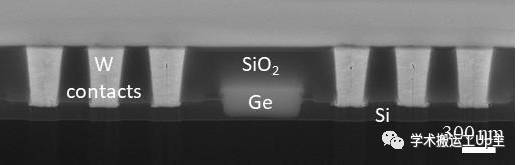

在硅圖案化之后,在 MRR 的slab層中進行了額外的離子注入以增強調制性能。在對硅結構進行高密度等離子體化學氣相沉積 (HDP-CVD) SiO2 包層并平坦化之后,使用 SiO2/Si3N4 電介質疊層作為硬掩模,通過在硅中形成空腔圖案來制造butt 耦合的 SiGeSi 光電探測器。對硅中的空腔進行部分蝕刻并進行表面處理后,通過使用兩步減壓化學氣相沉積 (RPCVD) 工藝進行選擇性外延,在硅上生長鍺。通過 CMP 去除多余的Ge并停在 SiO2 頂面。然后沉積一層 SiO2 以覆蓋 Ge 光電探測器。下面顯示了所得 Ge 光電探測器的示意性橫截面,并顯示了 SiO2 覆蓋后 Ge 光電探測器的 FIB 橫截面圖像。

為了增強有源光子器件上的電接觸,在定義為 MRR 和Ge PD的電接觸的高摻雜硅區域的表面進行硅化(Silicidation)。將電介質疊層蝕刻至摻雜硅,并通過在硅上沉積薄的 Ti/TiN 疊層并隨后進行熱退火來形成 TiSi2 硅化物。濕法去除未反應的 Ti/TiN 后,進行第二次熱退火以穩定 20nm 硅化物層。然后在 300 nm 厚的硅光子結構上沉積并平坦化 600nm 厚的厚 SiO2 層。

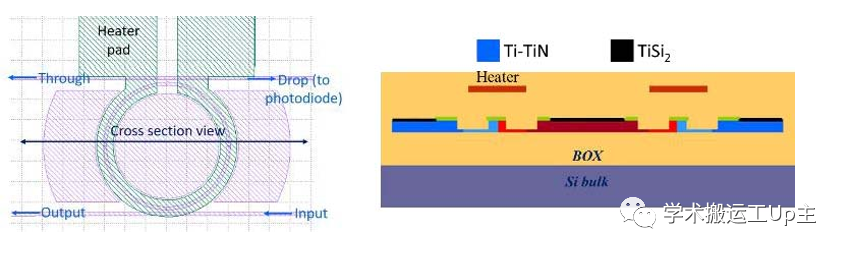

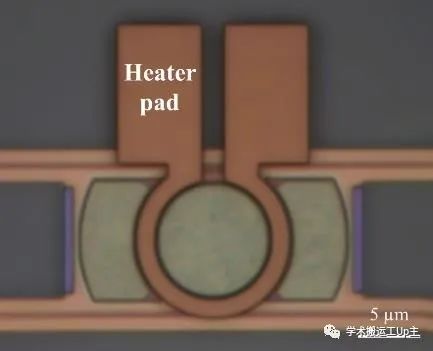

MRR 諧振頻率通過使用 MRR 波導頂部的加熱器heater進行控制,如下面的 MRR 設計和示意性橫截面所示。

通過沉積 Ti 10nm/TiN 100nm 疊層來制造heater,并通過干法蝕刻進行圖案化。下圖顯示了 MRR 頂部heater的顯微鏡圖片。

加熱器heater由 300nm 厚的平坦化 SiO2 層封裝。首先,對加熱器頂部 300nm 厚的 SiO2 層中的加熱器觸點進行干法蝕刻開始金屬觸點。然后,通過同時對 MRR 和Ge PD接觸點進行處理,將電介質疊層蝕刻至硅光子器件頂部的 TiSi2 硅化物層。一步沉積鎢以填充heater、PD 和 MRR 觸點。通過 CMP 去除多余的 W。帶有 W 觸點的 Ge PD的橫截面圖如下所示。

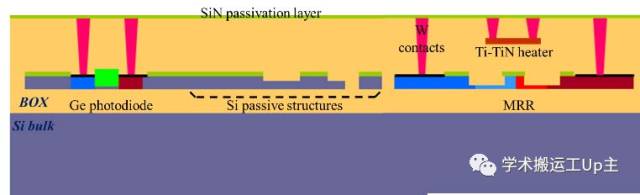

在 TSV 工藝之前沉積 60nm PECVD SiN 鈍化層。下面給出了接觸定義和鈍化后完整光子集成電路 (PIC) 的示意性橫截面。

2.TSV middle工藝

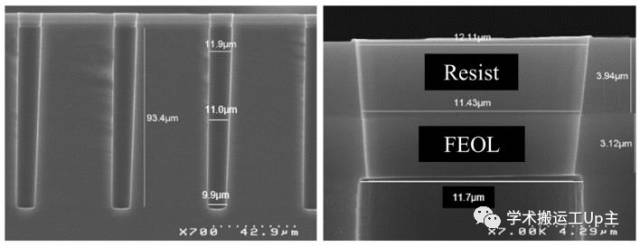

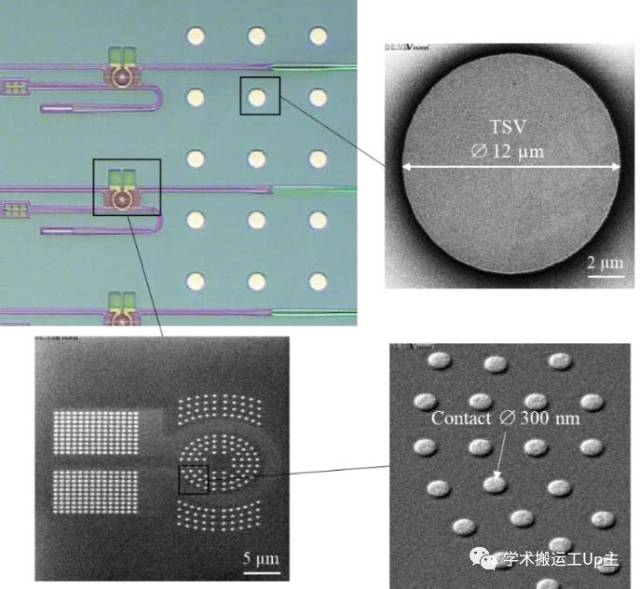

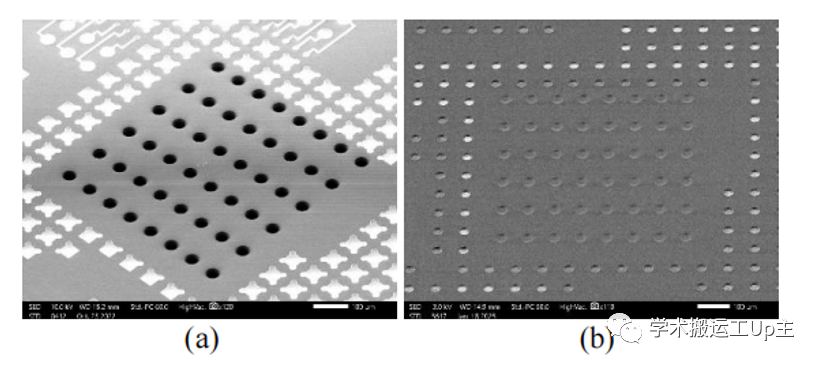

Interposer選擇的TSV工藝是直徑為12μm、厚度為100μm的TSV middle工藝。TSV蝕刻分兩步進行。首先,采用反應離子刻蝕(RIE)工藝刻蝕介質光子疊層(SiN/SiO2)。其次,使用Bosch工藝的深反應離子蝕刻(DRIE)通過圖案化光刻膠對硅進行蝕刻,如下所示。

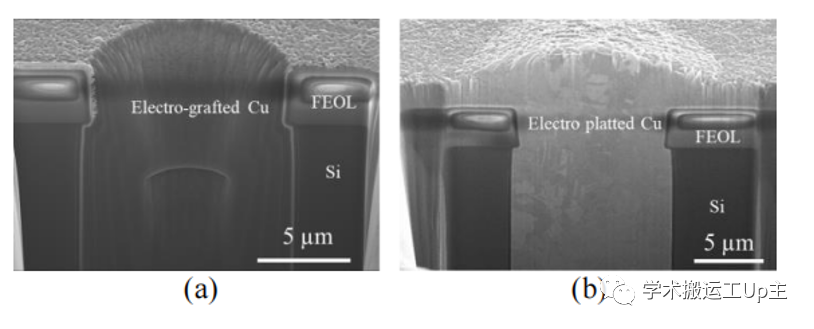

TSV 隔離是通過 300nm 低于大氣壓化學氣相沉積 (SACVD) 和 100nm 等離子體增強 CVD (PECVD) 氧化硅實現的。然后沉積阻擋層和種子層。沉積順序包括 Ti PVD 粘附層、TiN CVD 阻擋層和 Cu PVD 種子層。由于 Cu PVD 工藝的共形性受到限制,因此鍍了額外的電接枝銅層,以確保穿過 TSV 的籽晶連續性,如下所示(a)。TSV 填充采用 Cu 電化學沉積 (ECD) 進行,并采用優化的自下而上填充配方。這允許用低于 3μm 的剩余銅表面厚度填充 TSV,如下所示(b)。

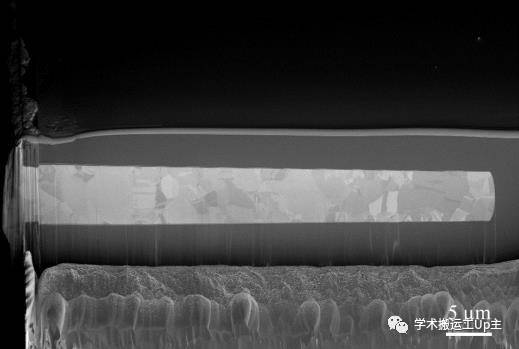

然后,TSV 在 400°C 下以特定的熱曲線進行退火,以最大程度地減少如下所示的 Cu 應力, 如下圖熱退火后的圖像。

最后的工藝是化學機械拋光(CMP)的兩步。第一步專用于在 TSV 隔離氧化硅層上選擇性蝕刻停止的 Cu 和阻擋層。第二步致力于在 300nm 直徑的 W 觸點上刻蝕停止的電介質 SiO2/SiN 層。此步驟具有挑戰性,主要是因為 CMP 工藝期間存在 TSV Cu 開口,如下所示。

3. BEOL工藝

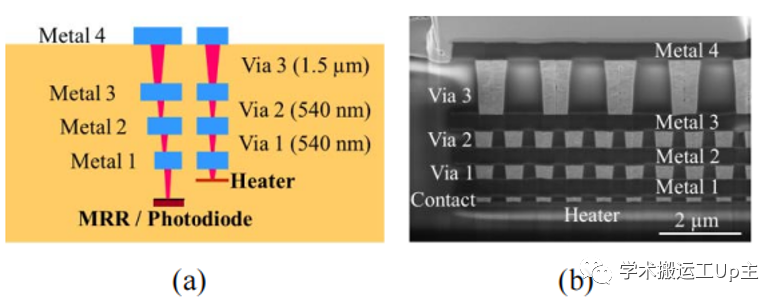

BEOL 疊層由 4 層金屬布線組成。如圖a所示,前3層相同,由PVD沉積的540nm Ti-TiN/AlCu/Ti-TiN多層金屬疊層制成,并由PECVD SiO2中間層隔開。每個介電層均采用 CMP 工藝進行平坦化。在 SiO2 金屬間層中通過 RIE 形成 300nm 寬度的方形接觸圖案,填充 W 并平坦化。第四金屬層的厚度與第 3 個金屬層的厚度相同,但通孔 3 的層間厚度增加到 1.5 μm,用于射頻功能目的。因此,接觸尺寸也增加到 750 nm 寬的方形接觸。完整 BEOL 的橫截面 FIB-SEM 圖像顯示在圖b中。

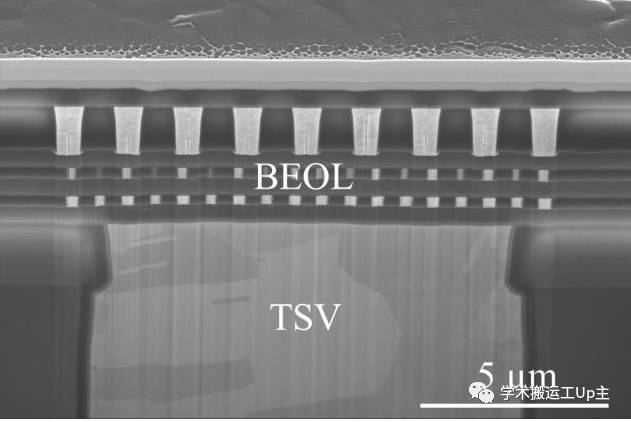

最終鈍化采用平坦化 500nm SiO2 PECVD 和 600nm SiN PECVD 進行。Pad open采用正光刻膠完成,電介質疊層采用 RIE 工藝蝕刻,下圖中FIB SEM顯示TSV middle工藝及BEOL的4層金屬線。

最終鈍化采用平坦化 500nm SiO2 PECVD 和 600nm SiN PECVD 進行。Pad open采用正光刻膠完成,電介質疊層采用 RIE 工藝蝕刻,下圖中FIB SEM顯示TSV middle工藝及BEOL的4層金屬線。

4.μ-pillars工藝

最后一個晶圓正面的工藝是μ-pillars工藝。首先,通過PVD分別沉積100nm和400nm的Ti/Cu種子層。光刻采用 12μm 厚的正光刻膠、臨界尺寸 (CD) 為 20μm、節距為 20μm 來實現。μ柱通過電鍍5μm Cu、2μm Ni和0.3μm Au來生長。然后strip光刻膠并通過濕法蝕刻去除種子層。

5. 背面工藝

1)晶圓減薄、Cu釘顯露

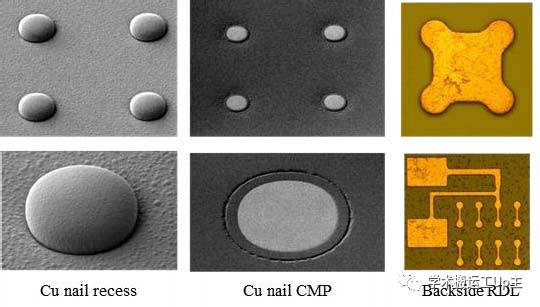

為了處理晶圓背面,使用 20μm 厚的粘合劑聚合物在 725μm 體硅carrier上進行臨時鍵合。通過粗磨和精磨來實現Interposer晶圓的減薄。濕法硅應力釋放最終將厚度降低至(110±1)μm。通過紅外干涉測量法監測 TSV 上方的殘余硅厚度。采用 SF6 RIE 工藝顯露銅釘,厚度范圍為 3 至 6μm。采用PECVD沉積2μm厚的低溫氧化硅。最后,進行 CMP 工藝以去除電介質并打開 TSV 的 Cu。

2)背面RDL、腔體蝕刻和鈍化

在正光刻膠 RDL 線/間距 10/10 μm 光刻之前,通過 PVD 工藝沉積由 100nm Ti 和 200nm Cu 組成的種子層。經過 O2 等離子體處理后,通過 ECD 電鍍 3μm 厚的 Cu,并對種子層進行濕法蝕刻,如下所示。

通過 PECVD 沉積 100nm 的低溫 SiN 層,以避免鈍化中的 Cu 擴散并在等離子體步驟中對其進行保護。然后在環形諧振器上方從體硅到 BOX 蝕刻直徑為 40μm 的空腔。使用掩模對準光刻技術在 RDL 上形成 8μm 厚的低溫固化 (LTC) 鈍化聚合物圖案,并在 N2 氣氛下在 230°C 下退火 3 小時。需開發專用旋涂工藝來覆蓋空腔。下圖中的SEM顯示旋涂有機鈍化層的RDL和空腔前后對比圖(a旋涂前/b旋涂后)

3) 焊錫凸塊和脫粘(Solder bumps & debonding)

首先,在LTC鈍化層上沉積Ti 200nm/Cu 400nm種子層。旋涂正光刻膠以達到40μm的厚度。光刻是通過具有40μm凸塊直徑和40μm間距的掩模對準器完成的。凸塊通過 5μm Cu、2μm Ni 和 17μm SnAg 的 ECD 生長。然后strip 光刻膠并蝕刻種子層。

最后將晶圓在切割膠帶上裂解開,進行清潔以去除粘合劑殘留物,并為封裝過程做好準備。

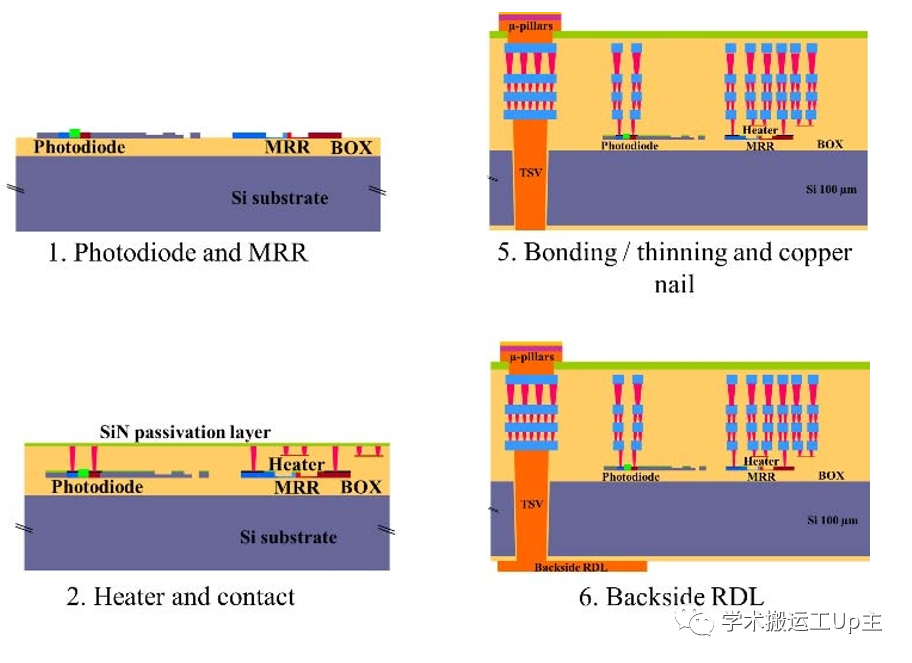

**下圖顯示CEA-LEti的Interposer工藝架構流程圖

審核編輯:劉清

-

耦合器

+關注

關注

8文章

710瀏覽量

59473 -

光刻機

+關注

關注

31文章

1136瀏覽量

46904 -

硅光子技術

+關注

關注

0文章

15瀏覽量

6220 -

TSV封裝

+關注

關注

0文章

12瀏覽量

2344 -

chiplet

+關注

關注

6文章

404瀏覽量

12513

原文標題:CEA-Leti 硅光工藝集成-Chiplet/Interposer

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

制造業革命——3D打印的主流工藝盤點

3D掃描的結構光

3D混合制造技術介紹

芯片的3D化歷程

使用結構光的3D掃描介紹

3D封裝與硅通孔(TSV)工藝技術

用于Chiplet 3D系統的硅光Interposer工藝架構介紹

用于Chiplet 3D系統的硅光Interposer工藝架構介紹

評論