編寫 HDL 通常是 FPGA 開發中耗時最少的部分,最具挑戰性和最耗時的部分可能是驗證。根據最終應用程序,驗證可能非常簡單,也可能非常復雜,簡單的話只需對大多數功能進行檢查或執行完全獨立開發的測試平臺來演示功能和代碼覆蓋率。

功能和代碼覆蓋率在驗證中很重要,因為它們都提供有關設計及其驗證的不同方面的信息。理想情況下,我們希望兩者都能達到 100%。僅其中一項達到 100% 表明我們還有進一步驗證要做。

以下是兩者的常見定義:

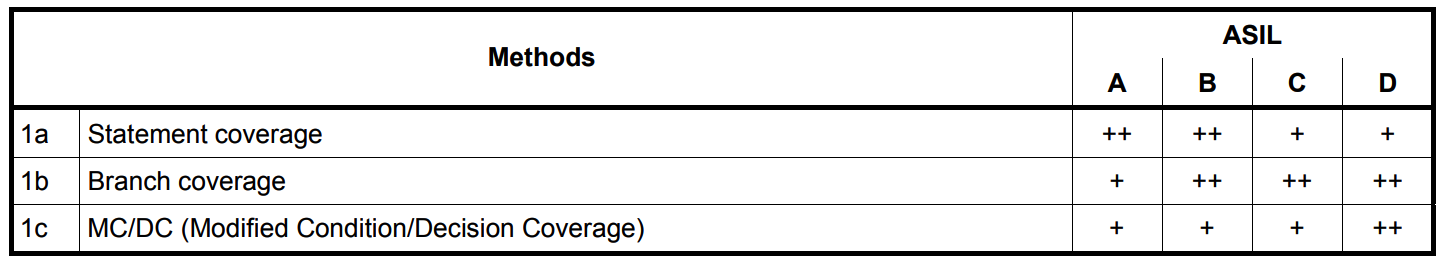

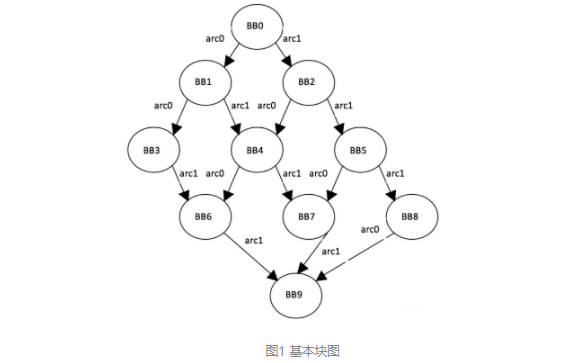

代碼覆蓋率——是一種通過計算測試過程中被執行的源代碼占全部源代碼的比例,進而間接度量軟件質量的方法。例如,它可以指示是否遍歷所有分支和語句(如果切換了所有觸發器)。

功能覆蓋率 – 提供有關測試平臺覆蓋被測單元功能行為的程度的信息。為了實現這一點,開發人員/驗證工程師必須定義覆蓋組和覆蓋點。

代碼覆蓋率和功能覆蓋率之間的區別在于,功能覆蓋率需要使用需求。

當然,代碼和功能覆蓋率都需要規劃代碼設計。代碼覆蓋率可能有一些限制,因為它無法識別缺失的功能,也無法識別是否已解決所有可能的邊界/極端情況值。代碼覆蓋率也不關心事件的順序。這就是功能覆蓋發揮作用的地方,因為它可以測試功能聲明。

通常,代碼和功能覆蓋率需要昂貴的仿真工具,但是,通過 Vivado 2021.1 的 Vivado 仿真器就可以實現。使用 Vivado 時,開發人員能夠驗證其設計并確保 RTL 功能符合要求。

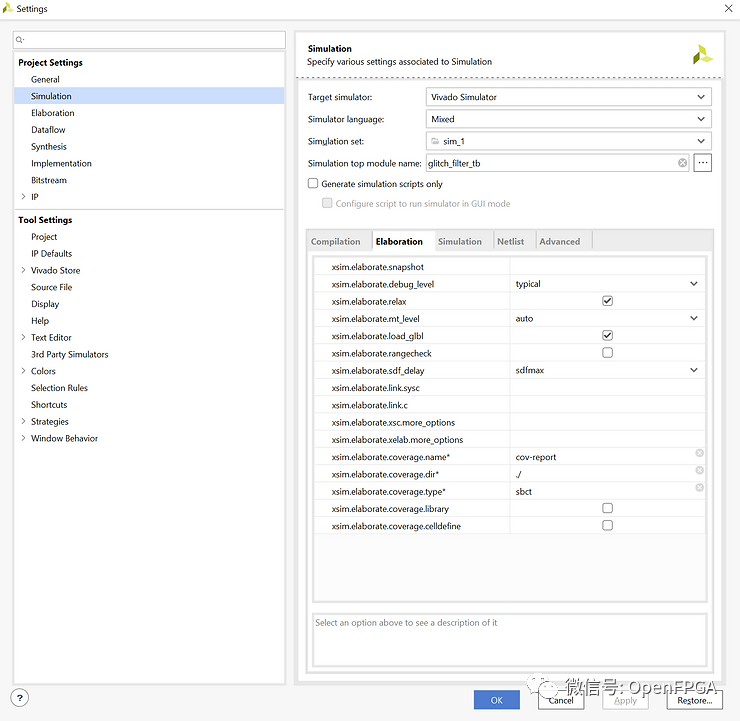

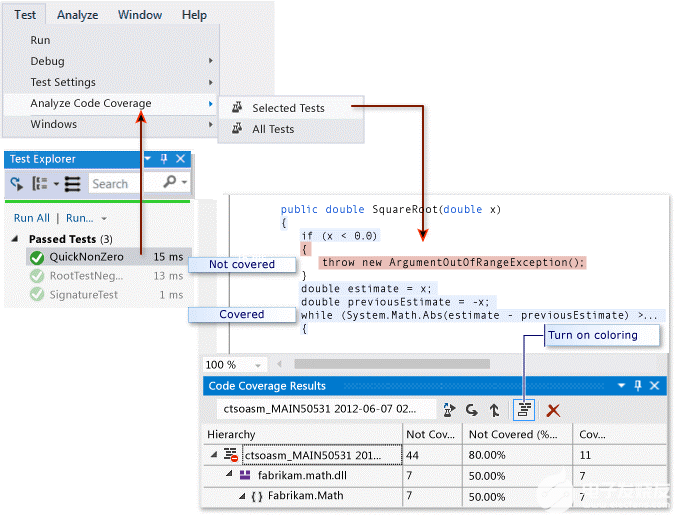

對于代碼覆蓋率,我們需要在項目設置中的“仿真”選項卡和細化設置下做的第一件事就是設置覆蓋類型。在Vivado中我們可以設置以下選項:

Line / Statement (s) 行/語句

Branch (b) 分支

Condition (c) 條件

Toggle (t) 切換

我們還可以定義覆蓋率報告名稱和覆蓋率目錄的位置。

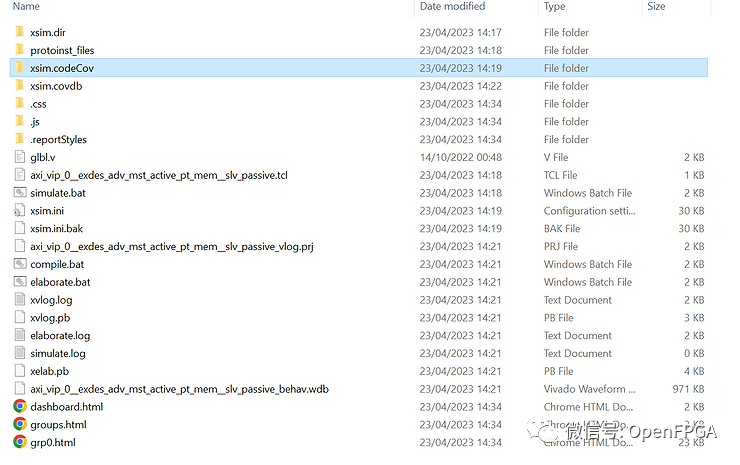

運行仿真結束時生成覆蓋信息。將能夠在elaboration設置中指定的位置看到 codeCov 目錄。

為了創建功能覆蓋,我們需要在 RTL 內創建覆蓋組。

這是獲取報告的數據庫。我們需要在 Vivado 中進行更多處理,將數據庫轉換為報告。

如果想了解 Vivado 仿真器的功能和代碼覆蓋率,最好的起點是UG937 Vivado 設計套件教程:邏輯仿真。

這提供了幾個設計示例,可用于測試 Vivado 仿真器功能的不同方面,包括代碼/功能覆蓋范圍以及 UVM 支持。

功能和代碼覆蓋率示例基于 AXI VIP 參考設計。完成本教程并添加覆蓋組將提供功能和代碼覆蓋率。

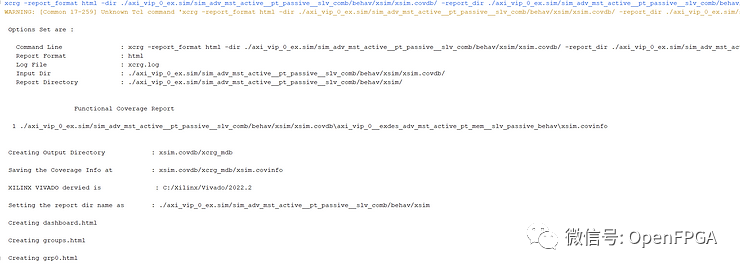

仿真完成后,我們需要運行 xcrg 命令來創建 HTML 報告。

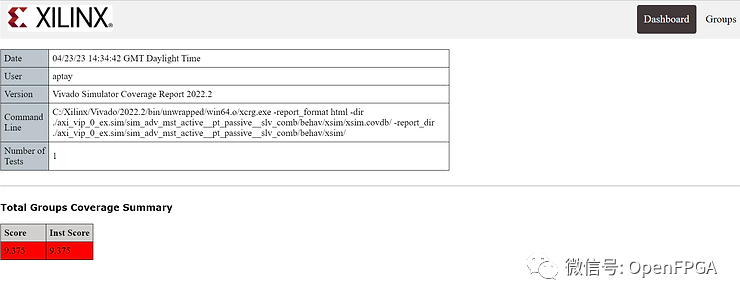

生成的 HTML 報告可以在任何瀏覽器中打開

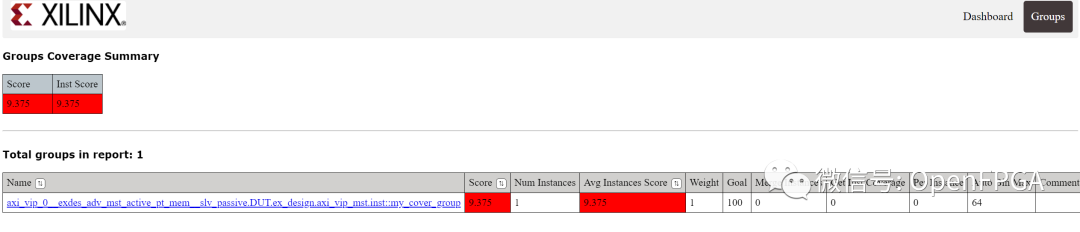

單擊組按鈕將打開有關覆蓋范圍組的詳細信息,在本示例中這比較簡單。

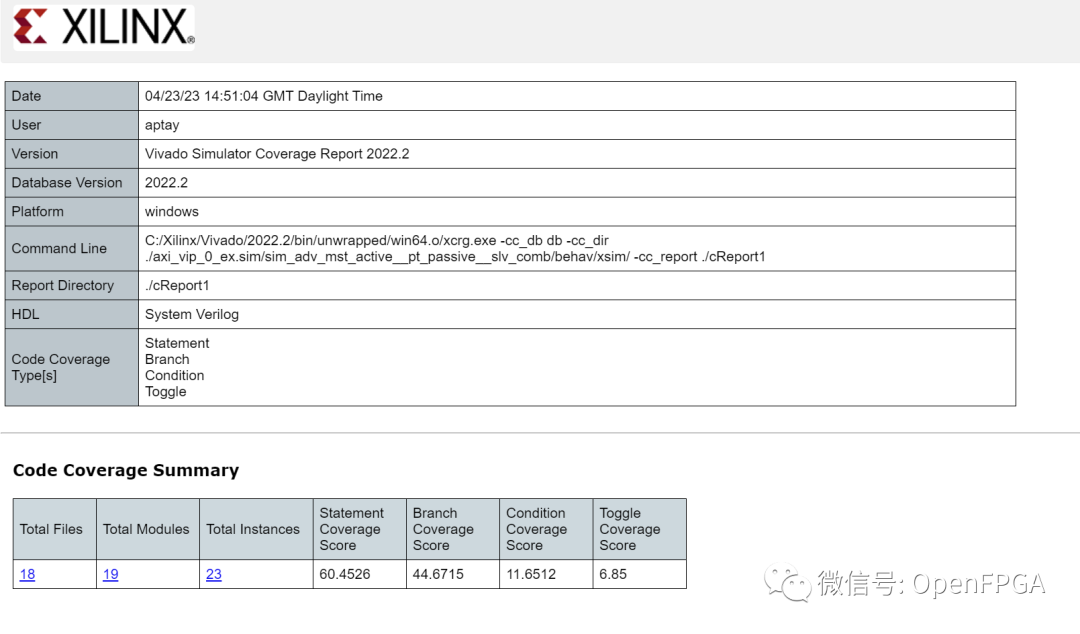

運行代碼覆蓋率轉換,可以看到生成的代碼覆蓋率報告。

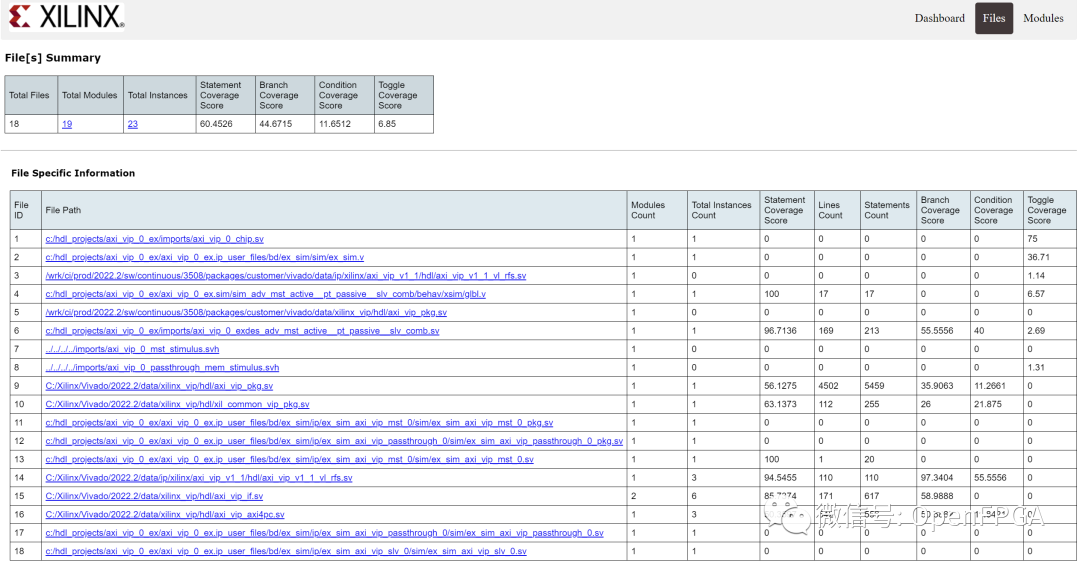

單擊右上角文件將顯示每個文件的結果。

總而言之,Vivado 仿真器的功能還是比較強大的。使用這些功能將幫助開發人員創建最佳設計,并有望減少調試硬件所花費的時間。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1016瀏覽量

83632 -

RTL

+關注

關注

1文章

385瀏覽量

59699 -

Vivado

+關注

關注

19文章

808瀏覽量

66323 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31484 -

HDL語言

+關注

關注

0文章

46瀏覽量

8909

原文標題:【Vivado那些事兒】Vivado 仿真器和代碼覆蓋率

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解Modelsim代碼覆蓋率功能使用

關于SpinalHDL中的驗證覆蓋率收集簡單說明

重點厘清覆蓋率相關的概念以及在芯片開發流程中跟覆蓋率相關的事項

Verilog代碼覆蓋率檢查

怎么才能寫出高覆蓋率的Verilog代碼?

高覆蓋率的Verilog代碼的編寫技巧

更好地測量代碼覆蓋率的 9 個技巧

代碼覆蓋率工具的重要性

代碼覆蓋率記錄

Vivado仿真器和代碼覆蓋率簡析

Vivado仿真器和代碼覆蓋率簡析

評論