誤碼儀的使用方法

誤碼儀(Error Code Monitor)是一種用于檢測和識別數據傳輸中發生的錯誤的測試設備。下面是一般誤碼儀的使用方法:

1. 連接設備:將誤碼儀與需要進行測試的數據傳輸設備(例如路由器、交換機等)進行連接。確保連接正確并穩定。

2. 配置測試參數:根據需要的測試目的和要求,配置誤碼儀的測試參數。例如,可以設置特定的傳輸速率、數據包大小和傳輸模式等。

3. 啟動測試:啟動誤碼儀的測試功能,開始發送測試數據包到被測設備。根據配置的參數,誤碼儀會模擬發送各種數據傳輸情況,包括正常傳輸和出現錯誤的情況。

4. 監測和記錄結果:誤碼儀會監測傳輸過程中的錯誤情況,并記錄錯誤碼和其他相關的統計信息。可以在誤碼儀上查看實時結果,也可以將結果保存到外部設備或計算機上進行分析和后續處理。

5. 分析和解釋結果:根據誤碼儀記錄的結果,可以進行錯誤分析和解釋。例如,可以確定出現錯誤的具體原因和位置,評估傳輸的質量和可靠性。

6. 調整和改進:根據測試結果,可以對數據傳輸設備進行調整和改進。例如,優化網絡設置、更換故障組件等,以提高數據傳輸的性能和可靠性。

基于FPGA的誤碼儀設計案例

本文設計的誤碼儀由兩部分組成:發信機和接收機。

1 發信機

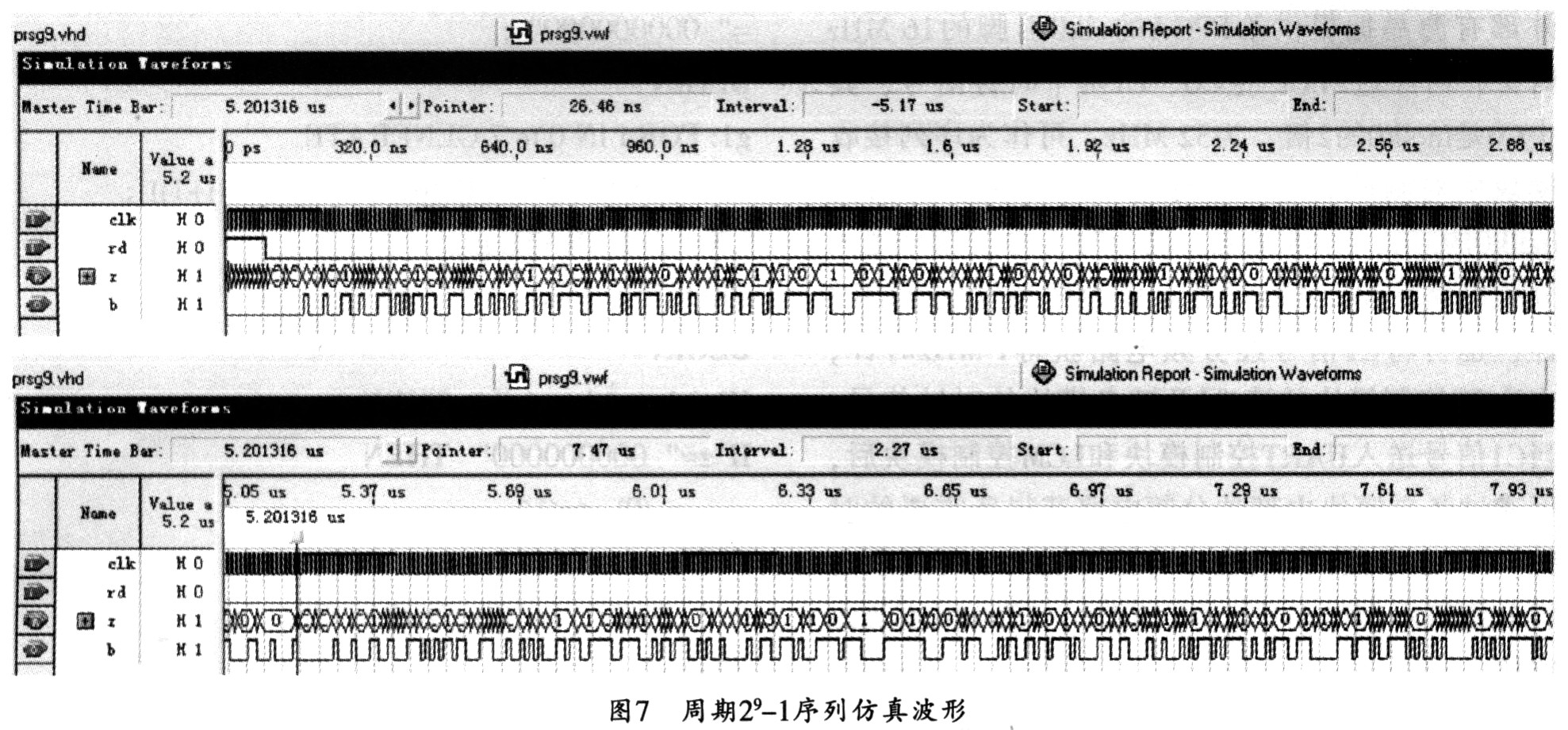

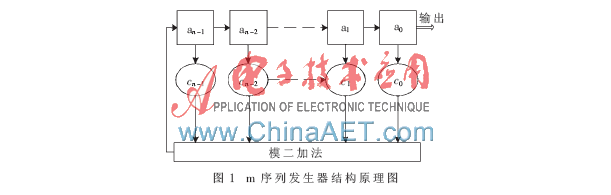

發信機的主要功能是產生具有隨機特性的偽隨機m 序列,通過FPGA 由VHDL 編程實現。偽隨機序列產生原理如下:

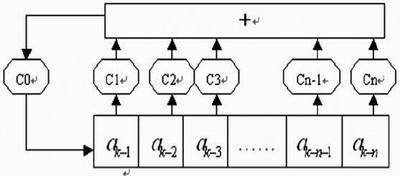

圖1 偽隨機序列產生原理圖

其中,ak-i是各移位寄存器的狀態,Ci對應各寄存器的反饋系數,為1表示參與反饋,為0不參與反饋。反饋函數為:

當級數n 和反饋系數一旦確定,則反饋移位寄存器的輸出序列確定了,m序列的一個重要的性質是:任一m序列的循環移位仍是一個m序列,序列長度為m = 2n-1 。

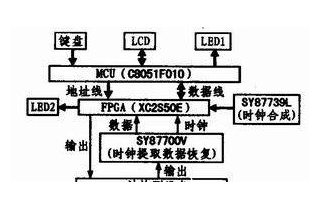

2 接收機

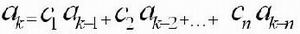

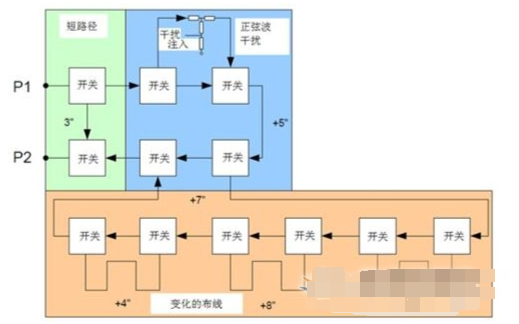

接收機主要由時鐘同步模塊、狀態同步模塊組成,其功能框圖如圖2 所示。

圖2 誤碼器接收機功能框圖

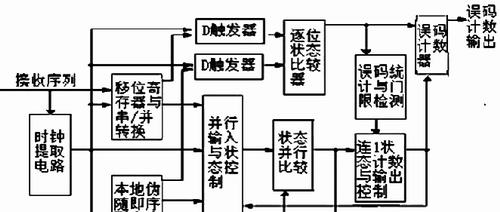

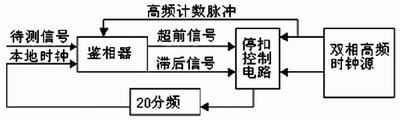

2.1 時鐘提取模塊

本單元所采用的時鐘提取方法是采用新的積分鑒相來實現的,通過在一個時鐘周期內對碼元進行積分,判斷超前滯后,從而極大

的降低了因干擾信號的出現導致誤調的可能性。

時鐘提取的原理圖如下:

圖3 時鐘提取原理圖

誤碼儀的測試原理

誤碼儀通過模擬發送和接收數據來進行測試,其測試原理如下:

1. 數據生成:誤碼儀根據配置的參數生成用于測試的數據信號。這些數據通常是經過編碼和調制處理的數字信號,模擬真實的數據傳輸。

2. 誤碼注入:誤碼儀將生成的數據信號注入到被測設備的輸入端口。這樣,誤碼儀就可以模擬真實環境中的數據傳輸。

3. 錯誤模擬:誤碼儀會在注入的數據信號中引入各種錯誤,以模擬傳輸過程中可能發生的錯誤情況。這些錯誤可以是比特錯誤、幀錯誤、丟包、延遲等。

4. 錯誤檢測:被測設備接收到誤碼儀注入的數據信號后,會根據接收到的數據進行錯誤檢測。被測設備會對接收到的數據進行解碼和校驗,以確定是否存在錯誤。

5. 錯誤統計:誤碼儀會統計和記錄被測設備接收到的錯誤情況,包括錯誤碼、錯誤類型、錯誤發生的位置等。這些統計信息可以用于分析和評估數據傳輸質量。

6. 分析和解釋:根據收集到的錯誤統計信息,可以對數據傳輸進行分析和解釋。可以確定錯誤的原因和位置,進而優化網絡設置或其他相關參數,提高數據傳輸的可靠性和性能。

誤碼儀的測試原理是通過模擬和引入錯誤情況,檢測和評估設備在真實環境中的數據傳輸質量和可靠性。不同的誤碼儀可能具有不同的測試原理和實現方式。

編輯:黃飛

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602024 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

數據傳輸

+關注

關注

9文章

1853瀏覽量

64499 -

誤碼儀

+關注

關注

0文章

12瀏覽量

10580

發布評論請先 登錄

相關推薦

求一種基于FPGA的誤碼率測試儀的方案

基于FPGA的誤碼率測試儀的設計與實現

一種基于FPGA的誤碼性能測試方案

基于FPGA的2M誤碼測試儀設計

基于FPGA的新型誤碼測試儀的設計與實現

基于FPGA的高速誤碼測試儀的設計

應用于光互連的高速誤碼儀的設計

一種基于FPGA的新型誤碼測試儀的設計與實現

以FPGA為核心的高速誤碼測試儀設計流程概述

誤碼儀的使用方法 基于FPGA的誤碼儀設計案例

誤碼儀的使用方法 基于FPGA的誤碼儀設計案例

評論