在過去的半個世紀中,我們開始將摩爾定律(即給定硅面積中的晶體管數量大約每兩年翻一番,推動計算向前發展)視為剛剛發生的事情,就好像它是自然發生的一樣。

一個自然的、不可避免的過程,類似于進化或衰老。當然,現實卻大不相同。跟上摩爾定律的步伐需要花費幾乎難以想象的時間、精力和人類的聰明才智——跨越多個大陸的數千人以及地球上一些最復雜的機器的無盡土地。

也許這些機器中最重要的是執行是極紫外(EUV)光刻。EUV 光刻是數十年研發的產物,現已成為過去兩代尖端芯片背后的驅動技術,在過去三年中用于每一款高端智能手機、平板電腦、筆記本電腦和服務器。

然而摩爾定律必須繼續前進,芯片制造商繼續推進他們的路線圖,這意味著他們需要進一步縮小設備的幾何尺寸。

因此,在 ASML,我(指代本文作者JAN VAN SCHOOT,下同)和我的同事正在開發下一代光刻技術。它被稱為高數值孔徑 EUV 光刻,涉及對系統內部光學器件的重大檢修。

高數值孔徑 EUV 將于 2025 年投入商業使用,芯片制造商將依靠其能力在本十年末保持其承諾的進步。

光刻的3個因素

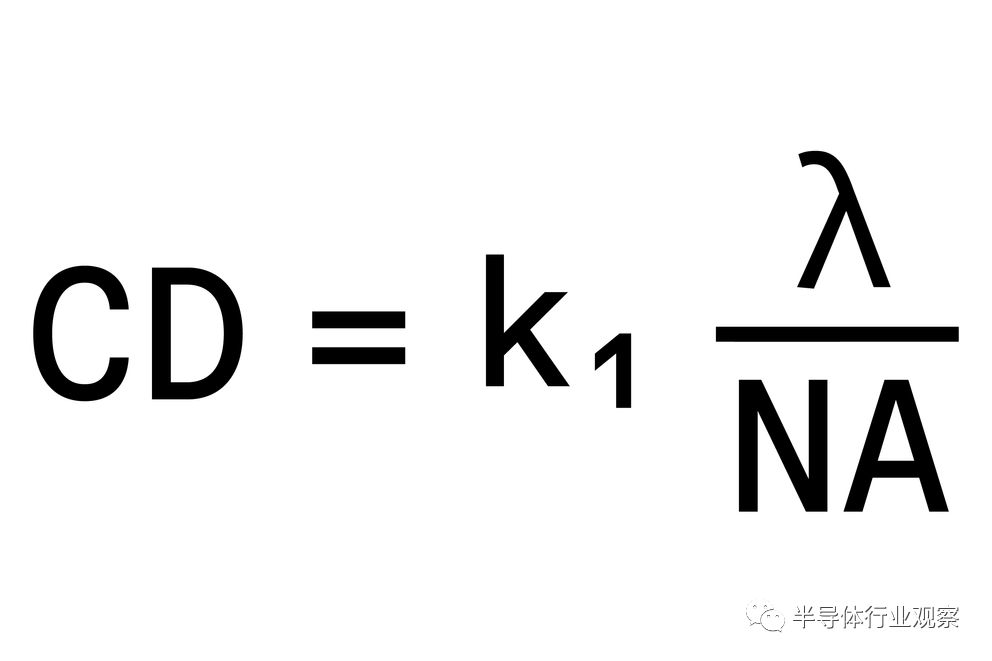

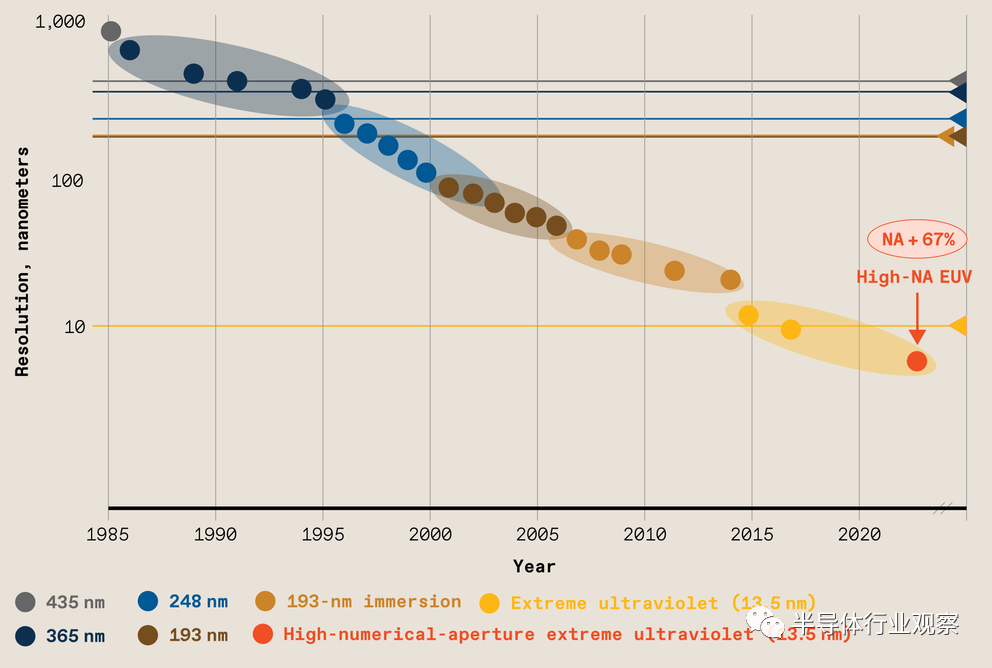

摩爾定律依賴于提高光刻分辨率,以便芯片制造商可以鋪設越來越精細的電路。在過去 35 年里,工程師們通過綜合研究以下三個因素,將分辨率降低了兩個數量級:光的波長;k 1,封裝過程相關因素的系數;數值孔徑 (NA),衡量系統發光角度范圍的指標。

臨界尺寸(即使用某種光刻曝光工具可以打印的最小特征尺寸)與光的波長除以光學器件的數值孔徑成正比。因此,您可以通過使用較短的光波長或較大的數值孔徑或兩者的組合來實現更小的臨界尺寸。例如,通過改進制造過程控制,可以將k 1值推至盡可能接近其物理下限0.25。

一般來說,提高分辨率的最經濟的方法是增加數值孔徑并改進工具和工藝控制以實現更小的 k 1。只有當芯片制造商沒有辦法進一步提高 NA 和 k 1時,他們才會采取減小光源波長的方法。

然而,業界不得不多次改變波長。波長的歷史進程從使用汞燈產生的 365 納米,到 20 世紀 90 年代末通過氟化氪激光器產生的 248 納米,然后在 20 世紀 90 年代初期,通過氟化氬激光器產生的 193 納米。對于每一代波長,光刻系統的數值孔徑都在逐漸增加,然后工業界才轉向更短的波長。

例如,隨著 193 nm 的使用即將結束,引入了一種增加 NA 的新方法:浸沒式光刻。通過在透鏡底部和晶圓之間放置水,NA 可以從 0.93 顯著增大到 1.35。自 2006 年左右推出以來,193 納米浸沒式光刻技術一直是尖端光刻技術的行業主力。

在過去四十年中,光刻技術的分辨率提高了約 10,000 倍。這在一定程度上是由于使用了越來越小的光波長,但它也需要更大的數值孔徑和改進的處理技術。

EUV 的黎明

但隨著打印小于 30 nm 的特征的需求增加,并且由于 193 nm 光刻的 NA 已達到極限,遵循摩爾定律變得越來越復雜。要創建小于 30 nm 的特征,需要使用多個圖案來生產單層芯片特征(這在技術和經濟上都是一項繁瑣的技術),或者需要改變波長。我們花了 20 多年的時間和無與倫比的開發努力才將下一個新波長上線:13.5 納米 EUV。

EUV 需要一種全新的發光方式。這是一個非常復雜的過程,需要使用強大的CO 2激光撞擊飛行中的熔融錫滴,然后將錫蒸發成等離子體,發射出光子能量光譜。EUV 光學器件從該光譜中獲取所需的 13.5 nm 波長,并將其引導通過一系列鏡子,然后從圖案掩模反射,將該圖案投影到晶圓上。所有這些都必須在超凈真空中完成,因為 13.5 nm 波長會被空氣吸收。(在前幾代光刻技術中,光線通過掩模將圖案投射到晶圓上。但 EUV 很容易被吸收,因此掩模和其他光學器件必須是反射性的。)

在真空室中,EUV 光 [紫色] 在從光掩模 [頂部中心] 反射之前經過多個鏡子反射。從那里,光繼續它的旅程,直到它被投射到帶有光掩模圖案的晶圓上[底部中心]。插圖顯示了當今數值孔徑為 0.33 的商業系統。NA 為 0.55 的未來系統中的光學器件將會有所不同。

從 193 納米光轉向 EUV 在一定程度上降低了臨界尺寸。一種稱為“制造設計”的過程,涉及設置電路塊的設計規則以利用光刻的限制,在降低 k 1方面發揮了很大作用 。現在是時候再次提高數值孔徑了,從現在的 0.33 提高到 0.55。

讓高數值孔徑 EUV 發揮作用

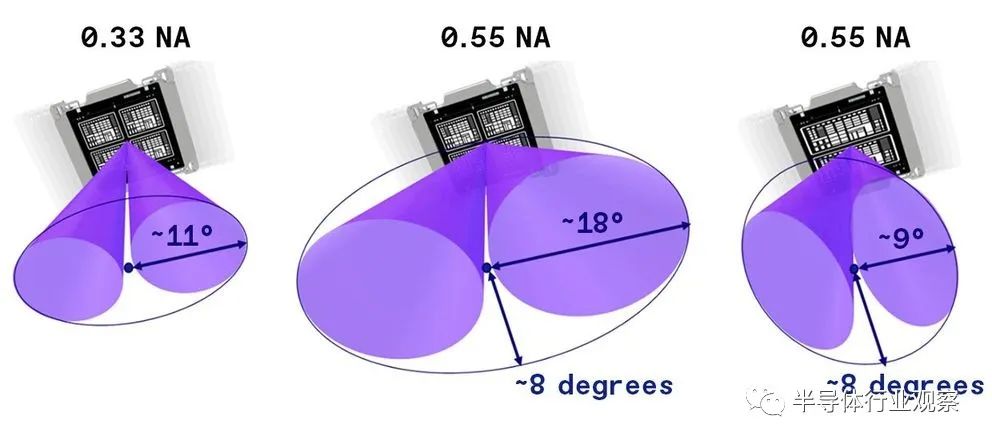

將 NA 從今天的 0.33 增加到目標值 0.55 不可避免地需要進行一系列其他調整。EUV 光刻等投影系統在晶圓和掩模處都有 NA。當您增加晶圓上的 NA 時,也會增加掩模上的 NA。因此,在掩模處,入射和出射的光錐變得更大,并且必須彼此成一定角度以避免重疊。重疊的光錐會產生不對稱的衍射圖案,從而導致令人不快的成像效果。

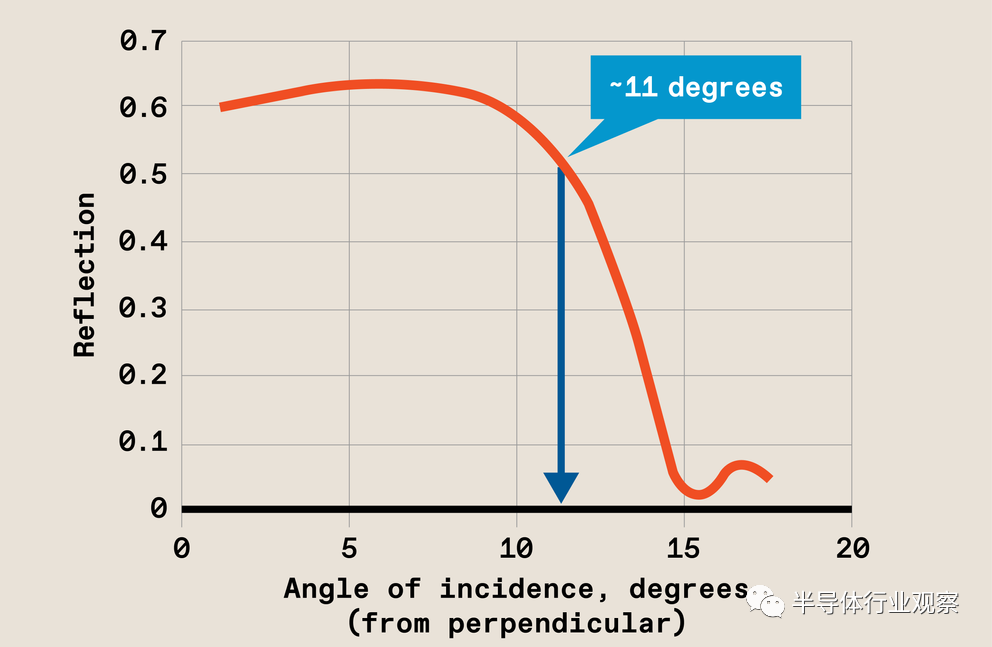

但這個角度是有限制的。由于 EUV 光刻所需的反射掩模實際上是由多層材料制成的,因此無法確保在特定反射角度以上獲得適當的反射。EUV掩模的最大反射角為11度。還有其他挑戰,但反射角度是最大的。

如果 EUV 光以太陡的角度照射光掩模,它將無法正確反射

當今 EUV 中掩模處的反射角已達到極限 [左] 增加 EUV 的數值孔徑將導致反射角過寬 [中]。因此,高數值孔徑 EUV 使用變形光學器件,該光學器件允許角度僅在一個方向上增加 [右]。以這種方式成像的場是一半大小,因此掩模上的圖案必須在一個方向上扭曲,但這足以維持通過機器的吞吐量。

克服這一挑戰的唯一方法是提高稱為縮小的質量(The only way to overcome this challenge is to increase a quality called demagnification)。縮小就像它聽起來的那樣——從掩模上獲取反射圖案并將其縮小。為了補償反射角問題,我和我的同事必須將縮小倍率加倍至 8 倍。因此,晶圓上掩模的成像部分將小得多。這種較小的像場意味著需要更長的時間才能產生完整的芯片圖案。事實上,這一要求會將我們的高數值孔徑掃描儀的吞吐量降低到每小時 100 個晶圓以下,這一生產率水平將使芯片制造變得不經濟。

值得慶幸的是,我們發現只需要在一個方向上增加縮小倍數(demagnification),即發生最大反射角的方向。另一個方向的縮小率可以保持不變。這使得晶圓上的場尺寸可接受,約為當今 EUV 系統中使用的尺寸的一半,即 26 x 16.5 毫米,而不是 26 x 33 毫米。這種方向相關的或變形的縮小構成了我們高數值孔徑系統的基礎。光學器件制造商卡爾蔡司付出了巨大的努力來設計和制造符合我們新機器所需規格的變形鏡頭。

為了確保半尺寸場具有相同的生產率水平,我們必須重新開發系統的掩模版和晶圓臺(分別固定掩模和晶圓的平臺),并在掃描過程中使它們彼此同步移動。重新設計產生了納米級精度的平臺,加速度提高了四倍。

高數值孔徑 EUV 將于 2025 年投產

第一個高數值孔徑 EUV 系統 ASML EXE:5000 將安裝在我們與比利時納米電子研究機構 Imec 于 2024 年初聯合開設的新實驗室中。該實驗室將允許客戶、掩模制造商、光刻膠供應商和其他公司開發使高數值孔徑 EUV 成為現實所需的基礎設施。

我們必須使其成為現實,因為高數值孔徑 EUV 是維持摩爾定律的關鍵組成部分。不過,達到 0.55 NA 并不是最后一步。從那時起,ASML、蔡司和整個半導體生態系統將以我們難以想象的方式進一步向更好、更快和創新的技術延伸。

審核編輯:劉清

-

激光器

+關注

關注

17文章

2485瀏覽量

60257 -

芯片制造

+關注

關注

9文章

610瀏覽量

28773 -

光譜儀

+關注

關注

2文章

947瀏覽量

30710 -

ASML

+關注

關注

7文章

718瀏覽量

41179 -

EUV光刻機

+關注

關注

2文章

128瀏覽量

15095

原文標題:給芯片“續命”的一臺機器

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

具有非常高數值孔徑的反射顯微鏡系統

今日看點丨ASML今年將向臺積電、三星和英特爾交付High-NA EUV;理想 L9 出事故司機質疑 LCC,產品經理回應

ASML創下新的EUV芯片制造密度記錄,提出Hyper-NA的激進方案

臺積電轉變態度?秘密訪問ASML總部引發行業關注

買臺積電都嫌貴的光刻機,大力推玻璃基板,英特爾代工的野心和危機

臺積電A16制程采用EUV光刻機,2026年下半年量產

英特爾完成首臺高數值孔徑EUV光刻機安裝,助力代工業務發展

英特爾完成高數值孔徑EUV光刻機,將用于14A制程

阿斯麥(ASML)公司首臺高數值孔徑EUV光刻機實現突破性成果

單模光纖數值孔徑一般是多少

Intel和ASML宣布全球第一臺High-NA光刻機“首光”

英特爾成為全球首家購買3.8億美元高數值孔徑光刻機的廠商

給芯片“續命”的一臺機器 讓高數值孔徑EUV發揮作用

給芯片“續命”的一臺機器 讓高數值孔徑EUV發揮作用

評論