點(diǎn)擊上方藍(lán)字關(guān)注我們

芯片設(shè)計(jì)和驗(yàn)證工程師通常要為在硅片上實(shí)現(xiàn)的每一行RTL代碼寫出多達(dá)10行測(cè)試平臺(tái)代碼。驗(yàn)證任務(wù)在設(shè)計(jì)周期內(nèi)可能會(huì)占用50%或更多的時(shí)間。盡管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發(fā)現(xiàn)系統(tǒng)級(jí)錯(cuò)誤,芯片設(shè)計(jì)人員正利用FPGA來加速算法創(chuàng)建和原型設(shè)計(jì)。

利用FPGA處理大型測(cè)試數(shù)據(jù)集可以使工程師快速評(píng)估算法和架構(gòu)并迅速做出權(quán)衡。工程師也可以在實(shí)際環(huán)境下測(cè)試設(shè)計(jì),避免因使用HDL仿真器耗大量時(shí) 間。系統(tǒng)級(jí)設(shè)計(jì)和驗(yàn)證工具(如matlab和Simulink)通過在FPGA上快速建立算法原型,可以幫助工程師實(shí)現(xiàn)這些優(yōu)勢(shì)。

本文將介紹使用MATLAB和Simulink創(chuàng)建FPGA原型的最佳方法。這些最佳方法包括:在設(shè)計(jì)過程初期分析定點(diǎn)量化的效應(yīng)并優(yōu)化字長,產(chǎn)生更 小、更高效的實(shí)現(xiàn)方案;利用自動(dòng)HDL代碼生成功能,更快生成FPGA原型;重用具有HDL協(xié)同仿真功能的系統(tǒng)級(jí)測(cè)試平臺(tái),采用系統(tǒng)級(jí)指標(biāo)分析HDL實(shí)現(xiàn) 方案;通過FPGA在環(huán)仿真加速驗(yàn)證(圖1)。

為什么在FPGA上建立原型?

在FPGA上建立算法原型可以增強(qiáng)工程師的信心,使他們相信自己的算法在實(shí)際環(huán)境中的表現(xiàn)能夠與預(yù)期相符。除了高速運(yùn)行測(cè)試向量和仿真方案,工程師還可 以利用FPGA原型試驗(yàn)軟件功能以及諸如RF和模擬子系統(tǒng)的相關(guān)系統(tǒng)級(jí)功能。此外,由于FPGA原型運(yùn)行速度更快,可以使用大型數(shù)據(jù)集,暴露出仿真模型未 能發(fā)現(xiàn)的缺陷。

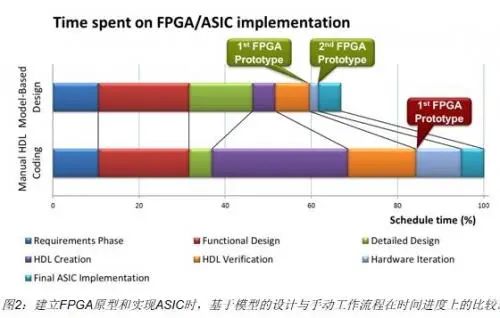

采用HDL代碼生成功能的基于模型的設(shè)計(jì)可以使工程師有效地建立FPGA原型,如圖2所示。該圖向我們展示了這樣一種現(xiàn)實(shí)情況:工程師經(jīng)常縮短詳細(xì)設(shè)計(jì) 階段,試圖通過盡快開始硬件開發(fā)階段以符合開發(fā)周期的要求。現(xiàn)實(shí)中,當(dāng)工程師發(fā)現(xiàn)定點(diǎn)算法達(dá)不到系統(tǒng)要求時(shí),就得在HDL創(chuàng)建階段重新審視詳細(xì)設(shè)計(jì)階段。這樣的重疊工作將使HDL創(chuàng)建階段延長(如紫色長條所示),并可能引發(fā)各種設(shè)計(jì)問題(如膠合邏輯或設(shè)計(jì)補(bǔ)丁)。

由于自動(dòng)HDL代碼生成流程比手工編碼快,工程師得以把節(jié)省下來的時(shí)間投入到詳細(xì)設(shè)計(jì)階段,生成更優(yōu)質(zhì)的定點(diǎn)算法。與手動(dòng)的工作流程相比,這種方法使工程師能夠以更快的速度生成質(zhì)量更佳的FPGA原型。

數(shù)字下變頻器案例研究

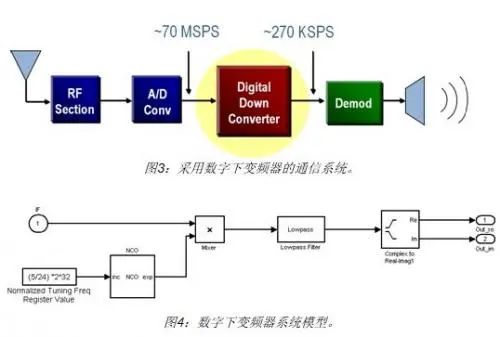

為了說明采用基于模型的設(shè)計(jì)建立FPGA原型的最佳方法,可借助數(shù)字下變頻器(DDC)來進(jìn)行案例研究。在眾多的通信系統(tǒng)中,DDC是一種普通的構(gòu)建塊 (圖3)。該構(gòu)建塊用于將高速通帶輸入轉(zhuǎn)換為低速基帶輸出,以便使用較低采樣率時(shí)鐘進(jìn)行處理。這樣,在硬件實(shí)施階段便可降低功耗、節(jié)約資源。DDC的主要 部件包括:數(shù)控振蕩器(NCO)、混頻器和數(shù)字濾波器鏈路(圖4)。

在設(shè)計(jì)過程初期分析定點(diǎn)量化的效應(yīng)

工程師通常使用浮點(diǎn)數(shù)據(jù)類型來測(cè)試新的構(gòu)想和開發(fā)初始算法。然而,F(xiàn)PGA和ASIC硬件實(shí)現(xiàn)要求轉(zhuǎn)換為定點(diǎn)數(shù)據(jù)類型,而這往往會(huì)造成量化誤差。使用手 動(dòng)工作流程時(shí),通常在HDL編碼過程中執(zhí)行定點(diǎn)量化。在該工作流程中,工程師無法輕易地通過比較定點(diǎn)表示形式和浮點(diǎn)參考值量化定點(diǎn)量化的效應(yīng),而分析針對(duì) 溢出的HDL實(shí)現(xiàn)也同樣不易。

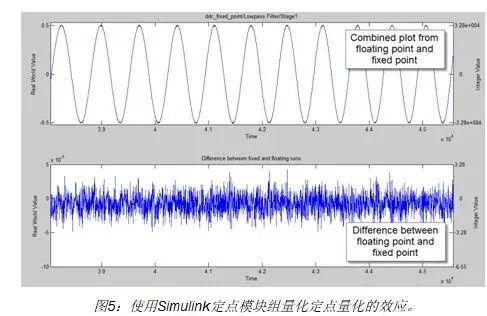

為了明智確定所需的小數(shù)位數(shù),在開始HDL編碼過程之前,工程師需要某種方法來比較浮點(diǎn)仿真結(jié)果與定點(diǎn)仿真結(jié)果。增加小數(shù)位數(shù)可以減小量化誤差;不過,這種方法需要增加字長(區(qū)域增多、功耗升高)。

例如,圖5展示了DDC濾波器鏈路中低通濾波器第一階段浮點(diǎn)與定點(diǎn)仿真結(jié)果的差異。這些差異是因定點(diǎn)量化所致。上方圖形顯示了浮點(diǎn)與定點(diǎn)仿真結(jié)果的重疊效果。下方圖形顯示了圖中每一點(diǎn)的量化誤差。工程師可能需要根據(jù)設(shè)計(jì)規(guī)范來增加小數(shù)位數(shù)以減小由此引出的量化誤差。

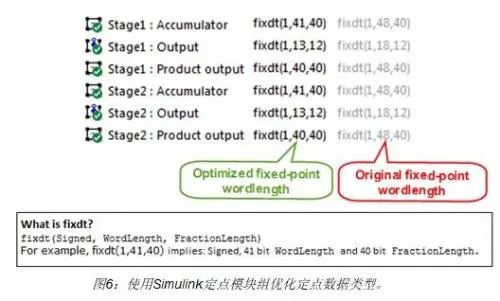

除了選擇小數(shù)位數(shù)之外,工程師還需要優(yōu)化字長,實(shí)現(xiàn)低功耗和區(qū)域優(yōu)化的設(shè)計(jì)。

在DDC案例研究中,工程師使用Simulink定點(diǎn)模塊組將部分?jǐn)?shù)字濾波器鏈路的字長減少了8位之多(圖6)。

利用自動(dòng)HDL代碼生成功能更快生成FPGA原型

在生成FPGA原型時(shí),HDL代碼必不可少。工程師手工編寫了Verilog或VHDL代碼。作為替代選擇,使用HDL編碼器自動(dòng)生成HDL代碼具有眾 多明顯優(yōu)勢(shì)。工程師可以快速地評(píng)估能否在硬件中實(shí)施當(dāng)前算法;迅速評(píng)估不同的算法實(shí)現(xiàn),選擇最佳方案;并在FPGA上更快地建立算法原型。

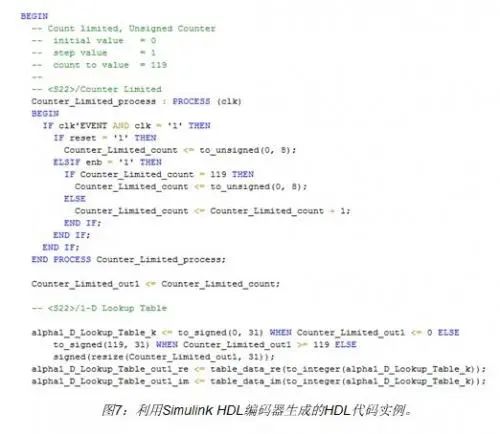

對(duì)于DDC案例研究而言,可以在55秒內(nèi)生成了5780行HDL代碼。工程師可以瀏覽并很快理解代碼(圖7)。自動(dòng)代碼生成功能允許工程師對(duì)系統(tǒng)級(jí)模型進(jìn)行更改,并且,通過重新生成HDL代碼,該功能可以在數(shù)分鐘之內(nèi)生成更新的HDL實(shí)現(xiàn)方案。

重用具有協(xié)同仿真功能的系統(tǒng)級(jí)測(cè)試平臺(tái)進(jìn)行HDL驗(yàn)證

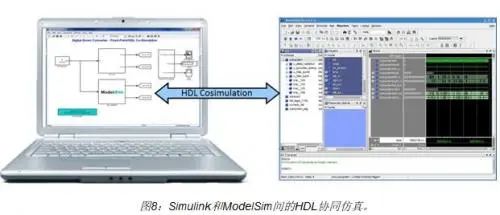

功能驗(yàn)證:HDL協(xié)同仿真使工程師能夠重用Simulink模型,將激勵(lì)驅(qū)動(dòng)至HDL仿真器,并對(duì)仿真輸出執(zhí)行交互式系統(tǒng)級(jí)分析(圖8)。

HDL仿真僅提供數(shù)字波形輸出,而HDL協(xié)同仿真則提供了顯示HDL代碼的完整視圖,并可以訪問Simulink的全套系統(tǒng)級(jí)分析工具。當(dāng)工程師觀察到預(yù)期結(jié)果與HDL仿真結(jié)果存在差異時(shí),可借助協(xié)同仿真進(jìn)一步了解該失配所產(chǎn)生的系統(tǒng)級(jí)影響。

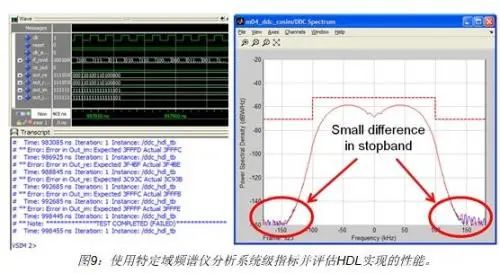

例如,在圖9中,頻譜儀視圖可以使工程師做出明智決定,忽略預(yù)期結(jié)果與HDL仿真結(jié)果之間的失配,其原因是該差異位于阻帶區(qū)。相比之下,數(shù)字波形輸出只 是將預(yù)期結(jié)果與HDL仿真結(jié)果的失配標(biāo)記為誤差。盡管工程師最終可能得出相同的結(jié)論,但這將需要更多的時(shí)間完成所需的分析。

測(cè)試覆蓋率:工程師可以使用HDL驗(yàn)證工具、Simulink設(shè)計(jì)驗(yàn)證工具和ModelSim/Questa自動(dòng)執(zhí)行代碼覆蓋率分析。在該工作流程 中,Simulink設(shè)計(jì)驗(yàn)證工具可針對(duì)模型覆蓋率生成一套測(cè)試用例。HDL驗(yàn)證工具自動(dòng)使用這一套測(cè)試用例運(yùn)行ModelSim/Questa,收集代 碼覆蓋率數(shù)據(jù),以對(duì)生成的代碼加以全面分析。

使用FPGA在環(huán)仿真加速驗(yàn)證

使用系統(tǒng)級(jí)仿真和HDL協(xié)同仿真驗(yàn)證DDC算法之后,便可以立即在FPGA目標(biāo)平臺(tái)上部署DDC算法。對(duì)算法執(zhí)行基于FPGA的驗(yàn)證(也稱為FPGA在 環(huán)仿真)可以增強(qiáng)對(duì)算法在現(xiàn)實(shí)環(huán)境中有效運(yùn)行的信心。相比基于主機(jī)的HDL仿真,該驗(yàn)證可以使工程師更快地運(yùn)行測(cè)試方案。

對(duì)于DDC算法而言,可以使用Simulink模型驅(qū)動(dòng)FPGA輸入激勵(lì)并分析FPGA的輸出(圖10)。與HDL協(xié)同仿真一樣,在Simulink中始終可以利用相關(guān)數(shù)據(jù)進(jìn)行分析。

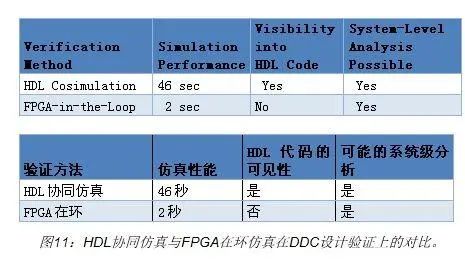

圖11對(duì)比了HDL協(xié)同仿真和FPGA在環(huán)仿真這兩種用于DDC設(shè)計(jì)的驗(yàn)證方法。在本案例中,F(xiàn)PGA在環(huán)仿真的速度是HDL協(xié)同仿真的23倍。這樣的 速度提升使工程師能夠運(yùn)行更廣泛的測(cè)試用例并對(duì)其設(shè)計(jì)進(jìn)行回歸測(cè)試。這使他們能夠識(shí)別出有待進(jìn)一步分析的潛在問題區(qū)域。

盡管HDL協(xié)同仿真速度較慢,但它卻提高了HDL代碼的可見性。因此,它很適合針對(duì)FPGA在環(huán)仿真過程中發(fā)現(xiàn)的問題區(qū)域進(jìn)行更詳細(xì)的分析。

本文小結(jié)

如果工程師遵循本文所述的四種最佳方法,開發(fā)FPGA原型將比傳統(tǒng)的手動(dòng)工作流程快出許多,并能使工程師信心倍增。此外,工程師還可以在整個(gè)開發(fā)過程中 繼續(xù)優(yōu)化自己的模型,并快速地重新生成有關(guān)FPGA實(shí)現(xiàn)的代碼。與依賴手工編寫HDL的傳統(tǒng)工作流程相比,這種能力可以顯著縮短設(shè)計(jì)迭代的周期。

有你想看的精彩 至芯科技FPGA就業(yè)培訓(xùn)班——助你步入成功之路、8月12號(hào)西安中心開課、歡迎咨詢! 基于FPGA的CAN總線通信節(jié)點(diǎn)設(shè)計(jì) 解析高速ADC和DAC與FPGA的配合使用

掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:在FPGA上建立MATLAB和Simulink算法原型

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601875

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Matlab/Simulink/Stateflow建模開發(fā)及仿真測(cè)試

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大規(guī)模電力電子系統(tǒng)仿真

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

利用Matlab函數(shù)實(shí)現(xiàn)深度學(xué)習(xí)算法

基于FPGA的實(shí)時(shí)邊緣檢測(cè)系統(tǒng)設(shè)計(jì),Sobel圖像邊緣檢測(cè),FPGA圖像處理

電路仿真軟件simulink的工作原理

電路仿真軟件simulink使用方法

fpga原型驗(yàn)證平臺(tái)與硬件仿真器的區(qū)別

fpga原型驗(yàn)證流程

在FPGA上為FPGA設(shè)計(jì)PCB的步驟詳解

原型平臺(tái)是做什么的?proFPGA驗(yàn)證環(huán)境介紹

在FPGA上建立MATLAB和Simulink算法原型

在FPGA上建立MATLAB和Simulink算法原型

評(píng)論