模板模式

Template method patttern: 在一個(gè)方法中定義一個(gè)算法骨架,并將某些步驟推遲到子類中實(shí)現(xiàn)。子類在不改變算法整體結(jié)構(gòu)的情況下,重新定義算法中的某些步驟。

模板模式的使用很簡(jiǎn)單,就是 繼承 + 重寫 的配合使用。在父類中定義一函數(shù)XXX(), 里面封裝了函數(shù) pre_XXX()和函數(shù) post_XXX(), 當(dāng)執(zhí)行函數(shù)XXX()時(shí),會(huì)自動(dòng)執(zhí)行 pre_XXX(), post_XXX(), 相當(dāng)于在父類中固定了這種執(zhí)行流程,pre_XXX() -> XXX() -> post_XXX()。pre_XXX(), post_XXX()擴(kuò)展了XXX()的功能。子類繼承父類,根據(jù)需求重寫。pre_XXX(), post_XXX()相當(dāng)于hook, 也可以廣義的稱為回調(diào)函數(shù),但是和回調(diào)函數(shù)仍有區(qū)別,在下一節(jié)具體闡述。

UVM中常見:

squence中的start()前后插入pre_start(),post_start(), body()前后的pre_body(), post_body();

uvm_object中copy()被調(diào)用會(huì)自動(dòng)執(zhí)行do_copy(), compare()中的do_compare(), print()中的do_print(), pack()中的do_pack(), unpack()中的do_unpack()。

phase中的pre_xxx_phase, post_xxx_phase

SV調(diào)用randomize()自動(dòng)調(diào)用pre_randomize(), post_randomize()。

這里就不在一一列舉和代碼展示了,

策略模式

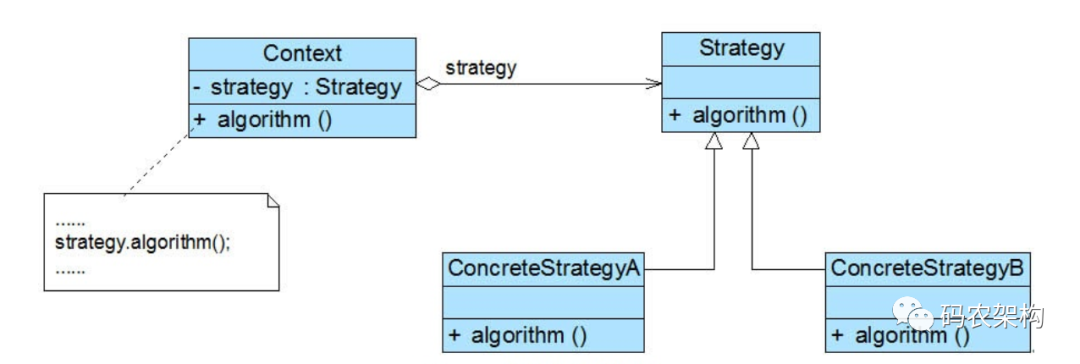

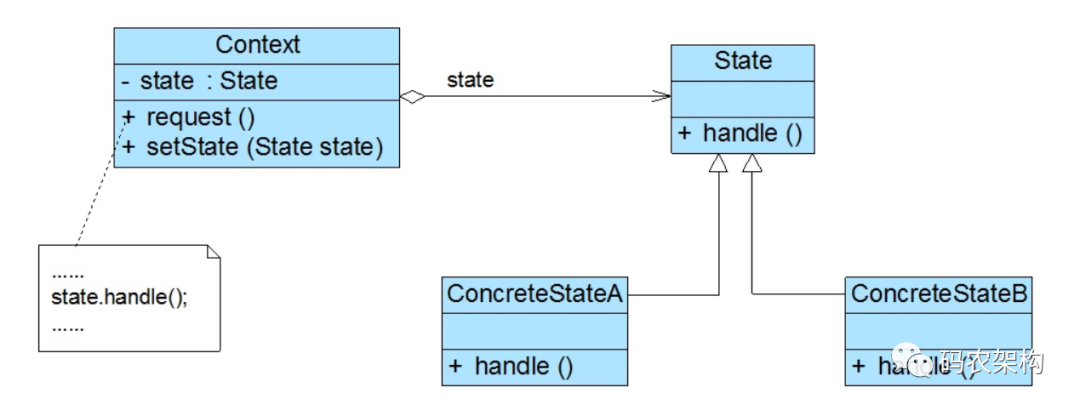

Strategy Pattern: 定義一種算法類,將每個(gè)算法分別封裝起來,讓它們可以相互替換。算法調(diào)用者只需包含抽象算法的類然后調(diào)用算法,算法的具體實(shí)現(xiàn)被獨(dú)立出來,保持主體的結(jié)構(gòu)穩(wěn)定。

策略模式讓具體算法獨(dú)立于算法的調(diào)用者,這里的算法指一個(gè)具體的行為,具備多態(tài)特性,可以實(shí)現(xiàn)重寫,算法的調(diào)用可以簡(jiǎn)單理解為一個(gè)函數(shù)被調(diào)用。策略模式其實(shí)就是 組合 + 多態(tài) 的配合使用。

在第一篇中,提到了composition這個(gè)單詞,也就是組合,合成的意思。相對(duì)于繼承(Inheritance),合成使用了“有”(has-a)的關(guān)系,繼承使用了“是”(is-a)的關(guān)系。對(duì)于抽象算法的實(shí)現(xiàn),可以聯(lián)系到第一篇中提到的interface class, 一種面向接口編程的特性。

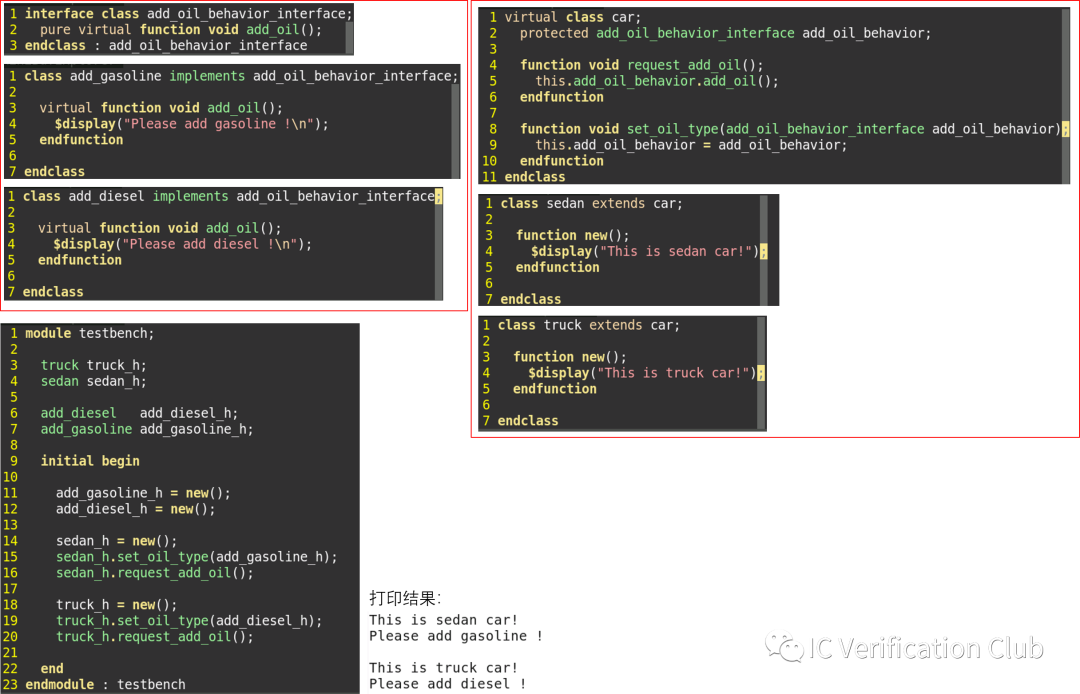

下面將 composition 和 interface class兩種結(jié)合起來,使用Systemverilog編寫一個(gè)簡(jiǎn)單的策略模式的示例:

1. car 兩個(gè)子類,sedan轎車和truck卡車,都需要請(qǐng)求加油。

2. 抽象類add_oil_behavior_interface, 兩個(gè)子類 add_gasoline add_diesel 是一種 add_oil “算法” 不同的實(shí)現(xiàn),一個(gè)加汽油,一個(gè)加柴油。

3. 在testbench中,通過set_oil_type將實(shí)例對(duì)象傳入。類的多態(tài),調(diào)用add_oil, 根據(jù)對(duì)象調(diào)用實(shí)際“算法”。

上面的例子通過策略模式構(gòu)建,似乎有些繁瑣,通過if else判斷是卡車還是轎車選擇加什么油,更簡(jiǎn)單明了。但是這里僅僅使用了一種車加油的“特征”,如果有更多種類的車,更多特征,比如載人數(shù)量,車身顏色,組件型號(hào)等,使用if else對(duì)各種類型的車做歸類將使代碼難以維護(hù)。如果卡車有一天加了汽油,只需要set_oil_type(add_gasoline_h)就可以完成,通過if else編寫的代碼顯然hardcoding了。

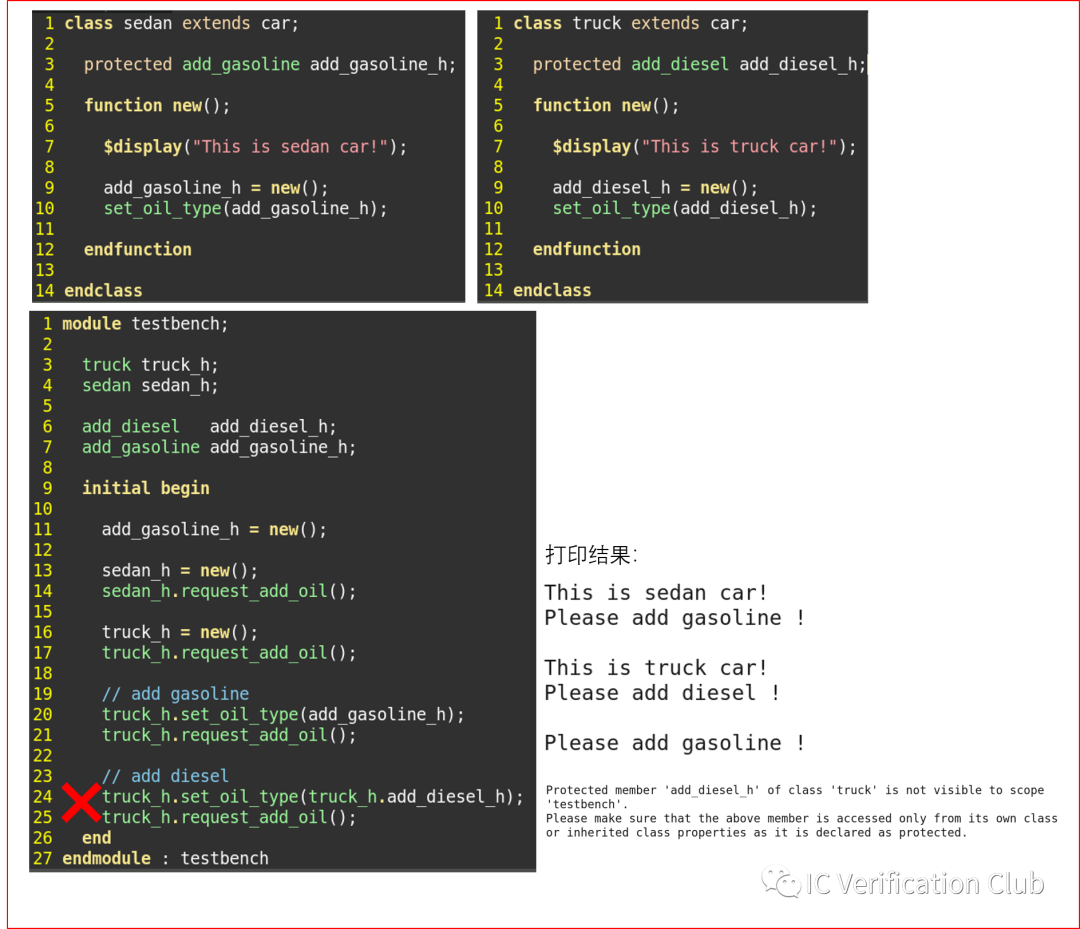

上述代碼還不夠make sense,無路是汽車還是卡車,當(dāng)被創(chuàng)建時(shí),應(yīng)該有一個(gè)default的默認(rèn)加油方式,所以可以改寫如下:

在汽車或者卡車被創(chuàng)建時(shí),就指定一種加油方式。line20將卡車切換成加汽油,line24再切換成加柴油時(shí),報(bào)錯(cuò)。因?yàn)樽兞勘?strong> protected 修飾,不可以在類外部調(diào)用。

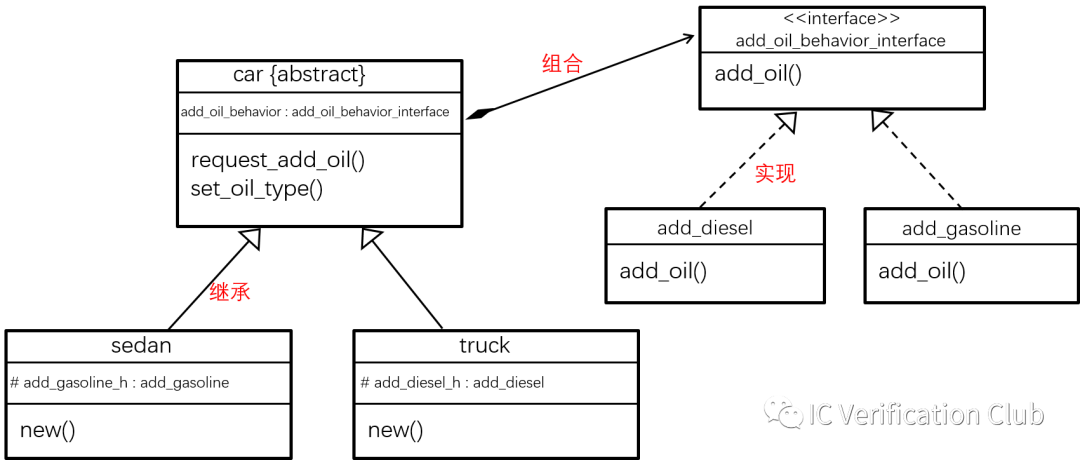

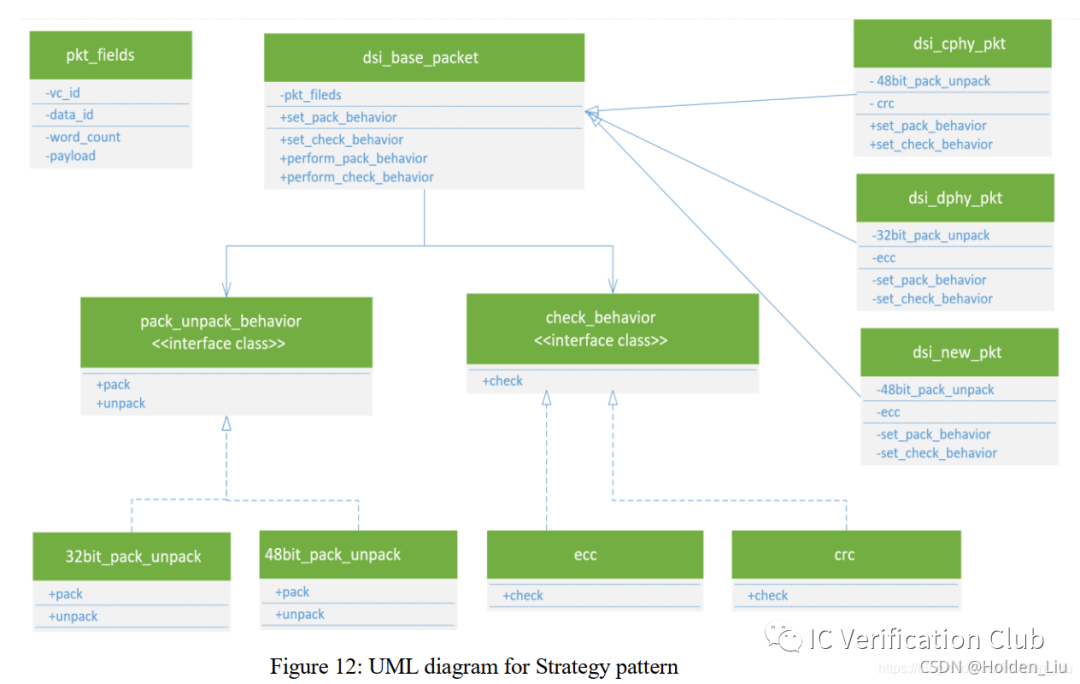

UML圖:

所以策略模式的 “策略” 體現(xiàn)在對(duì)算法的調(diào)用和算法的實(shí)現(xiàn)的解耦,我們把“算法”(具體函數(shù)處理)封裝到一個(gè)抽線類中,在調(diào)用類中聲明這個(gè)抽象類(這便是composition,調(diào)用類可以使用抽象類的方法),對(duì)抽象類實(shí)現(xiàn)或者重寫成多個(gè)子類,調(diào)用類調(diào)用算法時(shí),根據(jù)內(nèi)部抽象類句柄指向的具體的子類對(duì)象,調(diào)用子類對(duì)象的”算法“(多態(tài))。

策略模式很實(shí)用,在純軟件編程中非常常見。在UVM源碼中也應(yīng)用到了策略模式,比如default_sequence和uvm_callback。UVM中使用的策略模式和純軟件編程中所總結(jié)的策略模式稍有不同,但核心是一樣的,通過 “ 組合 + 多態(tài)” 的方式,實(shí)現(xiàn)對(duì)算法的調(diào)用和算法的實(shí)現(xiàn)的解耦。

default_sequence

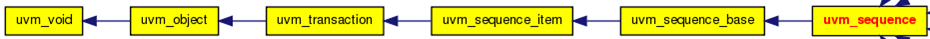

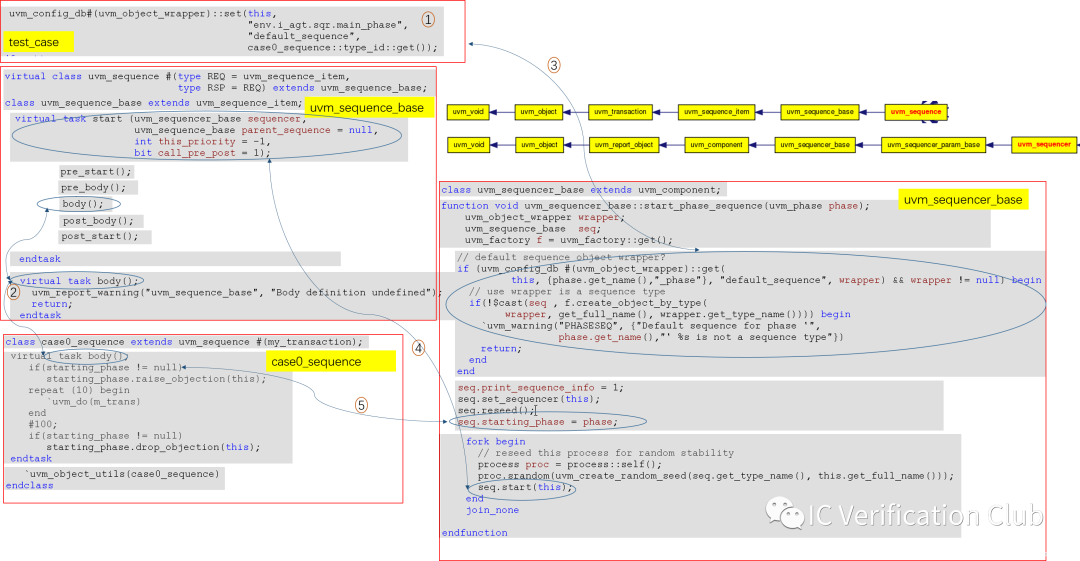

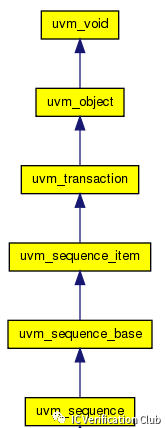

構(gòu)建用例創(chuàng)建的sequence繼承于uvm_sequence, 繼承關(guān)系如圖:

sequence不像component一樣,沒有被UVM賦予phase機(jī)制,sequence的運(yùn)行需要“掛載”在sequencer上,一般有三種方式(UVM設(shè)計(jì)模式 (六)命令模式、三種sequence啟動(dòng)方式、start_item/finish_item、中介模式、virtual sequence):

1:采用default_sequence的方式啟動(dòng)

2. 直接調(diào)用sequence的start()函數(shù)啟動(dòng)

3. 在virtual sequence中調(diào)用uvm_do宏啟動(dòng)sequence

下面梳理下default_sequence中策略模式的應(yīng)用:

1. 將case0_sequence“掛載”到sequencer上。

2. uvm_sequence_base中的虛函數(shù)start()調(diào)用了pre/post_start(), pre/post_body(),以及body()函數(shù),這些函數(shù)都是虛函數(shù),且沒有定義任何操作。case0_sequence重寫body()函數(shù)。

3. 當(dāng)執(zhí)行到main_phase()時(shí),會(huì)執(zhí)行uvm_sequencer_base中的start_phase_sequence()函數(shù),uvm_config_db#() get::()獲得case0_sequence的type_id, 然后調(diào)用factory的create_object_by_type創(chuàng)建case0_sequence的實(shí)例。(參考上一節(jié)工廠模式) $cast中的seq是uvm_sequence_base類型,多態(tài)。

4. 調(diào)用seq.start(), 執(zhí)行body()函數(shù)的代碼。

5. 只有使用default_sequence的方式啟動(dòng),case0_sequence中starting_phase才不等于 null.

(只摘取了與策略模式有關(guān)的 code) + :

default_sequence的方式啟動(dòng),會(huì)調(diào)用seq.start()函數(shù)來運(yùn)行body()函數(shù)的代碼, 不同用例body()函數(shù)的實(shí)現(xiàn)不同,這里的body()就相當(dāng)于策略模式中的“算法",將body()函數(shù)的實(shí)現(xiàn)放在子類sequence中重寫,實(shí)現(xiàn)解耦。

不同之處是,UVM中通過 confid_db和facotry結(jié)合創(chuàng)建sequence,更靈活。抽象類使用的是virtual class而不是interface class,區(qū)別在第一篇中有闡述。UVM設(shè)計(jì)模式(一)

callback

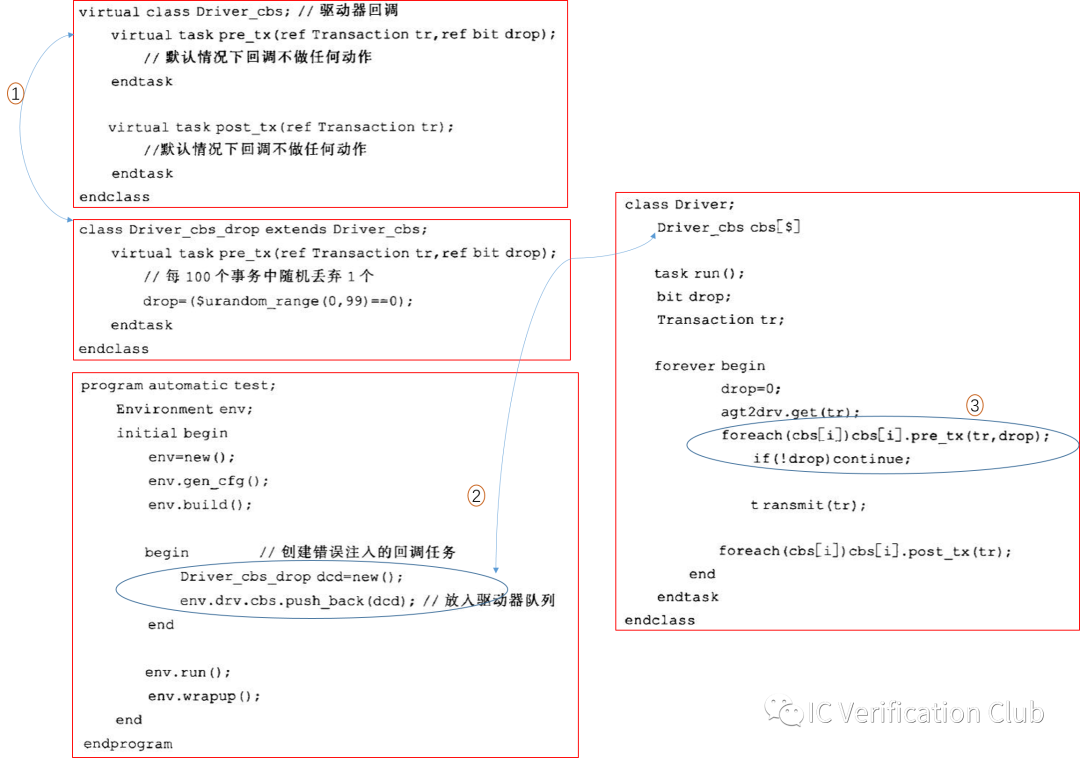

在學(xué)習(xí)uvm_callback之前,先看一下如何用Systemverilog寫一個(gè)簡(jiǎn)單的callback。

1. 抽象函數(shù)Driver_cbs定義了抽象函數(shù)pre_tx(), post_tx(),然后子類Driver_cbs_drop重寫了pre_tx()函數(shù),實(shí)現(xiàn)了每100個(gè)事務(wù)隨機(jī)丟棄1個(gè)事務(wù)的功能。在class Driver中聲明了這個(gè)抽象類的隊(duì)列 cbs[$] 。

2. 在test中創(chuàng)建Driver_cbs_drop的實(shí)例對(duì)象,然后放入到cbs[$]這個(gè)隊(duì)列中。可以放進(jìn)去的原因是類的多態(tài),父類句柄可以指向子類對(duì)象。

3. 遍歷cbs[$]中放入的callback類,執(zhí)行子類對(duì)象的pre_tx()函數(shù)。

源代碼:《SystemVerilog 驗(yàn)證-測(cè)試平臺(tái)編寫指南》 8.7 :

上述的callback和策略模式的實(shí)現(xiàn)方式一樣(組合 + 多態(tài)),在Driver類聲明抽象類,然后調(diào)用抽象類中的函數(shù),根據(jù)類的多態(tài),實(shí)際調(diào)用的是子類重寫過的函數(shù)。解耦pre_tx()函數(shù)的實(shí)現(xiàn)與調(diào)用,保持代碼結(jié)構(gòu)穩(wěn)定,提高擴(kuò)展性。

不同點(diǎn)在于callback定義的 pre_tx() 更像一個(gè)hook鉤子,callback 常在VIP中使用,為了滿足不同使用者的需求(在 driver中實(shí)現(xiàn)注錯(cuò)或者異常 ;在 monitor中收集功能覆蓋率;或者實(shí)現(xiàn)控制 objection 的 raise/drop功能 ),設(shè)計(jì)VIP的人員需要留出這個(gè)hook供使用者根據(jù)業(yè)務(wù)需求自行定義,使用者不需要了解VIP driver的具體實(shí)現(xiàn),只關(guān)心這個(gè)hook的實(shí)現(xiàn)。從這點(diǎn)來看,callback和上一節(jié)中的模板模式更接近,只不過實(shí)現(xiàn)方式不同,模板模式利用 繼承+重寫 實(shí)現(xiàn)。callbcak提供的hook相比模板模式提供的hook,擴(kuò)展性和復(fù)用性更好,但是實(shí)現(xiàn)更復(fù)雜些。實(shí)際工作根據(jù)業(yè)務(wù)需求選擇合適方式預(yù)留hook。

而純軟件中的策略模式是為了將一類算法歸一抽象,然后分別實(shí)現(xiàn)。側(cè)重于每一種算法的相互替代,使算法的變化獨(dú)立于使用它們的客戶端(這里的客戶端指使用算法的代碼)。通過解耦控制模塊代碼的復(fù)雜度和代碼量,解決大量使用if-else分支判斷邏輯。除此之外,策略模式還能滿足開閉原則呢,添加新策略的時(shí)候,最小化、集中化的代碼改動(dòng),減少引入bug的風(fēng)險(xiǎn)。

但是遵循第一篇中提到的KISS(Keep It Stupid Simple)原則,怎么簡(jiǎn)單怎么來,就是最好的設(shè)計(jì),非得用策略模式,搞出n多類,反倒是一種過度設(shè)計(jì)。設(shè)計(jì)模式之美

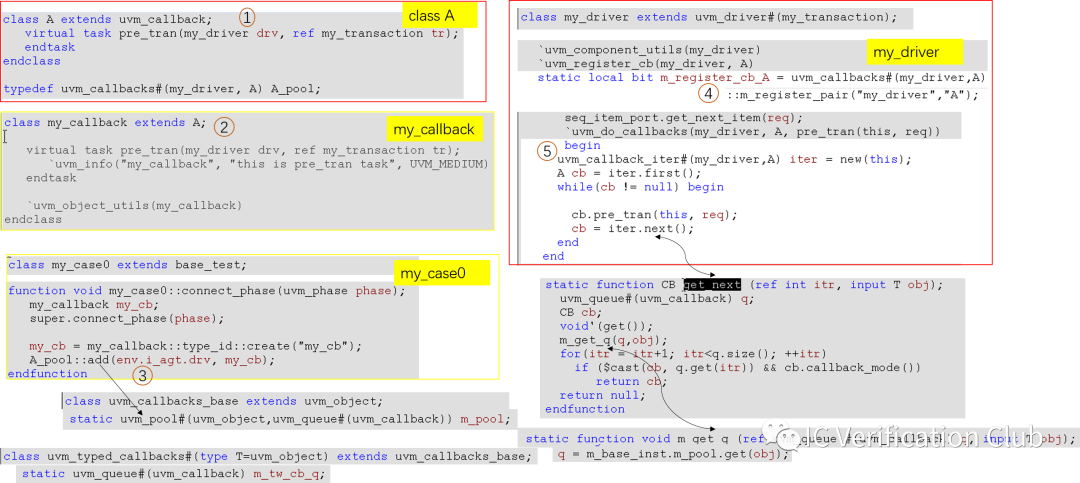

uvm_callback

uvm_callback的大體結(jié)構(gòu)與上一節(jié)提到的callbcak類似,具體實(shí)現(xiàn)細(xì)節(jié)不在列舉(可參考《UVM1.1 應(yīng)用指南及源碼分析》- 19 callback機(jī)制源碼分析 ),分析側(cè)重日常調(diào)用以及策略模式的相關(guān)內(nèi)容:

下圖紅框由VIP開發(fā)者或者平臺(tái)搭建者完成,黃框?yàn)閏allback調(diào)用者完成。

1. 設(shè)計(jì)一個(gè)class A包含虛函數(shù)pre_tran()作為hook,供driver調(diào)用。typedef 將 A_pool 定義為 uvm_callbacks#(my_dirver, A) 類型的參數(shù)化的類。(class A相當(dāng)于上節(jié)的 class Driver_cbs)

2. class my_callback 繼承 class A, 重寫 task pre_tran()。(class my_callback相當(dāng)于上節(jié)的class Driver_cbs_drop)

3. 在tc的connect_phase()中創(chuàng)建my_callback的對(duì)象,調(diào)用靜態(tài)函數(shù) A_pool::add(),完成對(duì)uvm_callbacks_base類中靜態(tài)關(guān)聯(lián)數(shù)組m_pool的賦值。(uvm_pool看成關(guān)聯(lián)數(shù)組, uvm_queue看成隊(duì)列, m_pool索引為object(drv), 值為存放uvm_callback(my_cb)的uvm_queue )( 此處的 uvm_queue相當(dāng)于上節(jié)的 cbs[$] 隊(duì)列,調(diào)用函數(shù) add()相當(dāng)于上節(jié) cbs.push_back(dcd) 。)

(不同之處,UVM引入了 m_pool 這個(gè)關(guān)聯(lián)數(shù)組作為 “池子“,可以存放 A類型的 callback, 也可以存放 B類型的 callback, 所以 A類型對(duì)應(yīng)一個(gè)隊(duì)列,B類型對(duì)應(yīng)一個(gè)隊(duì)列。此例中只用到了m_pool 。class uvm_typde_callbacks # (type T = uvm_object) 中還有一個(gè)靜態(tài)變量 m_tw_cb_q ,當(dāng) A_pool :: add (null, my_cb),第一個(gè)參數(shù)為 null,則 my_cb放入m_tw_cb_q隊(duì)列中。null則不指定具體 instance,表明該 callback對(duì)這個(gè) type實(shí)例的對(duì)象都有效 。m_pool全局只有一個(gè),而m_tw_cb_q則每個(gè) type對(duì)應(yīng)一個(gè))

4. `uvm_register_cb宏展開,調(diào)用靜態(tài)函數(shù)m_register_pair(), 完成callback與object的配對(duì)。試想,如果平臺(tái)設(shè)計(jì)者設(shè)計(jì)了callback A 給driver使用 `uvm_register_cb(my_driver,A),callback B給monitor使用 `uvm_register_cb(my_monitor,B),以及其他很多callback。而使用者在調(diào)用callback時(shí)卻在A_pool::add() 中誤加入了類型B的callback, 編譯仿真都正常進(jìn)行,但是實(shí)際hook并沒有被調(diào)用。幸運(yùn)的是,會(huì)打印一個(gè)warning供使用者debug,幫助他及時(shí)發(fā)現(xiàn)前面的錯(cuò)誤。

5. `uvm_do_callbacks(T,CB,THIS,METHOD)展開后,創(chuàng)建uvm_callback_iter的實(shí)例,這個(gè)類提供的是iterator迭代器的功能,因?yàn)樗衏allback都放在了容器 m_pool 或 m_tw_cb_q 中,在此處調(diào)用的callback需要滿足 uvm_object=my_driver, uvm_callback = A 的條件,需要對(duì)容器檢索遍歷獲得。如上節(jié)單獨(dú)的foreach循環(huán)無法滿足要求,所以UVM提供了一個(gè)迭代器類專門負(fù)責(zé)此事。該示例中重復(fù)的過程如下:(此處對(duì) uvm_queue的遍歷相當(dāng)于上節(jié)通過 foreach()對(duì) cbs[$] 的遍歷過程)

通過 m_get_q() 函數(shù)在 m_pool 中找到 和driver相對(duì)應(yīng)的 callback uvm_queue(ref類型,賦值給get_first()函數(shù)中的q變量),然后在q隊(duì)列中找到A類型的callback, 調(diào)用callback中的函數(shù)。然后重復(fù)執(zhí)行上述步驟,直到 cb == null 結(jié)束。

uvm_queue中可能會(huì)放不同類型的callback,通過 $cast篩選出符合的類型。

如果使用 A_pool :: add (null, my_cb), 則是對(duì)m_tw_cb_q 隊(duì)列的遍歷,這里沒有列出。

更多內(nèi)容見:UVM設(shè)計(jì)模式 ( 五 ) 迭代器模式、Python/SV中的迭代器、uvm_callback_iter、scoreboard中的迭代器

+ (源代碼UVM實(shí)戰(zhàn) 9.1.4):

根據(jù)上述紅色斜體的內(nèi)容描述,UVM中的callback和SV中的callback使用思路一致,也是 組合 + 多態(tài) 的實(shí)現(xiàn)方式,和策略模式一樣。通過UVM工廠模式的重寫功能也可以實(shí)現(xiàn)callback的效果,選擇哪種方式要根據(jù)實(shí)際場(chǎng)景。

擴(kuò)展使用

在實(shí)際工作中,可以采用策略模式進(jìn)行解耦,將那些經(jīng)常變化的“內(nèi)容”抽象出來,在外部分別實(shí)現(xiàn)。

下面列舉DVCon上的兩篇策略模式實(shí)際應(yīng)用的文章:

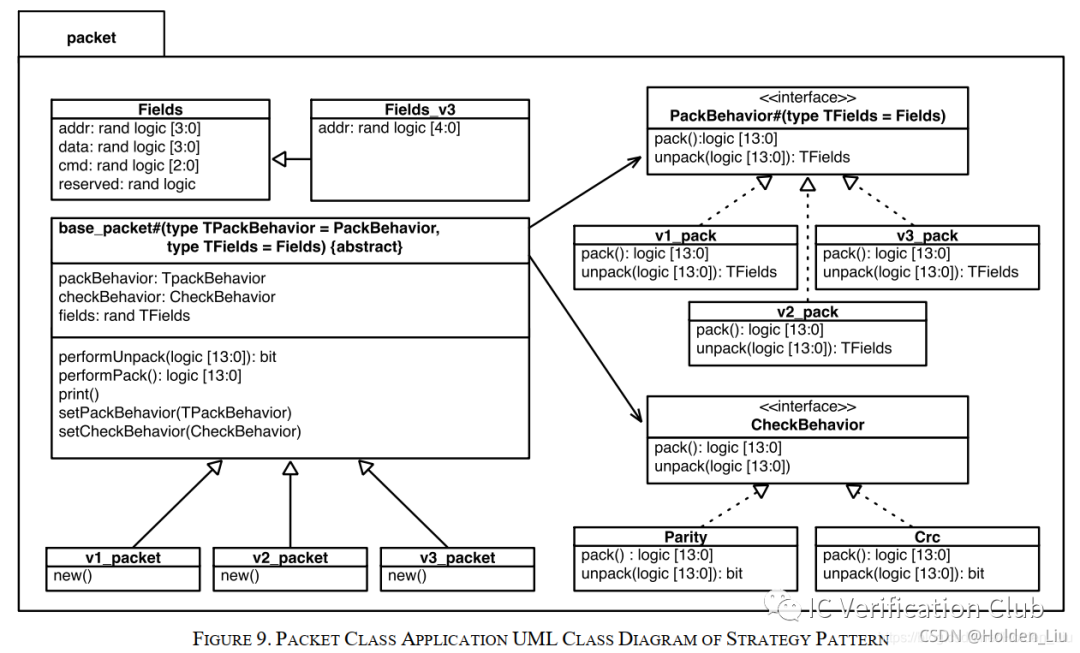

2016 DVCon US : Design Patterns by Example for SystemVerilog Verification Environments Enabled by SystemVerilog 1800-2012

將PackBehavior和CheckBehaviro這兩個(gè)"行為”從base_packet中拎出來,外部實(shí)現(xiàn)重寫interface class, 構(gòu)建了 v1_pack, v2_pack, v3_pack, Parity, Crc這幾個(gè)類。

根據(jù)不同版本V1,V2,V3繼承base_packet,創(chuàng)建v1_packet, v2_packet, v3_packet類,調(diào)用setPackBehaviro(), setCheckBehaviro()賦予不同的"行為“。

2019 DVCon INDIA : Using Software Design Patterns in Test Bench Development for a Multi-Layer Protocol

和上一篇類似,也是對(duì)packet中的pack_behaviro和check_behavior的操作。業(yè)務(wù)是DSI中的PHY layer。

審核編輯:劉清

-

仿真器

+關(guān)注

關(guān)注

14文章

1016瀏覽量

83638 -

UVM

+關(guān)注

關(guān)注

0文章

181瀏覽量

19139 -

解耦控制

+關(guān)注

關(guān)注

0文章

29瀏覽量

10196 -

UML技術(shù)

+關(guān)注

關(guān)注

0文章

5瀏覽量

1368 -

迭代器

+關(guān)注

關(guān)注

0文章

43瀏覽量

4302

原文標(biāo)題:UVM設(shè)計(jì)模式 ( 四 ) 模板模式、策略模式、default_sequence、uvm_callback

文章出處:【微信號(hào):數(shù)字芯片設(shè)計(jì)工程師,微信公眾號(hào):數(shù)字芯片設(shè)計(jì)工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字IC驗(yàn)證之“什么是UVM”“UVM的特點(diǎn)”“UVM提供哪些資源”(2)連載中...

數(shù)字IC驗(yàn)證之“典型的UVM平臺(tái)結(jié)構(gòu)”(3)連載中...

數(shù)字IC驗(yàn)證之“構(gòu)成uvm測(cè)試平臺(tái)的主要組件”(4)連載中...

什么是uvm?uvm的特點(diǎn)有哪些呢

UVM sequence分層有哪幾種方式呢

談?wù)?b class='flag-5'>UVM中的uvm_info打印

設(shè)計(jì)模式行為型:策略模式

UVM中uvm_config_db機(jī)制背后的大功臣

如何用Verdi查看UVM環(huán)境中的變量?

UVM中uvm_config_db機(jī)制背后的大功臣

UVM設(shè)計(jì)中的sequence啟動(dòng)方式有哪幾種呢?

行為型設(shè)計(jì)模式在UVM中的應(yīng)用有哪些呢?

行為型設(shè)計(jì)模式在UVM中的應(yīng)用有哪些呢?

評(píng)論