處理器、內(nèi)存發(fā)展速度不均衡,“存儲墻”如今成為數(shù)據(jù)計(jì)算一大障礙。隨著近幾年云計(jì)算和人工智能應(yīng)用的發(fā)展,面對計(jì)算中心的數(shù)據(jù)洪流,數(shù)據(jù)搬運(yùn)慢、搬運(yùn)能耗大等問題成為了計(jì)算的關(guān)鍵瓶頸。在過去二十年,處理器性能速度提升遠(yuǎn)超內(nèi)存性能提升,長期下來,不均衡的發(fā)展速度造成了當(dāng)前的存儲速度嚴(yán)重滯后于處理器的計(jì)算速度。

在傳統(tǒng)計(jì)算機(jī)的設(shè)定里,存儲模塊是為計(jì)算服務(wù)的,因此設(shè)計(jì)上會考慮存儲與計(jì)算的分離與優(yōu)先級。從處理單元外的存儲器提取數(shù)據(jù),搬運(yùn)時間往往是運(yùn)算時間的成百上千倍,整個過程的無用能耗大概在60%-90%之間,能效非常低,“存儲墻”成為了數(shù)據(jù)計(jì)算應(yīng)用的一大障礙。

1、消除馮諾依曼計(jì)算架構(gòu)瓶頸,存算一體應(yīng)運(yùn)而生

人工智能應(yīng)用興起,“存儲墻”下存算一體技術(shù)應(yīng)運(yùn)而生。應(yīng)用發(fā)展至今,人工智能的出現(xiàn)驅(qū)動了計(jì)算型存儲/存算一體/存內(nèi)計(jì)算的發(fā)展。人工智能算法的訪存密集(大數(shù)據(jù)需求)和計(jì)算密集(低精度規(guī)整運(yùn)算)的特征和為計(jì)算型存儲/存算一體/存內(nèi)計(jì)算的實(shí)現(xiàn)提供了有力的條件。如今,存儲和計(jì)算不得不整體考慮,以最佳的配合方式為數(shù)據(jù)采集、傳輸和處理服務(wù)。

存算一體(Computing in Memory)是在存儲器中嵌入計(jì)算能力,以新的運(yùn)算架構(gòu)進(jìn)行二維和三維矩陣乘法/加法運(yùn)算。存算一體技術(shù)直接利用存儲器進(jìn)行數(shù)據(jù)處理或計(jì)算,從而把數(shù)據(jù)存儲與計(jì)算融合在同一個芯片的同一片區(qū)之中,可以徹底消除馮諾依曼計(jì)算架構(gòu)瓶頸。存算一體的優(yōu)勢是打破存儲墻,消除不必要的數(shù)據(jù)搬移延遲和功耗,并使用存儲單元提升算力,成百上千倍的提高計(jì)算效率,降低成本。 存算一體有近內(nèi)存計(jì)算(NMC)、存儲級內(nèi)存(SCM)、近存儲計(jì)算(NSC)及存內(nèi)計(jì)算(IMC)等技術(shù)方向。 近內(nèi)存計(jì)算(NMC):“捆綁”緩存+內(nèi)存,通常會選用3D封裝,利用TSV(硅通孔技術(shù))實(shí)現(xiàn)垂直通信,但成本高,不同型號的芯片帶還要匹配大小,進(jìn)行預(yù)設(shè)計(jì)和流片。在以上工作的基礎(chǔ)之上,還要考慮通用性問題,它適用于AI,機(jī)器學(xué)習(xí)和數(shù)據(jù)中心等規(guī)模型應(yīng)用需求。另一種是2.5D封裝,主流技術(shù)是HBM(高帶寬內(nèi)存),與平面板級連線不同,加入了interposer這種特殊有機(jī)材料(線寬,節(jié)點(diǎn)間距優(yōu)于電路板)作為中間轉(zhuǎn)接層,它像一個有底座的硅芯片,CPU周邊增加很多“凹槽”,連接多個HBM(DRAM芯片)堆棧實(shí)現(xiàn)高密度和高帶寬。

存儲級內(nèi)存(SCM):常見的是由英特爾和美光推出的3D Xpoint,基于相變存儲技術(shù),速度介于SSD和內(nèi)存之間,目前可以和DRAM配合使用,適用于規(guī)模型應(yīng)用場景。 近存儲計(jì)算(NSC):將SSD控制器加上計(jì)算功能,或者讓擁有計(jì)算模塊的FPGA來處理數(shù)據(jù)并且充當(dāng)閃存控制器,不通過CPU進(jìn)行讀取計(jì)算,而是直連存儲器和計(jì)算,以此提升計(jì)算效率。

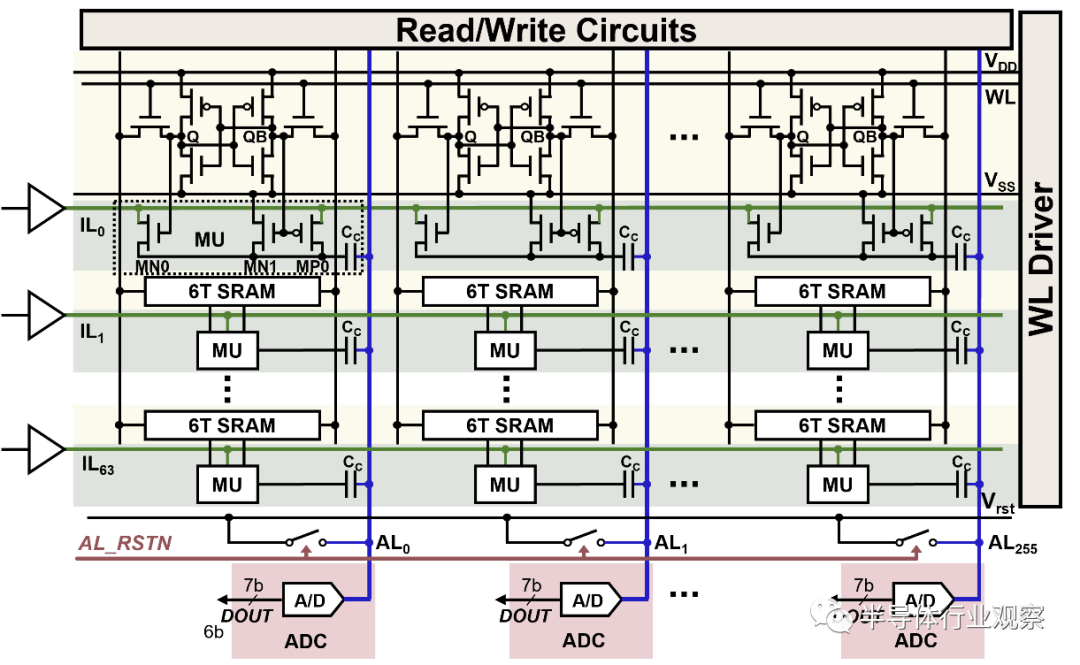

存內(nèi)計(jì)算(IMC):利用存儲器的單元模擬特性做計(jì)算。CPU是二進(jìn)制邏輯計(jì)算,而存內(nèi)計(jì)算則是利用存儲器內(nèi)電阻特性進(jìn)行計(jì)算,不只是用來區(qū)分電阻高低,而是通過電阻值來區(qū)分多種狀態(tài),僅僅用一個晶體管就可以完成一次乘法計(jì)算過程。

2、成熟存儲介質(zhì)、新型存儲介質(zhì)齊發(fā)展

存算一體有Flash、SRAM、DRAM等成熟存儲介質(zhì),同時ReRAM、MRAM等新型存儲介質(zhì)也在快速發(fā)展。根據(jù)存儲介質(zhì)的不同,存內(nèi)計(jì)算芯片可分為基于傳統(tǒng)存儲器和基于新型非易失性存儲器兩種。

傳統(tǒng)存儲器包括SRAM,DRAM和Flash等;新型非易失性存儲器包括ReRAM,PCM,F(xiàn)eFET,MRAM等。其中,距離產(chǎn)業(yè)化較近的是基于NOR Flash和基于SRAM的存內(nèi)計(jì)算芯片。

3、HBM:HBM技術(shù)下,DRAM由2D轉(zhuǎn)為3D

HBM(High Bandwidth Memory)即高帶寬存儲器,按照J(rèn)EDEC的分類,HBM屬于GDDR內(nèi)存的一種,其通過使用先進(jìn)的封裝方法(如TSV硅通孔技術(shù))垂直堆疊多個DRAM,并與GPU封裝在一起。業(yè)界希望通過增加存儲器帶寬解決大數(shù)據(jù)時代下的“內(nèi)存墻”問題,HBM便應(yīng)運(yùn)而生。存儲器帶寬是指單位時間內(nèi)可以傳輸?shù)臄?shù)據(jù)量,要想增加帶寬,最簡單的方法是增加數(shù)據(jù)傳輸線路的數(shù)量。

據(jù)悉,典型的DRAM芯片中,每個芯片有八個DQ數(shù)據(jù)輸入/輸出引腳,組成DIMM模組單元之后,共有64個DQ引腳。而HBM通過系統(tǒng)級封裝(SIP)和硅通孔(TSV)技術(shù),擁有多達(dá)1024個數(shù)據(jù)引腳,可顯著提升數(shù)據(jù)傳輸速度。HBM技術(shù)之下,DRAM芯片從2D轉(zhuǎn)變?yōu)?D,可以在很小的物理空間里實(shí)現(xiàn)高容量、高帶寬、低延時與低功耗,因而HBM被業(yè)界視為新一代內(nèi)存解決方案。

4、HBM:較傳統(tǒng)GDDR帶寬、功耗等性能優(yōu)勢明顯

更高速、更高帶寬:最新的HBM3的帶寬最高可以達(dá)到819 GB/s,而最新的GDDR6的帶寬最高只有96GB/s,CPU和硬件處理單元的常用外掛存儲設(shè)備DDR4的帶寬更是只有HBM的1/10。 更高位寬:采用3D堆疊技術(shù)之后,其下方互聯(lián)的觸點(diǎn)數(shù)量遠(yuǎn)遠(yuǎn)多于DDR內(nèi)存連接到CPU的線路數(shù)量。從傳輸位寬的角度來看,4層DRAM裸片高度的HBM內(nèi)存總共就是1024 bit位寬。很多GPU、CPU周圍都有4片這樣的HBM內(nèi)存,則總共位寬就是4096bit。

更低功耗:HBM 重新調(diào)整內(nèi)存的功耗效率,使每瓦帶寬比GDDR5高出3倍多,即功耗降低3倍多。 更小外形:GDDR作為獨(dú)立封裝,在PCB上圍繞在處理器的周圍,而HBM則排布在硅中階層(Silicon Interposer)上并和GPU封裝在一起,面積一下子縮小了很多,比如HBM2比GDDR5節(jié)省了94%的表面積。 HBM發(fā)展至今第四代性能不斷突破。自2014年首款硅通孔HBM產(chǎn)品問世至今,HBM技術(shù)已經(jīng)發(fā)展至第四代,分別是:HBM(第一代)、HBM2(第二代)、HBM2E(第三代)、HBM3(第四代),HBM芯片容量從1GB升級至24GB,帶寬從128GB/s提升至819GB/s,數(shù)據(jù)傳輸速率也從1Gbps提高至6.4Gbps

AIGC浪潮下AI服務(wù)器采購量增長,催生HBM需求量今年增近六成。2023年爆款A(yù)IGC應(yīng)用帶動AI服務(wù)器成長熱潮,大型云端企業(yè)紛紛積極布局,包含Microsoft、Google、AWS、字節(jié)跳動、百度等企業(yè)陸續(xù)采購高端AI服務(wù)器,以持續(xù)訓(xùn)練及優(yōu)化其AI分析模型。TrendForce預(yù)估今年AI服務(wù)器出貨量年增率可望達(dá)15.4%,2023~2027年AI服務(wù)器出貨量年復(fù)合成長率約12.2%。 高端AI服務(wù)器需采用的高端AI芯片,相較于一般服務(wù)器而言,AI服務(wù)器多增加GPGPU的使用,以NVIDIA A100 80GB配置4或8張計(jì)算,HBM用量約為320~640GB。未來在AI模型逐漸復(fù)雜化的趨勢下,將推升2023-2024年高帶寬存儲器(HBM)的需求。 TrendForce預(yù)估2023年全球HBM需求量將年增近六成,來到2.9億GB,2024年將再成長三成。根據(jù)Mordor Intelligence,2020年高帶寬內(nèi)存市場價(jià)值為 10.682 億美元,預(yù)計(jì)到2026年將達(dá)到40.885億美元,在2021-2026年預(yù)測期間的復(fù)合年增長率為25.4%。在近期的業(yè)績會上,SK海力士表示目前其HBM的銷量占比還不足營收1%,但今年銷售額占比有望成長到10%,同時預(yù)計(jì)在明年應(yīng)用于AI服務(wù)器的HBM和DDR5的銷量將翻一番。 HBM價(jià)值量顯著敢于標(biāo)準(zhǔn)DRAM,成為新利潤增長點(diǎn)。芯片咨詢公司 SemiAnalysis 表示,HBM的價(jià)格大約是標(biāo)準(zhǔn)DRAM芯片的五倍,為制造商帶來了更大的總利潤。目前,HBM占全球內(nèi)存收入的比例不到5%,但SemiAnalysis預(yù)計(jì)到2026年將占到總收入的20%以上。

SK海力士首席財(cái)務(wù)官Kim Woo-hyun 在4月份的財(cái)報(bào)電話會議上表示預(yù)計(jì)2023年HBM收入將同比增長50%以上。

5、CXL:PCIe應(yīng)對海量數(shù)據(jù)面臨瓶頸

PCI-Express簡稱PCIE,是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于擴(kuò)充計(jì)算機(jī)系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。PCIE本質(zhì)上是一種全雙工的的連接總線,傳輸數(shù)據(jù)量的大小由通道數(shù)lane決定的。 一般,1個連接通道lane稱為X1,每個通道lane由兩對數(shù)據(jù)線組成,一對發(fā)送,一對接收,每對數(shù)據(jù)線包含兩根差分線。即X1只有1個lane,4根數(shù)據(jù)線,每個時鐘每個方向1bit數(shù)據(jù)傳輸,依次類推。CPU通過主板上的PCIe插槽及PCIe協(xié)議與加速器溝通,實(shí)現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送,并在高時鐘頻率下保持高性能。

即使每代PCIe性能升級,但面對海量數(shù)據(jù)仍有壓力。每一代PCIe的吞吐量都翻番,2019年5月底公布的PCIe 5.0,其以32Gb/s的單通道帶寬與32GT/s每通道數(shù)據(jù)傳輸速率,滿足了現(xiàn)今絕大多數(shù)的需求。但應(yīng)對數(shù)據(jù)TB級增長、異構(gòu)計(jì)算大行其道的當(dāng)下,PCIe在內(nèi)存使用效率、延遲和數(shù)據(jù)吞吐量等方面,已經(jīng)面臨壓力。

6、CXL:PCIe技術(shù)乏力,CXL旨在解決內(nèi)存墻和IO墻問題

PCIe技術(shù)逐漸乏力,CXL旨在解決存儲墻和IO墻問題。現(xiàn)代處理器性能的不斷提升,而內(nèi)存與算力之間的技術(shù)發(fā)展差距卻不斷增大。在過去的20多年中,處理器的性能以每年大約55%速度快速提升,而內(nèi)存性能的提升速度則只有每年10%左右。面臨摩爾定律的壓力,當(dāng)代內(nèi)存容量擴(kuò)展速度逐年減緩,成本卻愈發(fā)高昂。隨著大數(shù)據(jù)AI、機(jī)器學(xué)習(xí)等應(yīng)用爆發(fā),英特爾二十年前開創(chuàng)的PCIe(PCI Express)技術(shù)逐漸乏力,內(nèi)存墻和IO墻成為兩個不可逾越的瓶頸,基于PCI-e協(xié)議的CXL技術(shù)便在此環(huán)境下出現(xiàn)。 存儲墻:現(xiàn)代計(jì)算系統(tǒng)通常采取高速緩存(SRAM)、主存(DRAM)、外部存儲(NAND Flash)的三級存儲結(jié)構(gòu)。每當(dāng)應(yīng)用開始工作時,就需要不斷地在內(nèi)存中來回傳輸信息。SRAM響應(yīng)時間通常在納秒級,DRAM則一般為100納秒量級,NAND Flash更是高達(dá)100微秒級,當(dāng)數(shù)據(jù)在這三級存儲間傳輸時,后級的響應(yīng)時間及傳輸帶寬都將拖累整體的性能,形成“存儲墻”。

IO墻:以AI為例,AI模型的大小基本上每兩年上升一個數(shù)量級,內(nèi)存中的數(shù)據(jù)可以較快訪問,但超出內(nèi)存后數(shù)據(jù)就需要放在外部存儲里,用網(wǎng)絡(luò)IO來訪問數(shù)據(jù)。IO方式的訪問會使得訪問速度嚴(yán)重下降,當(dāng)數(shù)據(jù)量過于龐大內(nèi)存容量不夠時,IO也不可避免地會成為應(yīng)用的瓶頸。

7、CXL:具有極高兼容性和內(nèi)存一致性的全新互聯(lián)技術(shù)標(biāo)準(zhǔn)

CXL作為一種全新的互聯(lián)技術(shù)標(biāo)準(zhǔn),具有極高兼容性和內(nèi)存一致性。CXL全稱為Compute Express Link,2019年英特爾推出了CXL技術(shù),其能夠讓CPU與GPU、FPGA或其他加速器之間實(shí)現(xiàn)高速高效的互聯(lián),從而滿足高性能異構(gòu)計(jì)算的要求,并且其維護(hù)CPU內(nèi)存空間和連接設(shè)備內(nèi)存之間的一致性。

CXL硬件加軟件的生態(tài)環(huán)境里,已經(jīng)涌現(xiàn)了一大批公司。CXL聯(lián)盟于2019年3月由創(chuàng)始成員阿里巴巴集團(tuán)、思科系統(tǒng)、戴爾易安信、Meta、谷歌、惠普企業(yè)(HPE)、華為、英特爾公司和微軟組成。此后,AMD、NVIDIA、三星、Arm、瑞薩、IBM、Keysight、Synopsys、Marvell等以各種身份加入。2021、2022年Gen-Z技術(shù)和OpenCAPI技術(shù)相繼加入,CXL聯(lián)盟一統(tǒng)I/O互連標(biāo)準(zhǔn)。

8、CXL:1.1/2.0/3.0三代標(biāo)準(zhǔn),從單機(jī)到多層交互

CXL是基于 PCIe 5.0發(fā)展而來,過去四年時間CXL已經(jīng)發(fā)表了1.0/1.1、2.0、3.0三個不同的版本。 CXL 1.1:2019年,CXL的第一個版本CXL 1.1問世了。它主要定義的標(biāo)準(zhǔn)是如何直接連接一臺服務(wù)器里計(jì)算器件和內(nèi)存器件,它主要的場景是對內(nèi)存的容量和帶寬進(jìn)行擴(kuò)展,即Memory Expansion。 CXL 2.0:下圖中H1到H4到Hn指不同Host,它可以通過CXL Switch連接多個設(shè)備, D1到D4到Dn指的是不同的內(nèi)存,也是通CXLSwitch連到上層的主機(jī)里。CXL 2.0不僅解決單機(jī)設(shè)備的問題,更是使Memory Pooling成為可能。這套框架下,可以跨系統(tǒng)設(shè)備實(shí)現(xiàn)共享內(nèi)存池,大大提高內(nèi)存的使用率,增加靈活性,同時降低內(nèi)存的使用成本。

CXL 3.0:2022年8月份發(fā)布的新標(biāo)準(zhǔn),在CXL 2.0基礎(chǔ)上增加了一些重要功能,它可以使得多個Switch互相連接,可以使得上百個服務(wù)器互聯(lián)并共享內(nèi)存。除了多層交互以外,CXL 3.0還多Memory sharing的能力,突破了某一個物理內(nèi)存只能屬于某一臺服務(wù)器的限制,在硬件上實(shí)現(xiàn)了多機(jī)共同訪問同樣內(nèi)存地址的能力。 技術(shù)路線圖明確,至少2023年H2才有CXL 1.0/1.1的產(chǎn)品落地。已經(jīng)有不少公司宣布將支持CXL,包括AMD、英特爾的下一代服務(wù)器芯片,內(nèi)存廠商三星、海力士、美光均宣布了支持CXL的內(nèi)存產(chǎn)品,但真正的產(chǎn)品仍需至少2023年H2才能推出。2024年上半年,CXL1.1和CXL 2.0的產(chǎn)品可能會有落地產(chǎn)品,CXL 3.0的落地還需要更長時間。

責(zé)任編輯:彭菁

-

模塊

+關(guān)注

關(guān)注

7文章

2671瀏覽量

47342 -

存儲

+關(guān)注

關(guān)注

13文章

4264瀏覽量

85675 -

計(jì)算

+關(guān)注

關(guān)注

2文章

445瀏覽量

38736 -

人工智能

+關(guān)注

關(guān)注

1791文章

46867瀏覽量

237590 -

存算一體

+關(guān)注

關(guān)注

0文章

100瀏覽量

4288

原文標(biāo)題:計(jì)算架構(gòu)升級,新興技術(shù)應(yīng)用而生

文章出處:【微信號:架構(gòu)師技術(shù)聯(lián)盟,微信公眾號:架構(gòu)師技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

比存算一體更進(jìn)一步,“感存算一體化”前景如何?

探索存內(nèi)計(jì)算—基于 SRAM 的存內(nèi)計(jì)算與基于 MRAM 的存算一體的探究

存算一體技術(shù)路線如何選

談?wù)剻C(jī)電一體化技術(shù)的現(xiàn)狀及發(fā)展趨勢

存算一體技術(shù)未來的整體趨勢如何

2023年存算一體是芯片設(shè)計(jì)的技術(shù)趨勢

巨頭紛紛布局存算一體,各種存儲介質(zhì)的優(yōu)勢分析

如何選擇存儲器類型 存算一體芯片發(fā)展趨勢

存算一體化與邊緣計(jì)算:重新定義智能計(jì)算的未來

存算一體技術(shù)發(fā)展趨勢 存儲與計(jì)算的分離與優(yōu)先級關(guān)系

存算一體技術(shù)發(fā)展趨勢 存儲與計(jì)算的分離與優(yōu)先級關(guān)系

評論