FPGA廠商提供了豐富的IP核,基礎性IP核都是可以直接免費調用的,比如FIFO、RAM等等。

本文主要介紹FIFO的一些基礎知識,幫助大家能夠理解FIFO的基礎概念。

一、FIFO介紹

FIFO全稱是First In First Out,即先進先出。

FIFO是一個數據緩存隊列,主要特點就是數據順序寫入,再按照同樣的順序輸出數據,即先進去的數據先被取出來。

1、FIFO的通俗理解

FIFO可以類比一個水池。

當寫通道打開時,就相當于往水池里加水;而當讀通道打開時,就相當于從水池中放水。

如果持續不斷地加水和放水,如果加水速度超過了放水速度,那么水池就會滿了,這時FIFO就會發生溢出,水會溢出水池。

相反,如果放水速度快于加水速度,那么水池就會變空,FIFO就會出現空的情況。

2、FIFO的分類

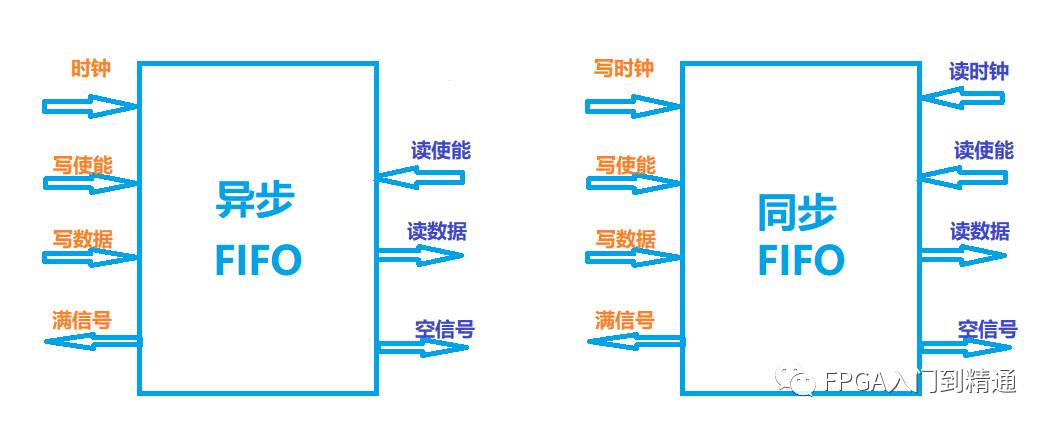

根據FIFO輸入時鐘的區別,可以分為同步FIFO和異步FIFO。

同步 FIFO 只有一個獨立的時鐘端口 clock,所有的輸入輸出信號都同步于 clock 信號。

異步FIFO有兩個時鐘,寫端口和讀端口分別有獨立的時鐘,所有寫相關的信號都是屬于寫時鐘,所有與讀相關的信號都屬于讀時鐘。

3、FIFO IP

FIFO一般不需要自己去寫代碼實現,FPGA官方軟件都提供了FIFO IP,直接使用即可。

FPGA IP特性:

- 配置選項和控制手段廣泛:提供了豐富的配置選項和控制手段,可以根據用戶的需求進行靈活配置。

- 靈活的接口和支持多種數據寬度:接口設計靈活,同時支持多種不同數據寬度的操作。

- 支持多種讀寫模式:支持單寫單讀、單寫多讀、多寫單讀、多寫多讀等讀寫模式,可以適應不同的應用場景。

- 多種存儲方式:支持異步、同步等不同的存儲方式,可以根據需求選擇合適的存儲方式。

- 可配置的參數:可以配置深度、寬度、讀寫數據寬度等參數,使得用戶可以按需定制FIFO的特性。

二、FIFO的應用

FIFO的應用非常廣泛,其中同步fifo主要用于處理數據緩存,異步fifo主要用于處理跨時鐘數據傳輸處理。

常用的應用場景如下:

接口數據/消息緩沖:FIFO可以用于緩存數據或消息,以應對數據流量突發情況,同時降低或消除背壓的頻率,減小上級模塊的復雜度。

接口協議隔離:在模塊與復雜的協議進行對接時,FIFO可以作為隔離后的用戶接口,降低模塊接口協議設計復雜度,并實現協議接口的IP化,提高系統的復用性。

跨時鐘域處理:FIFO可以用于處理異步時鐘域的數據、消息和總線。通過FIFO,可以實現簡單、快速、安全的跨時鐘域處理。

數據位寬轉換:FIFO可以用于實現數據的位寬轉換,例如從512位轉換為256位。

三、FIFO的重要概念

1、主要端口

讀寫時鐘:同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。異步FIFO讀寫時鐘是獨立的兩個時鐘。

讀寫使能:讀寫控制的使能

滿信號:FIFO里面的緩存數據數量達到了最大深度值

空信號:FIFO里面的緩存全部被讀空

深度:FIFO所能容納的最大數據數量

2、FIFO的存儲結構

FIFO通常采用循環存儲結構,即存儲空間是一個環形的緩沖區。

數據寫入時,從第一個寫入地址開始,依次向后寫入;數據讀取時,從第一個讀取地址開始,依次向后讀取。

當寫入數據量達到FIFO的深度時,將不能再寫入數據,此時需要停止寫入操作,等待讀取操作將數據讀出,否則將發生溢出。

同樣,當讀取數據量達到FIFO的深度時,將不能再讀取數據,此時需要停止讀取操作,等待寫入操作將數據寫入。

3、FIFO的空滿狀態

FIFO具有空標志和滿標志,用于指示FIFO的存儲狀態。

當FIFO空時,寫入操作將停止,直到FIFO非空;當FIFO滿時,讀取操作將停止,直到FIFO非滿。

空滿狀態的判斷通常采用比較讀寫指針的位置關系,例如當寫入指針等于讀取指針時,FIFO為空;當寫入指針比讀取指針多一位(達到FIFO的深度)時,FIFO為滿。

4、FIFO的讀寫操作

FIFO的讀寫操作遵循先進先出的原則。

寫入數據時,根據寫地址將數據寫入FIFO的空閑位置;讀取數據時,根據讀地址從FIFO的存儲位置讀取數據。

在連續的讀寫操作中,讀寫指針會自動遞增,以便在下次讀寫時正確指向FIFO的下一個位置。

5、FIFO的同步處理

由于FIFO通常涉及不同時鐘域之間的數據傳輸,因此需要進行同步處理。

在異步FIFO中,寫入時鐘和讀取時鐘是不同的,需要使用握手協議進行同步。

在同步FIFO中,讀寫時鐘是同一個時鐘,但仍然需要進行時序分析,以保證數據的穩定性和可靠性

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602034 -

fifo

+關注

關注

3文章

387瀏覽量

43561 -

IP核

+關注

關注

4文章

326瀏覽量

49432 -

數據緩存

+關注

關注

0文章

23瀏覽量

7051

發布評論請先 登錄

相關推薦

FIFO的一些基礎知識

FIFO的一些基礎知識

評論