什么是SPI?

SPI的英文全稱為Serial Peripheral Interface,顧名思義為串行外設接口。SPI是一種同步串行通信接口規(guī)范,主要應用于嵌入式系統(tǒng)中的短距離通信。該接口由摩托羅拉在20世紀80年代中期開發(fā),后發(fā)展成了行業(yè)規(guī)范。

SPI簡介?

SPI是一種高速的、全雙工的、同步的通信總線,并且至多僅需使用4根線,節(jié)約了芯片的管腳,SPI主要應用于EEPROM、FLASH、ADC、DAC等芯片,還有數(shù)字信號處理器和數(shù)字信號解碼器之間。

SPI設備之間采用全雙工模式通信,是一個主機和一個或者多個從機的主從模式。主機負責初始化幀,這個數(shù)據(jù)傳輸幀可以用于讀與寫兩種操作,片選線可以從多個從機選擇一個來響應主機的請求。

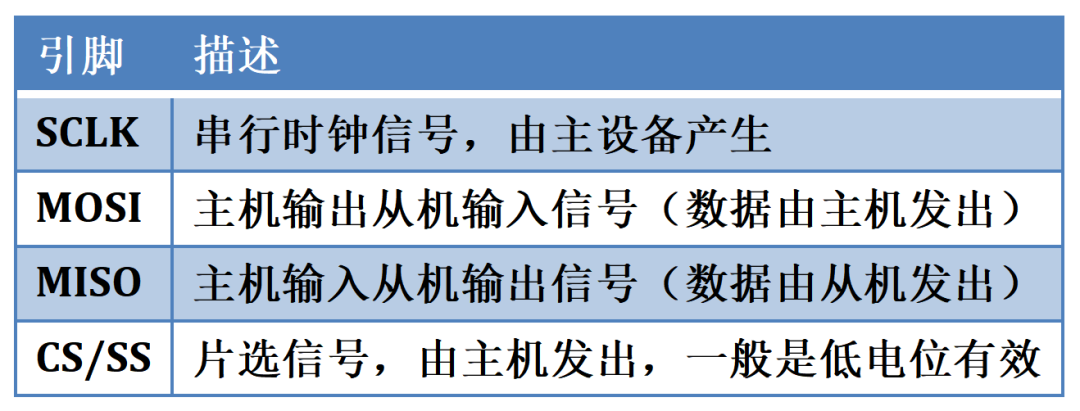

SPI接口定義如下表:

由上表也可以看出當SPI設備間通信時,數(shù)據(jù)線應該是MOSI連接MOSI,MISO連接MISO,SCLK與SCLK相連,而不是像串口那樣TX、RX進行反接。當只有單一SPI從機設備時,如果從機設備允許的話,可直接將CS/SS線固定在低電平。然而類似于MAX1242這款需要CS/SS線的下降沿來觸發(fā)的芯片,則必須將CC/SS線與主機相連。如下圖,為一主一從連接方式。

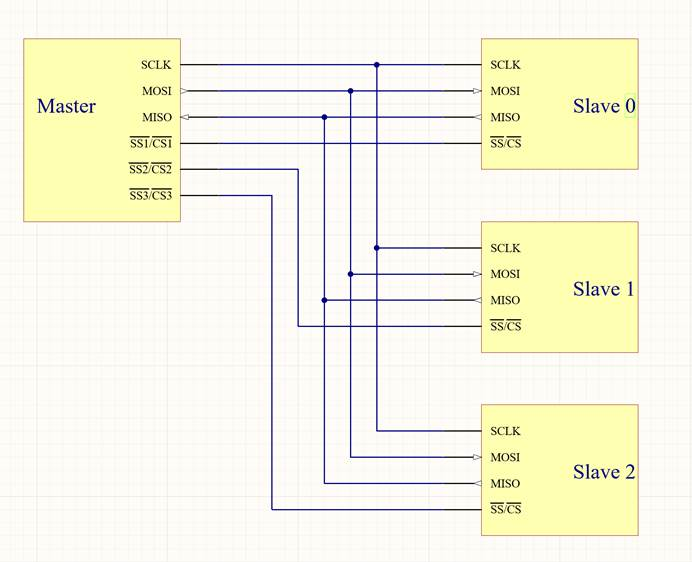

對于多個從機設備時,則每個從機都需要一根CS/SS線來與主機相連,從而達到主機能與任一從機通信的目的。如下圖,為一主多從的連接方式。

大多數(shù)從機設備都有著三態(tài)邏輯的特性,因此當設備未被選中時,它們的MISO信號線會變成高阻抗狀態(tài)(電氣斷開)。沒有三態(tài)輸出的設備則需外接三態(tài)緩沖器才能與其他的從機設備共享SPI總線。

數(shù)據(jù)傳輸

在SPI通信中,SPI主機設備以從機設備支持的頻率通過SCLK線給到SPI從機設備,這點也意味著從機是無法主動向主機發(fā)送數(shù)據(jù)的,只能主機輪詢向從機發(fā)或者從機設備主動通過一個IO口來告知主機數(shù)據(jù)到達。

在SPI每個時鐘周期內(nèi),都會進行一次全雙工數(shù)據(jù)的傳輸。主機通過MOSI線上發(fā)送1bit時,從機也會在讀取到之后通過MISO線發(fā)送1bit數(shù)據(jù)出去。這說明,即使只進行單工通信,也會保持此通信順序。

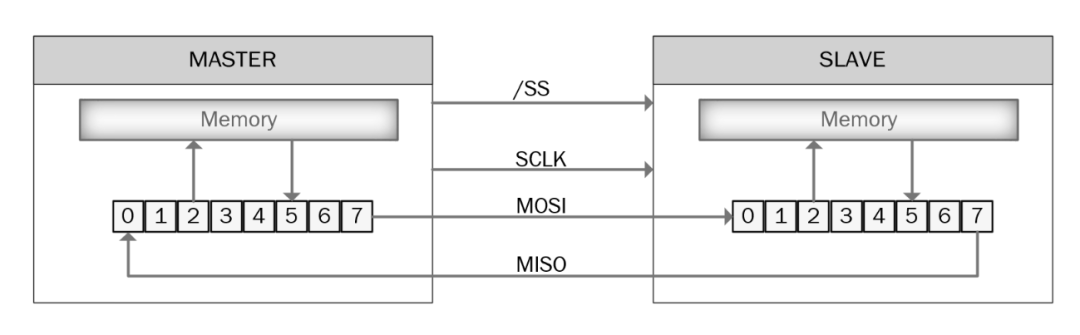

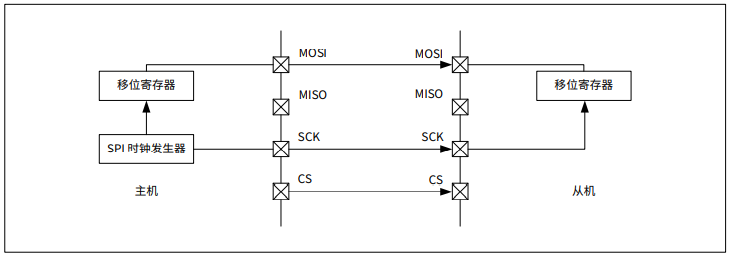

SPI傳輸通常涉及到兩個給定了字長的移位寄存器。例如在主機、從機中的8bit的移位寄存器。它們以虛擬環(huán)形拓撲連接,數(shù)據(jù)通常先從最高有效位被移出。在時鐘沿,主機和從機都移出1bit數(shù)據(jù)從傳輸線上給到對方。在下一個時鐘邊沿來到時,雙方的接收器再對傳輸線上的該bit進行采樣,并將其設置為移位寄存器的新的最低有效位。在寄存器位被移出和移入后,主機和從機交換了寄存器值。如果需要交換更多數(shù)據(jù),則重新加載移位寄存器并重復該過程。傳輸可以持續(xù)任意數(shù)量的時鐘周期。完成后,主機停止切換時鐘信號。如下圖,為主從機之間的交互時的移位寄存器示意圖。

其中上圖的通信流程如下:

1.SPI主機首先現(xiàn)將SS或CS線拉低,以此來告知SPI從機通信開始。

2. 主機通過發(fā)送SCLK時鐘信號,來告知從機即將進行的讀寫操作。這里的SCLK時鐘信號是由SPI的模式來決定是高電平還是低電平有效的,這點在稍后會進行介紹。

3. 主機(Master)將要發(fā)送的數(shù)據(jù)寫到發(fā)送數(shù)據(jù)緩存區(qū)(Memory),緩存區(qū)經(jīng)過移位寄存器(0~7),串行移位寄存器通過MOSI信號線將字節(jié)一位一位的移出去傳送給從機,同時MISO接口接收到的數(shù)據(jù)經(jīng)過移位寄存器一位一位的移到接收緩存區(qū)。

4.從機(Slave)也將自己的串行移位寄存器(0~7)中的內(nèi)容通過MISO信號線返回給主機。同時通過MOSI信號線接收主機發(fā)送的數(shù)據(jù),這樣,兩個移位寄存器中的內(nèi)容就被交換。

SPI通信的4種工作模式

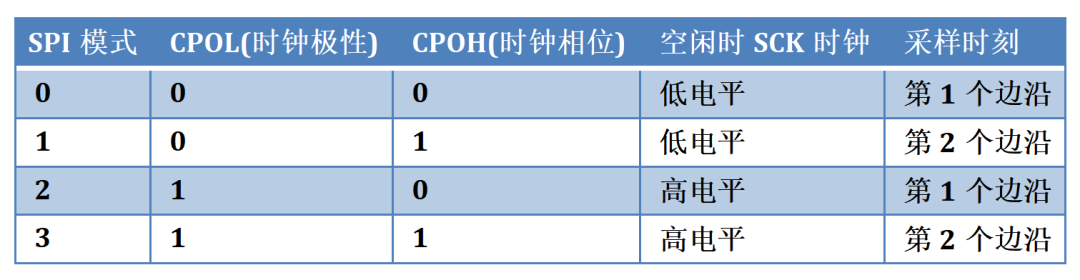

SPI通信中有4種不同的操作模式,不同的從機設備可能在出廠時就被設置好了某種模式,并且無法更改。但是SPI通信必須處于同一種模式下才能進行。因此我們應該對自己手里的SPI主機設備進行模式的配置,也就是通過CPOL(時鐘極性)和CPHA(時鐘相位)來控制SPI主設備的通信模式,具體如下:

時鐘極性(CPOL)定義了SCLK時鐘線空閑狀態(tài)時的電平:

1.CPOL=0,即SCLK=0,表示SCLK時鐘信號線在空閑狀態(tài)時的電平為低電平,因此有效狀態(tài)為高電平。

2. CPOL=1,即SCLK=1,表示SCLK時鐘信號線在空閑狀態(tài)時的電平為高電平,因此有效狀態(tài)為低電平。

時鐘相位(CPHA)定義了數(shù)據(jù)位相對于時鐘線的時序(即相位):

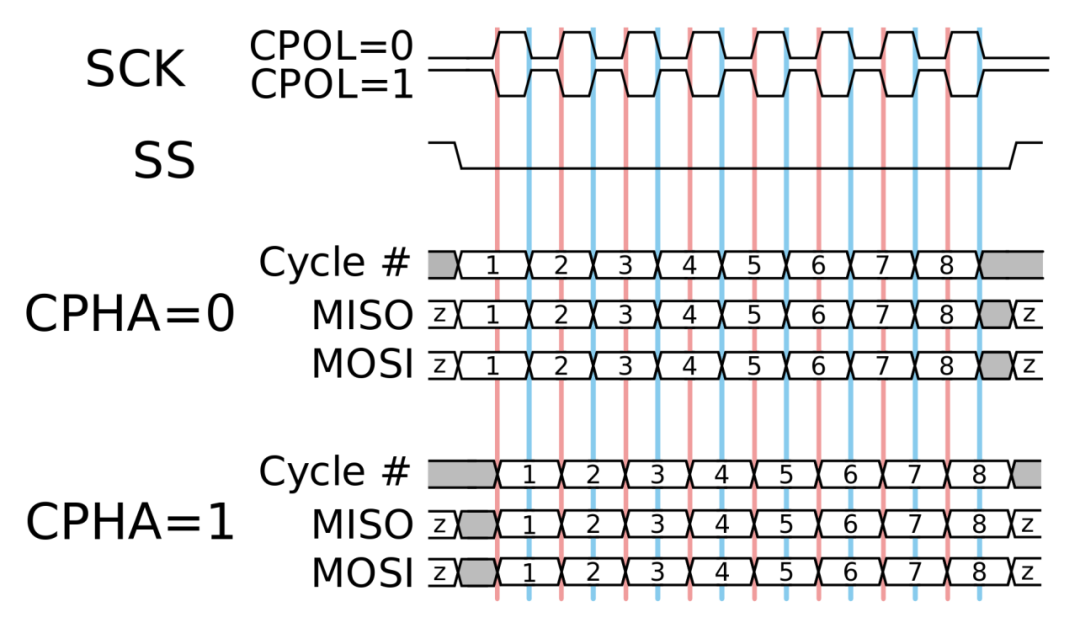

1. CPHA=0,即表示輸出(out)端在上一個時鐘周期的后沿改變數(shù)據(jù),而輸入(in)端在時鐘周期的前沿(或不久之后)捕獲數(shù)據(jù)。輸出端保持數(shù)據(jù)有效直到當前時鐘周期的尾部邊緣。對于第一個時鐘周期來說,第一位的數(shù)據(jù)必須在時鐘前沿之前出現(xiàn)在MOSI線上。也就是一個CPHA=0的周期包括半個時鐘空閑和半個時鐘置位的周期。

2. CPHA=1,即表示輸出(out)端在當前時鐘周期的前沿改變數(shù)據(jù),而輸入(in)端在時鐘周期的后沿(或不久之后)捕獲數(shù)據(jù)。輸出端保持數(shù)據(jù)有效直到下一個時鐘周期的前沿。對于最后一個時鐘周期來說,從機設備在片選信號消失之前保持MISO信號線有效。也就是一個CHPA=1的周期包括半個時鐘置位和半個時鐘空閑的周期。

注意:此處的前沿和后沿的意思表示在每個周期中第一個出現(xiàn)的邊沿和最后一個出現(xiàn)的邊沿。總的來說則為:當時鐘為正向時鐘時,時鐘線的上升沿為前沿,時鐘的下降沿為后沿,反之。

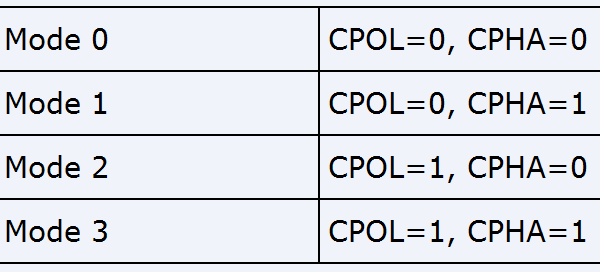

如下表,為SPI通信的4種模式:

下圖顯示了時鐘極性和相位的時序圖。紅線表示時鐘的前沿,藍線表示時鐘的后沿。

SPI協(xié)議的優(yōu)缺點

SPI的優(yōu)點在于它有著比I2C更高的吞吐量,不被最大時鐘速度所限制,可實現(xiàn)潛在的高速、極為簡單的硬件接口,外圍電路使用的上拉電阻是比I2C協(xié)議更少的,這意味著它具有比I2C的功耗更低、從機的時鐘來源來自主機設備,無需新增精密振蕩器、從機不需要唯一的地址、相對于并行接口而言,使用的引腳數(shù)目大大減少等優(yōu)點。

但同時有著一定的缺點,例如SPI沒有帶內(nèi)尋址、當使用多個不同模式的從機設備時,主機設備切換模式時重新初始化,會使得訪問從機設備速度變慢、SPI從機設備沒有硬件流控,只能通過主機自主的延遲下個時鐘周期到來的時間、僅能在短距離通信等缺點。但能在避免SPI的缺點的方向來應用SPI的話,SPI的優(yōu)點讓它遠遠優(yōu)于其他協(xié)議。

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8526瀏覽量

150863 -

SPI

+關注

關注

17文章

1701瀏覽量

91345 -

串行通信

+關注

關注

4文章

569瀏覽量

35301 -

通信總線

+關注

關注

0文章

44瀏覽量

9844

原文標題:【干貨】超全面!SPI通信協(xié)議詳解

文章出處:【微信號:cdebyte,微信公眾號:億佰特物聯(lián)網(wǎng)應用專家】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

SPI通信的4種工作模式

超詳細的SPI原理和通信模式

SPI的通信原理 SPI的接線實例

SPI通信簡介

簡析SPI,對SPI的簡單代碼編寫,模擬SPI

SPI接口通信協(xié)議詳解:SPI時序、2線、3線、4線SPI及4種常用工作模式

通信協(xié)議(SPI)

什么是SPI?SPI通信的4種工作模式

什么是SPI?SPI通信的4種工作模式

評論