點擊上方藍字關注我們

隨著軟件定義無線電平臺在軍事航空航天領域以及近在一些消費無線電和電子領域的出現,現場可編程邏輯 (FPGA) 作為可重新編程數字信號處理 (DSP) SDR 引擎的用途變得越來越重要。

現場可編程邏輯一直是連接寬帶 A/D 和 D/A 轉換器、數字接收器和通信鏈路等高速外設到嵌入式實時系統中可編程處理器的電路。

FPGA(現場可編程門陣列)特別適合處理時鐘、同步以及馴服這些專用設備所需的其他各種定時電路。此外,FPGA 非常適合數據格式化任務,例如串并轉換、數據打包、時間戳、多路復用和數據包形成。

但它們的 DSP 功能已成為 FPGA 固有的重要功能之一,過去幾年 FPGA 供應商對該技術的工程和營銷投資急劇增加就證明了這一點。

數字信號處理任務

在傳統的軟件無線電接收器系統中,經過轉換和濾波的基帶信號作為時域波形的復雜樣本流發送到 DSP。DSP 必須處理所有解調任務以及基于接收信號分析的更別決策。

信號智能接收器通常通過首先對信號進行頻譜分析來估計使用的調制類型來對信號進行分類,然后應用解調算法來確定是否提取了有用的信息,例如可理解的語音或有意義的數據。

DSP 的其他重要任務包括解密、數據存儲、通道切換、到其他系統的信號路由、記錄??活動以及向操作員發送音頻或數字數據以供收聽或顯示。

在手機基站中,數字信號處理任務的數量隨著每個新通信標準的增加而增加。復雜的數字語音和數據協議的激增需要解碼、卷積、成幀、糾錯和聲碼。

采樣率要求的穩步增加加劇了這些額外任務的處理負載。為了支持寬帶 CDMA 等新應用,DSP 距離天線越來越近。

為了滿足這些需求,DSP 時鐘速率已增加到 200 MHz 以上,并且許多新器件具有兩個或更多硬件乘法器。然而,作為系統中昂貴、耗電的資源之一,限度地減少 DSP 的大量工作負載顯然非常重要。

FPGA 在 SDR 中的作用

在過去五年中,為了適應 DSP 功能,FPGA 在幾個關鍵領域取得了巨大的進步。這些器件的柵極密度很好地遵循摩爾定律,大約每年半增加一倍。近發布的一些設備號稱擁有 1000 萬個門!門陣列通常被構造為配備存儲器并能夠執行數學函數的邏輯單元。這些高密度邏輯單元現在可用于各種基本“”,以支持快速乘法器、用于處理 FFT 處理的塊存儲器以及用于 FIR 濾波器的分布式存儲器。

FPGA 綜合工具現在支持“可參數化”內核,這些內核接受位寬定義并自動生成內核結構以滿足信號處理精度要求,而不會浪費門。

現在可以使用多種前端設計工具來滿足硬件和軟件系統工程師的各種輸入偏好。其中包括框圖系統生成器、原理圖處理器以及用于 Verilog 和 VHDL 的輸入語言編譯器。新模擬器的速度、準確性和易用性簡化了新設計的測試,并限度地減少了調試應用程序所花費的時間。

第三方供應商現在提供 IP 內核,以補充 FPGA 供應商提供的標準內核。這些范圍從完整的 DSP 處理器到高速互聯網調制解調器等特定應用模塊。憑借這些新的商業“現成”功能,FPGA 現在能夠打入通用 ASIC 市場以及 DSP 市場。

更重要的是,FPGA 的數字信號處理能力通常可以勝過通用 DSP。例如,如果寬帶 FIR 數字濾波器在單個時鐘周期內需要 32 個 MAC(乘法/累加運算),則僅具有兩個乘法器的通用 DSP 將遠遠達不到要求。另一方面,FPGA 可以輕松整合 32 個 MAC 內核來處理任務。

靈活且可重復使用

這種基于 COTS 的軟件無線電系統是實現各種應用的理想平臺。通過將新的 FPGA 設計工具和 IP 庫用于這些高度可配置的基于 FPGA 的 COTS 板級產品,系統設計人員可以消除對定制板的需求。由于 FPGA“硬件”可以從根本上重新配置,無需新的電路板設計,因此當前項目中使用的相同產品可以輕松地重新配置以適應未來的應用。

隨著新的軟件無線電算法的開發,它們可以首先在 DSP 上進行測試,利用更廣泛的代碼生成、仿真和優化工具。完成后,該算法可以移植到 FPGA,以實現更好的實時操作或支持許多并行通道的處理負擔。,為了過渡到大批量生產,大多數 FPGA 設計都可以輕松轉換為定制 ASIC 的掩模工具。

雖然重新編程 FPGA 來處理新功能可能比為 DSP 編寫新算法復雜一些,但這種努力程度的差距似乎正在縮小。FPGA 設計工具不再是硬件設計人員的專屬領域,現在越來越廣泛地被軟件工程師使用,確保這一重大技術轉變將代表未來嵌入式系統設計的主流范例。

軟件無線電模塊應用

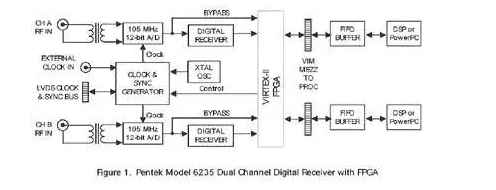

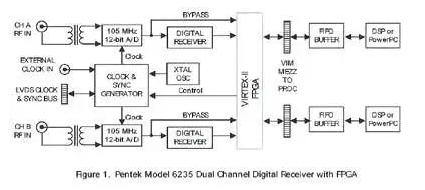

DSP 驅動的 FPGA SDR 平臺的強大功能和靈活性的一個說明性示例(如下圖 1 所示)是連接到四路 DSP 處理器 VME 板的雙通道數字接收器子卡模塊。它包含兩個能夠以高達 100 MHz 采樣率運行的 12 位 A/D 轉換器,以及兩個可轉換和過濾寬帶數字化輸入的選定部分的數字下轉換器。

板載 FPGA 接受兩個 A/D 轉換器的實際輸出以及兩個數字下變頻器的復雜基帶輸出。FPGA 實現 VIM(速度接口夾層)接口,將數據直接傳送到處理器板上的每個 DSP 或 PowerPC,其中 FIFO 緩沖區支持 DMA 塊數據傳輸,速率高達 400 MB/秒。

著眼于添加 DSP 功能,此類平臺中 FPGA 的自然選擇是 Xilinx Virtex-II 系列。XC2V3000 具有 96 個專用 18×18 乘法器模塊和超過 200 KB 的塊 RAM,可提供豐富的信號處理資源組合,甚至適用于一些更重要的應用。

在模塊的基本工廠配置中,FPGA 仍然為板上的各種器件執行傳統的定時、格式化和粘合邏輯任務。由于這些功能相對簡單,因此僅消耗 6% 的可編程邏輯。這使得 94% 的邏輯塊、所有 96 個乘法器以及幾乎整個塊 RAM 可用于添加 DSP 算法。

為了幫助展示這些未開發資源的力量,啟動了一個工程項目來實施高性能 FFT 引擎。由于通信、雷達和信號智能系統都利用 FFT 進行跟蹤、調諧和圖像處理操作,因此 FFT 仍然是的處理器性能基準測試算法之一。

簡而言之,FFT 接受輸入時域樣本塊,并將其轉換為輸出頻域樣本塊。由于計算相當復雜,它消耗了大量DSP處理資源,成為FPGA實現的主要候選者。

構建 FFT

執行 FFT 計算有效的方法之一是 radix-4“蝴蝶”算法的迭代。在每個蝶形內部,四個輸入數據點乘以正弦表中的系數,然后組合起來產生四個輸出點。重復這種蝶形運算,直到處理完所有輸入點,四個,代表一個“階段”。要實現 4,096 點 FFT,需要六級蝶形運算。

與傳統可編程處理器相比,使用 FPGA 計算 FFT 的好處之一是可以同時計算大量乘法器。

在上面的 4,096 示例中,總共需要 60 個乘法器來并行實現所有六個 FFT 蝶形級。由于 XC2V3000 具有 96 個可用乘法器,因此很明顯為什么 FPGA 通常可以顯著優于僅具有兩個或四個硬件乘法器的標準 DSP 處理器,特別是對于 FFT 等算法。

由于 FFT 本質上是一種面向塊的算法,因此當可自由尋址的 RAM 支持快速訪問所有輸入和輸出樣本時,FFT 的運行效率。然而,這種隨機數據可用性的理想模型與來自 A/D 轉換器的順序輸入數據樣本流相反。

幸運的是,FPGA 的可配置塊 RAM 資源可以重組,形成一個存儲器結構,將適當的樣本并行輸入蝶式引擎的四個輸入數據存儲器端口,從而解決數據可用性問題。這種專有的內存架構允許以連續的脈動方式處理后續輸入塊,以便所有六個階段中的所有乘法器都可以始終高效地使用。

對于每個 FPGA 時鐘周期,每個 radix-4 蝶形運算處理四個輸入樣本。因此,當FPGA處理時鐘等于A/D時鐘時,上述架構的運行速度比實時快四倍。通過合適的硬件復用方案,同一 FFT 引擎可用于處理四個輸入數據流,而不是僅一個。

在此示例中,由于兩個 A/D 轉換器和 FPGA 的時鐘頻率均為 100 MHz,因此 FPGA 僅以一半容量工作。但只要付出一點額外的努力,引擎就可以設置為處理兩個通道的 50% 輸入重疊處理,以充分利用硬件。在這種情況下,每個 FFT 的流水線執行時間是驚人的 10.24 微秒!這比以 100 MHz 采樣率收集 4,096 個輸入點所需的時間快四倍,與實時執行四次 FFT 一致。

FFT 增強

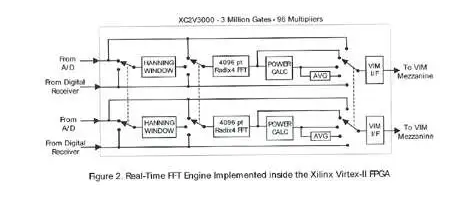

由于 96 個乘法器中僅使用了 60 個用于 FFT 算法,因此結合了其他功能。在四個復數輸入流中的每一個上,都可以應用一個可選的漢寧窗,需要八個額外的乘法器。由于 FFT 和 Hanning 窗的系數使用單獨的 FPGA 表存儲器,因此可以用替代輸入窗函數代替 Hanning 窗。

另外八個乘法器用于在 FFT 輸出處執行可選的功率計算,其中四個輸出中每一個輸出的實部和虛部進行平方,然后相加。,平均器級將 50% 輸入重疊 FFT 的兩個輸出相加,以改善信噪比特性。

在 FPGA 的輸出端,多路復用器允許將每個信號處理階段的結果定向到處理器接口。下圖2 顯示了圖1所示子卡模塊的FPGA內部的所有基本功能塊。

結論

對于 4,096 點復雜 FFT,該 FPGA 引擎的執行速度為 10.24 微秒,其性能比在 400 MHz G4 PowerPC 上運行的優化 FFT 算法的基準高出十倍!

為了實現優于 90 dB 的計算動態范圍,采用了多種技術來減少 FPGA 整數運算中固有的舍入和截斷誤差。通過部署可用的 FPGA 資源優化執行速度后,整個設計利用了 XC2V3000 器件 96 個乘法器中的 76 個、99% 的邏輯片和 97% 的塊 RAM。

盡管這種特殊的 FPGA 組件由于近推出而仍然價格昂貴,但球柵陣列封裝圖案的兩個同心子集可容納同一系列中的兩個較小的器件,從而為要求不高的應用節省成本。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、8月12號西安中心開課、歡迎咨詢! 基于FPGA的多通道頻率檢測技術方案 利用FPGA實現的一種機載高清視頻處理模塊

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:將 FPGA 嵌入 DSP 驅動的軟件無線電應用中

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602006

原文標題:將 FPGA 嵌入 DSP 驅動的軟件無線電應用中

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

軟件無線電接收SLE串口透傳信號問題

陸地移動無線電調制分析儀的技術原理和應用場景

無線電接收設備中常用的高頻電路有哪些

高頻與射頻技術只能應用于無線電系統嗎

無線電時鐘的dcf信號是什么意思

將FPGA嵌入DSP驅動的軟件無線電應用中

工業和信息化部優化UWB和RFID設備無線電管理規定

網絡研討會預告 | 《如何使用Zynq Ultrascale+ RFSoC實現軟件定義無線電》

軟件無線電安全之GNU Radio基礎知識

RRH(遠程無線電頭)是什么?RRH的應用和功能

將 FPGA 嵌入 DSP 驅動的軟件無線電應用中

將 FPGA 嵌入 DSP 驅動的軟件無線電應用中

評論