半導體器件有許多封裝形式,按封裝的外形、尺寸、結構分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術指標一代比一代先進。

總體說來,半導體封裝經歷了三次重大革新:第一次是在20世紀80年代從引腳插入式封裝到表面貼片封裝,它極大地提高了印刷電路板上的組裝密度;第二次是在20世紀90年代球型矩陣封裝的出現,滿足了市場對高引腳的需求,改善了半導體器件的性能;芯片級封裝、系統封裝等是現在第三次革新的產物,其目的就是將封裝面積減到最小。

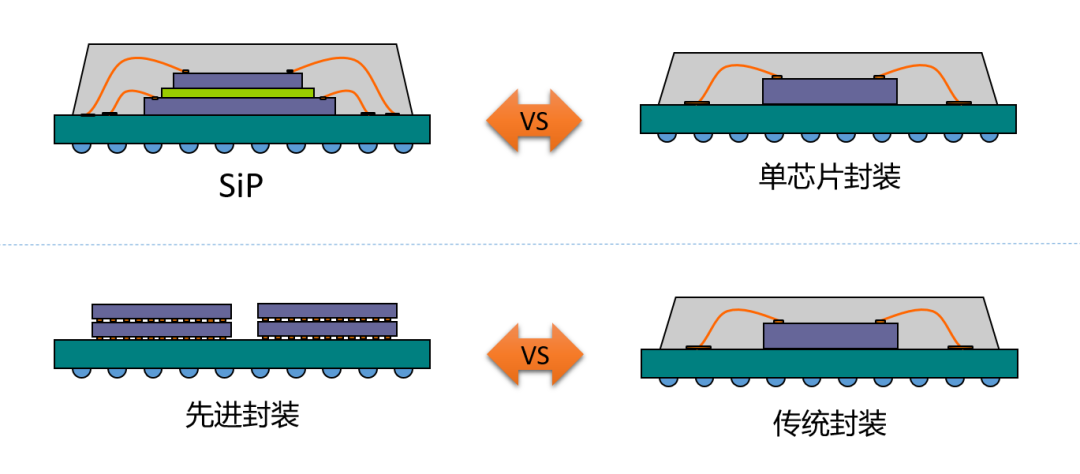

半導體產品在由二維向三維發展,從技術發展方向半導體產品出現了系統級封裝(SiP)等新的封裝方式,從技術實現方法出現了倒裝(FlipChip),凸塊(Bumping),晶圓級封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進封裝技術。

傳統封裝vs先進封裝

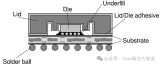

傳統封裝概念從最初的三極管直插時期后開始產生。傳統封裝過程如下:將晶圓切割為晶粒(Die)后,使晶粒貼合到相應的基板架的小島(LeadframePad)上,再利用導線將晶片的接合焊盤與基板的引腳相連(WireBond),實現電氣連接,最后用外殼加以保護(Mold,或Encapsulation)。典型封裝方式有DIP、SOP、TSOP、QFP等。

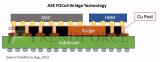

先進封裝主要是指倒裝(FlipChip),凸塊(Bumping),晶圓級封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等封裝技術。先進封裝在誕生之初只有WLP,2.5D封裝和3D封裝幾種選擇,近年來,先進封裝的發展呈爆炸式向各個方向發展,而每個開發相關技術的公司都將自己的技術獨立命名注冊商標,如臺積電的InFO、CoWoS,日月光的FoCoS,Amkor的SLIM、SWIFT等。盡管很多先進封裝技術只有微小的區別,大量的新名詞和商標被注冊,導致行業中出現大量的不同種類的先進封裝,而其誕生通常是由客制化產品的驅動。

先進封裝優勢

先進封裝提高加工效率,提高設計效率,減少設計成本。

先進封裝主要包括倒裝類(FlipChip,Bumping),晶圓級封裝(WLCSP,FOWLP,PLP),2.5D封裝(Interposer)和3D封裝(TSV)等。以晶圓級封裝為例,產品生產以圓片形式批量生產,可以利用現有的晶圓制備設備,封裝設計可以與芯片設計一次進行。這將縮短設計和生產周期,降低成本。

先進封裝提高封裝效率,降低產品成本。

隨著后摩爾定律時代的到來,傳統封裝已經不再能滿足需求。傳統封裝的封裝效率(裸芯面積/基板面積)較低,存在很大改良的空間。芯片制程受限的情況下,改進封裝便是另一條出路。舉例來說,QFP封裝效率最高為30%,那么70%的面積將被浪費。DIP、BGA浪費的面積會更多。

先進封裝以更高效率、更低成本、更好性能為驅動。

先進封裝技術于上世紀90年代出現,通過以點帶線的方式實現電氣互聯,實現更高密度的集成,大大減小了對面積的浪費。SiP技術及PoP技術奠定了先進封裝時代的開局,2D集成技術,如WaferLevelPackaging(WLP,晶圓級封裝),Flip-Chip(倒晶),以及3D封裝技術,ThroughSiliconVia(硅通孔,TSV)等技術的出現進一步縮小芯片間的連接距離,提高元器件的反應速度,未來將繼續推進著先進封裝發展的腳步。

先進封裝技術

Flip-Chip & Bumping

FlipChip指的是芯片倒裝,以往的封裝技術都是將芯片的有源區面朝上,背對基板和貼后鍵合。而FlipChip則將芯片有源區面對著基板,通過芯片上呈陣列排列的焊料凸點(Bumping)實現芯片與襯底的互聯。硅片直接以倒扣方式安裝到PCB從硅片向四周引出I/O,互聯長度大大縮短,減小了RC(Resistance-Capacitance)延遲,有效的提高了電性能。

FlipChip的優勢主要在于以下幾點:小尺寸,功能增強(增加I/O數量),性能增強(互聯短),提高了可靠性(倒裝芯片可減少2/3的互聯引腳數),提高了散熱能力(芯片背面可以有效進行冷卻)。

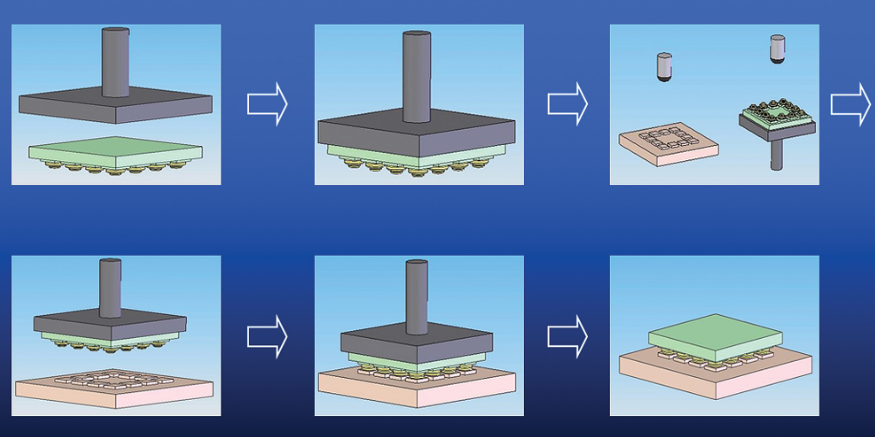

▼倒裝芯片晶體貼裝技術

?Bumping是一種新型的芯片與基板間電氣互聯的方式。

可以通過小的球形導電材料實現,這種導電球體被稱為Bump,制作導電球這一工序被稱為Bumping。當粘有Bump的晶粒被倒臵(Flip-Chip)并與基板對齊時,晶粒便很容易的實現了與基板Pad(觸墊)的連接。相比傳統的引線連接,Flip-Chip有著諸多的優勢,比如更小的封裝尺寸與更快的器件速度。

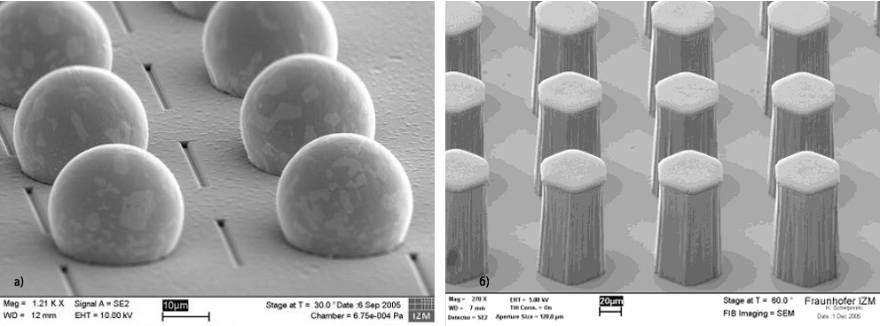

▼焊球端子和柱式端子

?FlipChip的關鍵一步是Bumping,可以通過在晶圓上制作外延材料來實現。

當芯片制作工序完成后,制造UBM(Underbumpmetallization)觸墊將被用于實現芯片和電路的連接,Bump也會被淀積與觸點之上。焊錫球(Solderball)是最常見的Bumping材料,但是根據不同的需求,金、銀、銅、鈷也是不錯的選擇。對于高密度的互聯及細間距的應用,銅柱是一種新型的材料。焊錫球在連接的時候會擴散變形,而銅柱會很好的保持其原始形態,這也是銅柱能用于更密集封裝的原因。

?FlipChip產品對應不同bumping類型增長速度不一。

根據Yole預測,采用倒裝芯片技術的集成電路出貨量將保持穩定增長,預計產能將以9.8%的復合年增長率擴張,從2014年的約合1600萬片12寸晶圓增長到2020年的2800萬片。終端應用主要為計算類芯片,如臺式機和筆記本電腦的CPU、GPU和芯片組應用等。

?其中鍍金晶圓凸點(Au-platedwaferbumping)將穩定增長,**由于IC顯示驅動器(4K2K超高清電視和高清晰度、大屏幕平板電腦和智能手機)的市場驅動。預計產能將以4%的復合年增長率擴大,從2014年的430萬片增長到2020年的540萬片。

?金釘頭凸點(Austudbumping)產能將略有下滑,**從2014年的30.4萬片降到2020年的29.3萬片,主要原因是射頻器件從倒裝芯片轉移至晶圓級芯片尺寸封裝(WLCSP)。但是,新興應用的需求將增加,如CMOS圖像傳感器模組、高亮度LED等。

?中道封裝技術需求增長,將帶來行業上下游的跨界競爭。**針對3DIC和2.5D中介層平臺的“中端工藝(middleend-process)”基礎設施的出現將使Fab和IDM受益,并在較小程度上分給OSAT。2.5D中介層平臺的發展將會產生價值的轉移,從襯底供應商轉向前端代工廠。

2.5D封裝:RDL&中介層

?RDL(Redistributionlayer,再分布層):在晶圓水平上,觸點再分布可以很高效的進行。再分布層用于使連線路徑重新規劃,落到我們希望的區域,也可以獲得更高的觸點密度。再分布的過程,實際上是在原本的晶圓上又加了一層或幾層。首先淀積的是一層電介質用于隔離,接著我們會使原本的觸點裸露,再淀積新的金屬層來實現重新布局布線。UBM在這里會被用到,作用是支撐焊錫球或者其他材料的接觸球。

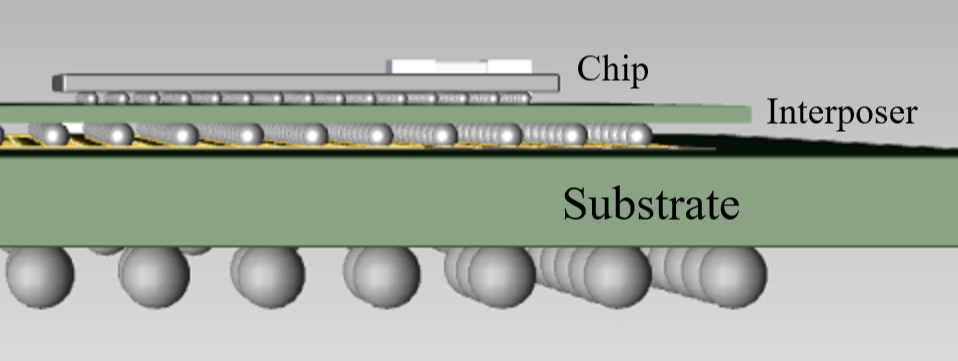

?中介層(Interposer):指的是焊錫球和晶粒之間導電層。它的作用是擴大連接面,使一個連接改線到我們想要的地方。與再分布層作用類似。

▼中間層(Interposer)示意

3D封裝:TSV,PoP和MEMS

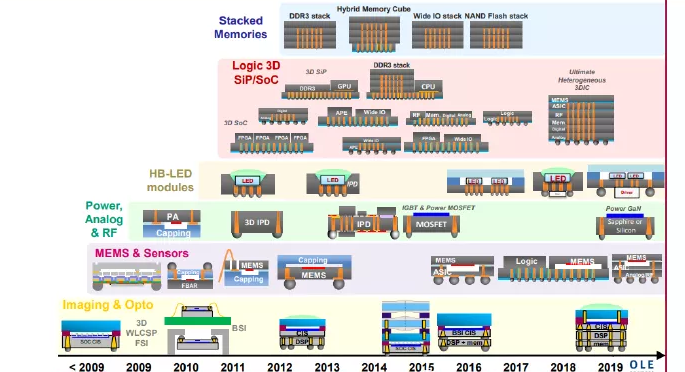

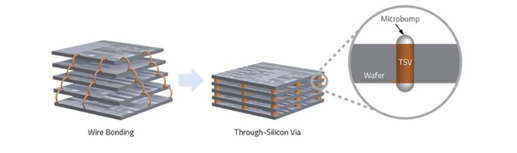

?TSV(Through-siliconvia,硅通孔):Bump和RDL會占用芯片接合到基板上的平面面積,TSV可以將芯片堆疊起來使三維空間被利用起來。更重要的是,堆疊技術改善了多芯片連接時的電學性質。引線鍵合可以被用于堆疊技術,但TSV吸引力更大。TSV實現了貫穿整個芯片厚度的電氣連接,更開辟了芯片上下表面之間的最短通路。芯片之間連接的長度變短也意味著更低的功耗和更大的帶寬。TSV技術最早在CMOS圖像傳感器中被應用,未來在FPGA、存儲器、傳感器等領域都將被應用。根據Yole預測,2016~2021年,應用TSV技術的晶圓數量將以10%的年復合增長率增長。3D存儲芯片封裝也會在將來大量的用到TSV。

▼3DIC和TSV技術演進路徑

▼TSV技術示意圖

?PoP(PackageonPackage,堆疊封裝):PoP是一種將分離的邏輯和存儲BGA(Ballgridarray,球狀引腳柵格陣列)包在垂直方向上結合起來的封裝技術。在這種結構中,兩層以上的封裝單元自下而上堆疊在一起,中間留有介質層來傳輸信號。PoP技術增大了器件的集成密度,底層的封裝單元直接與PCB板接觸。傳統的PoP是基于基板的堆疊,隨著存儲器對高帶寬的需求,球間間隔要求更小,未來將會與FOWLP技術相結合,做基于芯片的堆疊。

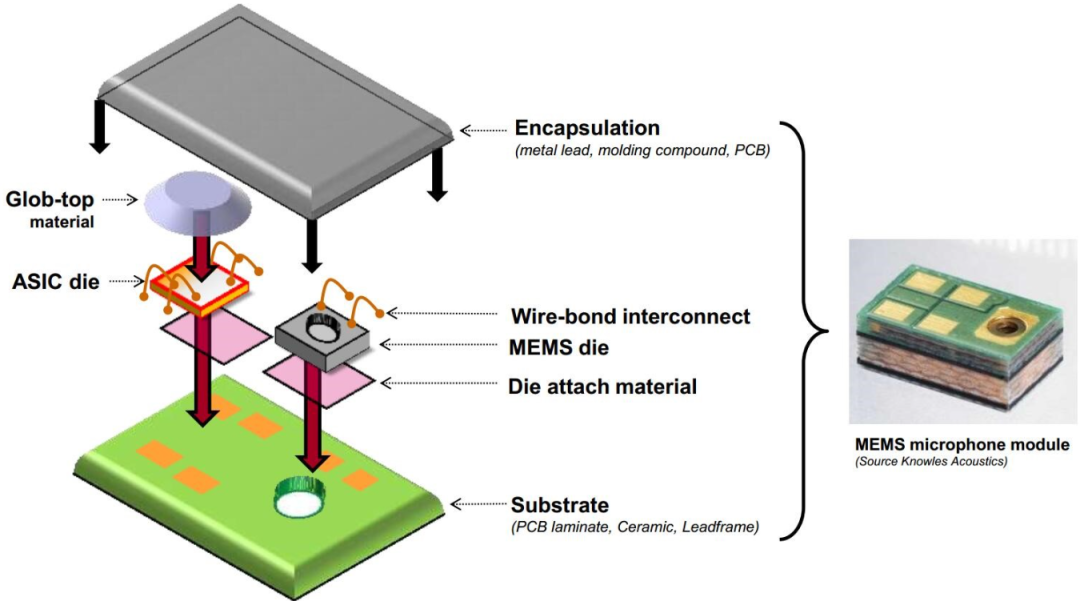

?MEMS封裝:微機電系統在近些年應用越來越廣泛,隨著傳感器、物聯網應用的大規模落地,MEMS封裝也備受關注。MEMS的封裝不同與集成電路封裝,分為芯片級、模組級、卡級、板級、門級等多元垂直分級封裝,設計時也需考慮不同模組間的相互影響。目前MEMS封裝市場規模在27億美元左右,20162020年間將會維持16.7%的年復合增長率高速增長。其中RFMEMS封裝市場是主要驅動,20162020年間,年復合增長率高達35.1%。

▼MEMS封裝技術示意圖

在整個MEMS生態系統中,MEMS封裝發展迅速,晶圓級和3D集成越來越重要。主要的趨勢是為低溫晶圓鍵合等單芯片集成開發出與CMOS兼容的MEMS制造工藝。另一個新趨勢是裸片疊層應用于低成本無鉛半導體封裝,這種技術可為量產帶來更低的成本和更小的引腳封裝。但是,MEMS器件的CMOS和3D集成給建模、測試和可靠性帶來挑戰。

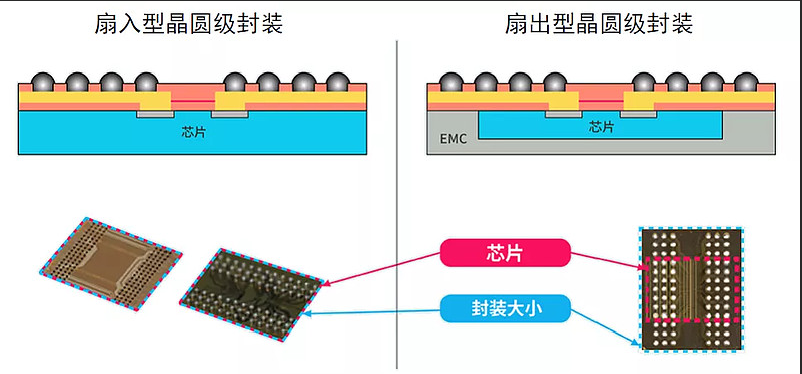

FIWLP&FOWLP,PLP

首先要提及Wafer-levelpackaging(WLP,晶圓級封裝)的概念。在傳統封裝概念中,晶圓是先被切割成小的晶粒,之后再進行連接和塑封。而晶圓級封裝工序恰好相反,晶圓級封裝將晶粒在被切割前封裝完成,保護層將會被附著在晶圓的正面或是背面,電路連接在切割前已經完成。

? FIWLP:Fan-inWafer-levelpackaging,又稱WLCSP(Wafer-levelChipScalePackage),扇入式晶圓級封裝,也就是傳統的晶圓級封裝,切割晶粒在最后進行,適用于低引腳數的集成電路。隨著集成電路信號輸出的引腳數目的增加,焊錫球的尺寸也就變得越來越嚴格,PCB對集成電路封裝后尺寸以及信號輸出接腳位臵的調整需求得不到滿足,因此衍生出了扇出型晶圓級封裝。扇入晶圓級封裝的特征是封裝尺寸與晶粒同大小。

?FOWLP:Fan-outWafer-levelpackaging,扇出式晶圓級封裝,開始就將晶粒切割,再重布在一塊新的人工模塑晶圓上。它的優勢在于減小了封裝的厚度,增大了扇出(更多的I/O接口),獲得了更優異的電學性質及更好的耐熱表現。

FIWLP與FOWLP用途不同,均為今后的主流封裝手段。FIWLP在模擬和混合信號芯片中用途最廣,其次是無線互聯,CMOS圖像傳感器也采用FIWLP技術封裝。FOWLP將主要用于移動設備的處理器芯片中。根據Yole的預測,2018年以前FOWLP的主要驅動為蘋果智能手機的處理器芯片,2018年以后的FOWLP的主要驅動除了其他安卓手機處理器的增長,主要是高密度FOWLP在其他處理芯片的應用,如AI、機器學習、物聯網等領域。

▼FIWLP與FOWLP技術示意圖

?PLP:全稱Panel-levelpackaging,平板級封裝,封裝方法與FOWLP類似,只不過將晶粒重組于更大的矩形面板上,而不是圓形的晶圓。更大的面積意味著節約更多的成本,更高的封裝效率。而且切割的晶粒為方形,晶圓封裝會導致邊角面積的浪費,矩形面板恰恰解決了浪費問題。但也對光刻及對準提出了更高的要求。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27003瀏覽量

216268 -

電路板

+關注

關注

140文章

4905瀏覽量

97410 -

封裝

+關注

關注

126文章

7778瀏覽量

142719 -

BGA

+關注

關注

4文章

535瀏覽量

46728 -

DIP

+關注

關注

0文章

239瀏覽量

30108 -

先進封裝

+關注

關注

1文章

373瀏覽量

223

原文標題:什么是先進封裝?和傳統封裝有什么區別?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

傳統封裝和先進封裝的區別在哪

傳統封裝和先進封裝的區別

芯片的封裝有什么區別?

ad693ad和ad693aq的封裝有什么區別?

COB封裝是什么意思?與傳統封裝有什么區別?

SiP與先進封裝有什么區別

x2安規電容有灰色和黃色封裝有什么區別

什么是先進封裝?先進封裝和傳統封裝區別 先進封裝工藝流程

傳統封測廠的先進封裝有哪些

什么是先進封裝?和傳統封裝有什么區別?

什么是先進封裝?和傳統封裝有什么區別?

評論