來源:FPGA之家

隨著時下智能時代的發展,機器學習已成為不少專業人士的“必備技能”。盡管如此,可它在實用性上仍然存在一些問題。因而設計師們采取了架構精簡、壓縮、以及硬件加速等三種途徑。都有啥特點呢?請往下看~

精簡架構設計,輸入/輸出的極致簡化設計師減少層數或網絡中各層之間連接數量的任何努力,都會直接降低推理的內存要求和計算量。因此,我們很難預測指定網絡設計在指定問題和訓練集上的作用,除非有經驗可供參考。確定您是否需要特定深度學習網絡設計中全部 16 層的唯一方法,是以網絡的數層為樣本對其進行訓練和測試。但由于此類探索工作的費用較高,設計師往往更傾向于使用他們熟悉的網絡架構;當然,探索也可能有助于節省大量成本。

讓我們以 ImageNet 當前面臨的眾所周知的靜態圖像分類挑戰為例。深度學習網絡一般從上一層的每個節點為自身的每個節點獲取加權輸入,而圖像分類研究人員有了重大發現,即使用卷積神經網絡 (CNN) 可以化繁為簡(圖1)。

在其初層中,CNN 使用較少的卷積引擎替代完全連接的節點。卷積引擎并不為每項輸入提供權重,僅具有小型卷積核心。它可使用輸入圖像對核心進行卷積處理,生成特征圖—一種 2D 數組,表示圖像和圖像各點處核心之間的相似度。然后,特征圖可收到非線性化信息。卷積層的輸出是一個三維數組:該層中每個節點的 2D 特征圖。然后,該數組將經過池化運算降低分辨率,從而縮減 2D 特征圖的大小。

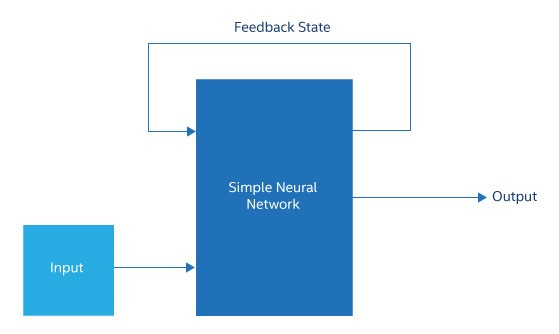

圖1.遞歸神經網絡通常只是將其部分中間狀態或輸出饋送回輸入的簡單神經網絡

現代 CNN 可能具有許多卷積層,每個卷積層跟著一個池化層。在靠近網絡輸出端的位置,卷積和池化層終止,其余層是完全連接的。因此,網絡從輸入端到輸出端逐漸變細,最終形成一個完全連接的層,其寬度剛好足以為每個所需的標記生成一個輸出。與具有相似深度的完全連接的深度學習網絡相比,該網絡能夠大幅減少權重、連接數和節點數。“壓縮”技術,突破推理的上限機器學習社區使用壓縮表示與卷積數據壓縮截然不同的概念。該語境下的壓縮包含一系列技術,用于減少生成推理所需的計算數量并降低其難度,修剪便是此類技術之一。在進行修剪時,深度學習網絡訓練通常會在權重矩陣中產生多個零或非常小的數值。實際上,這意味著無需計算將乘以權重的輸入。因此,表示推理計算的數據流圖表可被剪下一整個分支。經驗表明,如果一個網絡被修剪后再重新訓練,其精度實際上可以提高。

另一種壓縮方法是減少權重中的位數。雖然數據中心服務器可能將所有值保持在單精度浮點中,但研究人員發現,更低的權重精度和幾個位足以實現與 32 位浮點幾乎相同的精度。同樣,在應用非線性之后,節點的輸出可能只需要幾個位。如果推理模型將在服務器上執行,這幾乎沒有幫助。然而,該方法在一個 MCU 上非常有用,一個能夠非常有效地實施 2 位或 3 位乘法器的 FPGA 加速器可以充分利用這種壓縮形式。

總之,在某些情況下,修剪技術、大幅減少位數和相關技術已經被證明可以減少 20 到 50 倍的推理工作。這些技術可以把經過訓練的網絡的推理工作控制在一些邊緣計算平臺的范圍內。當壓縮不足以達成目的時,設計師可以轉向硬件加速,而且硬件加速有越來越多的替代方案。

硬件加速的新風標!推理所需的計算既不多樣也不復雜,主要包括許多乘積和 — 乘積累加 (MAC) — 運算,用于將輸入乘以權重和在每個節點將結果相加。該計算任務還包括所謂的修正線性單元 (ReLU) — 用于將所有負值設置為零 — 等非線性函數、雙曲正切或 sigmoid 函數 — 用于注入非線性 — 以及用于池化的最大值函數。總之,該計算任務看起來很像一個典型的線性代數工作負載。

應用超級計算領域的硬件思想。最簡單的方法是將輸入、權重和輸出作為向量進行組織,并使用內置到大型 CPU 中的向量 SIMD 單元。為了提高速度,設計師在 GPU 中使用了大量著色引擎。通過在 GPU 的內存層次結構中安排輸入、權重和輸出數據避免抖動或高缺失率,(絕非無足輕重的小問題,)但這并沒有阻止 GPU 成為數據中心深度學習領域使用最廣泛的非 CPU 硬件。最近幾代的 GPU 取得了長足進步,增加了更小的數據類型和矩陣數學塊來補充浮點著色單元,能夠更好地適應該應用。

這些調整說明了加速硬件設計師使用的基本策略:減少或消除指令獲取和解碼,減少數據移動,盡可能多地使用并行性,以及利用壓縮。難點在于確保這些操作在實施時不會互相干擾。

使用這些策略有幾種架構方法:

1、在芯片上對大量的乘法器、加法器和小型 SRAM 塊進行實例化,并通過片上網絡將它們鏈接起來。這為執行推理提供了原始資源,但存在一個關鍵挑戰,即從計算元件中高效獲取數據,以及將數據傳輸至計算元件及程序員。這些設計是過去許多大規模并行計算芯片的后繼者,所有這些芯片都遭遇了難以攻克的編程挑戰。

2、Google 張量處理單元(TPU)等芯片采用了進一步依托應用的方法,按照深層學習網絡的固有結構組織計算元件。這類架構將網絡的輸入權重乘法視為非常大的矩陣乘法,并創建硬件矩陣乘法器來執行它們。在 TPU 中,乘法是在一個收縮乘法器數組中完成的,在這個數組中,操作數自然地從一個單元流到另一個單元。數組被緩沖區包圍,以饋入激活和權重值,后面是激活函數和池化硬件。

通過對芯片進行特定的組織在一定程度上自動實施矩陣運算,TPU 可讓程序員免于通過計算元件和 SRAM 對數據移動進行精細安排。編程變得非常簡單,基本就包括將輸入和權重分組成矩陣并按下按鈕,但存在一個問題。如上所述,修剪會產生非常稀疏的矩陣,簡單地將這些矩陣饋入像 TPU 一樣的設備會導致大量毫無意義的乘法和加法。在模型開發的壓縮階段,可能需要將這些稀疏矩陣重新排列為更小的密集矩陣,以便充分利用硬件。

3、將推理任務作為一系列矩陣乘法建模,而非作為數據流圖表建模。加速器被設計成一個數據流引擎,數據從一側進入,通過可配置的鏈接流經一個類似于圖表的處理元件網絡,然后進行輸出。這種加速器可以配置為僅執行所修剪網絡需要的操作。

一旦選擇了架構,接下來的問題就是實施。在開發過程中,許多架構源于 FPGA,以滿足成本和調度要求。在一些情況下,一些架構將留在 FPGA 中——例如,當深度學習網絡模型預計會發生一個加速器設計無法完全處理的過多改變。但是,如果模型的改變很小,例如層排列有所不同和權重發生改變,ASIC 或 CPU 集成加速器可能是首選項。

這又回到了邊緣計算及其限制的話題。如果機器學習網絡要在一組服務器上執行,那么在服務器 CPU、GPU、FPGA 或大型 ASIC 加速器芯片上執行都是可行的選擇。但是,如果必須在一個更為有限的環境中執行,例如車間機器、無人機或攝像頭,則需要一個小型的 FPGA 或 ASIC。

對于極其有限環境中的小型深度學習模型,例如手機,內置于應用處理器 SOC 中的低功耗 ASIC 或加速器塊可能是唯一的選擇。盡管到目前為止,這些限制往往會促使設計師努力設計簡單的乘法器數組,但神經形態設計的卓越能效可能會使它們對下一代深度嵌入式加速器非常重要。

無論如何,機器學習都不再局限于數據中心范疇,推理正邁向邊緣。隨著研究人員不再聚焦當前的傳統深度學習網絡,將視線投向更多概念,邊緣的機器學習問題有望成為架構開發的前沿課題。

-

芯片

+關注

關注

453文章

50410瀏覽量

421849 -

硬件

+關注

關注

11文章

3252瀏覽量

66118 -

網絡

+關注

關注

14文章

7518瀏覽量

88632 -

機器學習

+關注

關注

66文章

8378瀏覽量

132412 -

cnn

+關注

關注

3文章

351瀏覽量

22170

發布評論請先 登錄

相關推薦

什么是機器學習?通過機器學習方法能解決哪些問題?

麻省理工學院推出新型機器人訓練模型

【「時間序列與機器學習」閱讀體驗】+ 鳥瞰這本書

【「時間序列與機器學習」閱讀體驗】+ 簡單建議

【《時間序列與機器學習》閱讀體驗】+ 了解時間序列

按照這樣學習C語言,成為卷王不是夢!

人工智能、機器學習和深度學習是什么

深度學習與傳統機器學習的對比

四足機器人ANYmal展新技能:跑酷

人工智能和機器學習的頂級開發板有哪些?

如何打通機器學習的“三大玄關”,你該這樣Get新技能!

如何打通機器學習的“三大玄關”,你該這樣Get新技能!

評論