嵌入式系統(tǒng)低速接口-SPI

繼續(xù)說SPI,SPI來說就是沒有IIC那么固定。它就是設計了一種二進制流的交互方式,所以這也是為什么它那么靈活的原因。它可以在任何兩個嵌入式的設備之間交換消息。

但是話又說回來了,SPI和UART都是串行的,那有啥區(qū)別呢?

SPI的優(yōu)點:

速度快,可達數(shù)十Mbps

接口簡單,只需要三根線(SCLK、MOSI、MISO)

多設備支持簡單,通過CS線選擇從機

更好的實時控制能力

支持全雙工通信

推挽驅動(跟漏極開路正相反)提供了比較好的信號完整性和較高的速度

比I2C或SMBus吞吐率更高

協(xié)議非常靈活支持“位”傳輸

不僅限于8-bit一個字節(jié)的傳輸

可任意選擇的信息大小、內容、以及用途

異常簡單的硬件接口:

一般來講比I2C或SMBus需要的功耗更低,因為需要更少的電路(包括上拉電阻)

沒有仲裁機制或相關的失效模式

“從設備”采用的是“主設備”的時鐘,不需要精確的晶振

“從設備”不需要一個單獨的地址 — 這點不像I2C或GPIB或SCSI

不需要收/發(fā)器

在一個IC上只用了4個管腳, 板上走線和布局連接都比并行接口簡單很多

每個設備最多只有一個單獨的總線信號(片選);其它的都是共享的

信號都是單方向的,非常容易進行電流隔離

對于時鐘的速度沒有上限,有進一步提高速度的潛力

SPI的缺點:

通信距離短,不適合長距離通信

通常需要額外的片選信號增加從機數(shù)量

全雙工通信復雜度較高

相比于I2C總線需要更多的管腳, 即便是只用到3根線的情況下

沒有尋址機制,在共享的總線連接時需要通過片選信號支持多個設備的訪問

在從設備側沒有硬件流控機制(主設備一側可以通過延遲到下一個時鐘沿以降低傳輸?shù)乃俾?

從設備無法進行硬件“應答”(主設備傳送的信息無法確定傳遞到哪里,是否傳遞成功)

一般只支持一個主設備(取決于設備的硬件構成)

沒有查錯機制

沒有一個正式的標準規(guī)范,無法驗證一致性

相對于RS-232, RS-485, 或CAN-總線,只能近距離傳輸

存在很多的變種,很難能夠找到開發(fā)工具(例如主適配卡)支持這所有的變種

SPI不支持熱交換(動態(tài)地增加一個節(jié)點).

如果想使用“中斷”,只有通過SPI信號以外的其它信號線,或者采用類似USB1.1或2.0中的周期性查詢的欺騙方式

有一些變種比如多路I/O SPI和下面定義的三線串行總線都是半雙工的

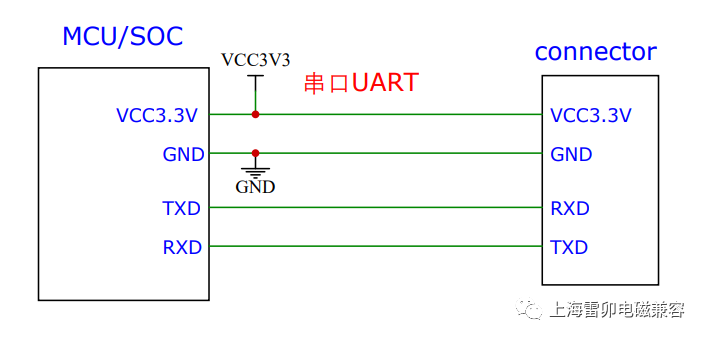

UART的優(yōu)點:

只需要兩根線(TX、RX),連接簡單

可支持較遠距離的通信

更簡單的全雙工通信機制

已經(jīng)得到廣泛應用,資料豐富

UART的缺點:

速率較慢,通常在Mbps量級

單主機與單從機通信,擴展難度大

對時序信號敏感,容易出現(xiàn)誤碼

不具備同步通信能力

總體來說,SPI更適合需要高速的數(shù)據(jù)交互和實時控制的場景;而UART更適合簡單的遠距離串行通信。

SPI偏向大數(shù)據(jù)流,UART可以長距離的控制。

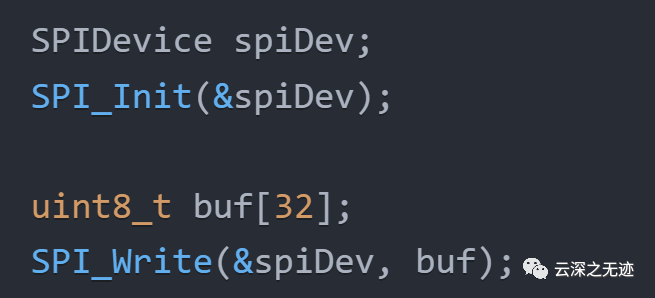

假如是自己的封裝的一個SPI的收發(fā)協(xié)議呢?

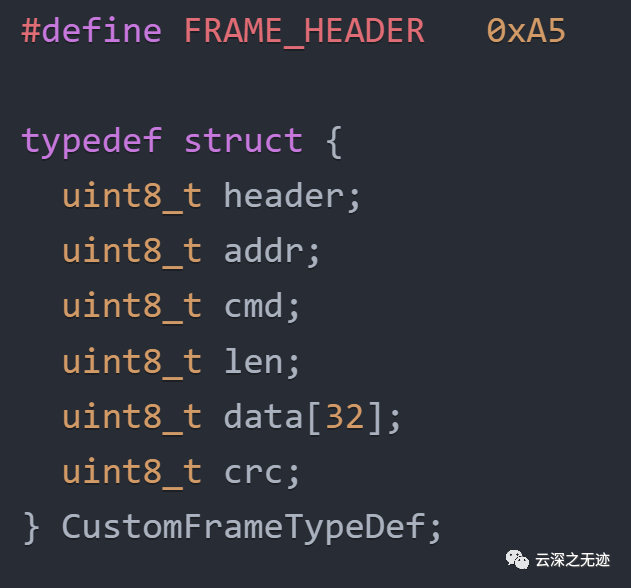

用結構體封裝一個這樣的東西,別問是啥?就這樣

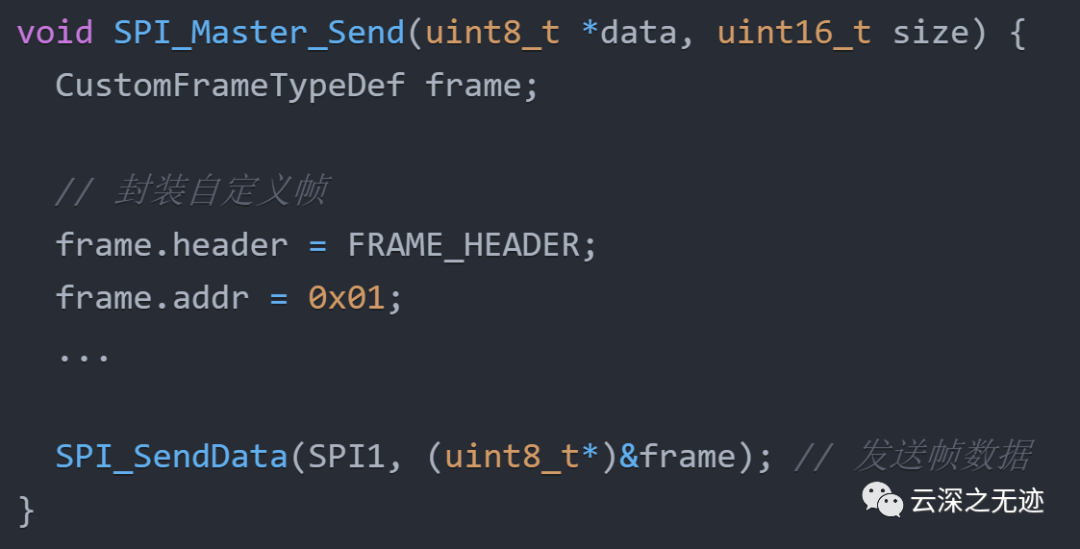

發(fā)送

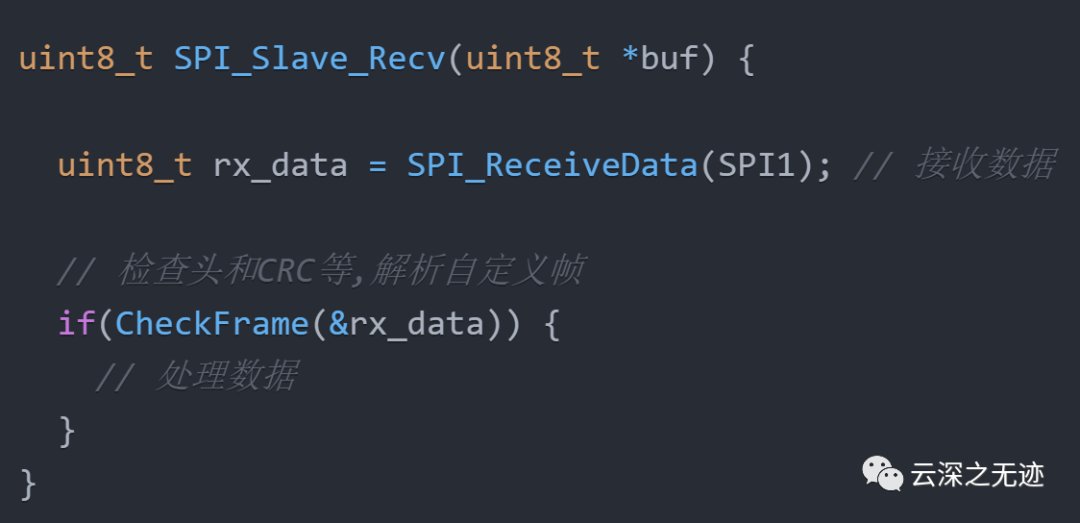

接收

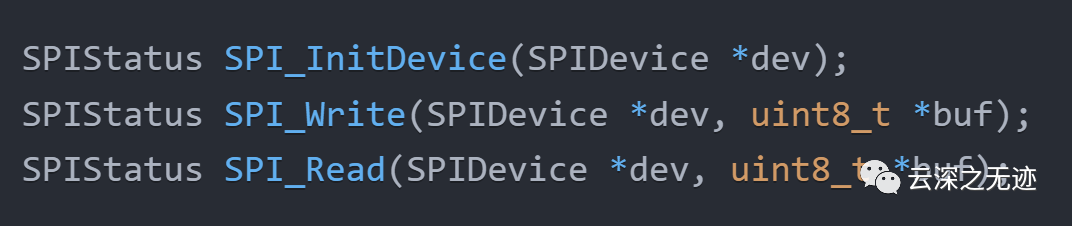

所以大概要實現(xiàn)的功能

在應用層的時候,這樣使用

以上這些函數(shù)就可以實現(xiàn),兩個MCU之間的自定義協(xié)議的通訊。

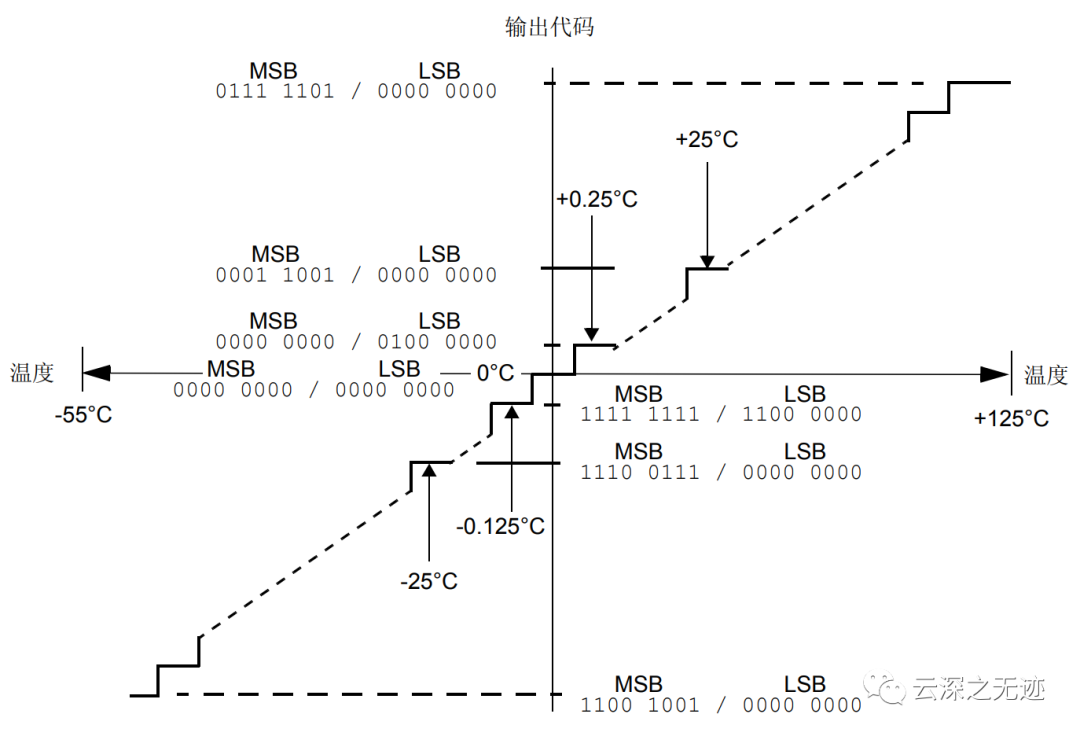

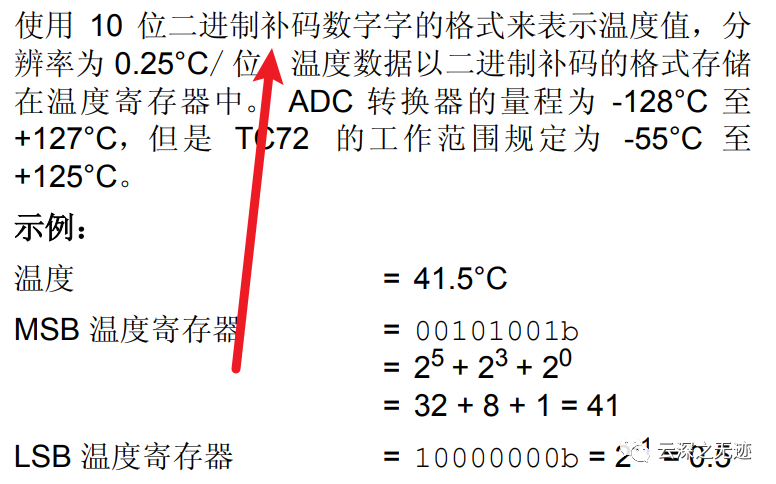

在數(shù)據(jù)在處理上面,還有一個小細節(jié),就是SPI和IIC的傳感器,有時候里面的data要使用二進制的補碼。

就像這樣

使用二進制補碼表示數(shù)據(jù)的好處主要有:

兼容有符號數(shù)據(jù)表示

二進制補碼可以直接表示傳感器采集的有符號數(shù)據(jù)(負數(shù)),無需額外處理。比如溫度值可以直接用二進制補碼形式表示正負溫度。

提高數(shù)據(jù)處理效率

如果使用純二進制表示無符號數(shù)據(jù),CPU進行有符號數(shù)的運算和比較需要額外處理。使用補碼可以直接進行算術運算,提高效率。

節(jié)省通信帶寬

如果使用ASCII等編碼,數(shù)據(jù)存儲和傳輸會膨脹很多。二進制補碼表示可以高效利用每一位。

簡化數(shù)據(jù)解析

補碼形式的數(shù)據(jù)可以直接作為int16、int32等有符號類型解析,無需復雜解碼。

減少出錯概率

ASCII編碼需要進行 num-to-ascii 和 ascii-to-num 的轉換,容易引入錯誤。二進制補碼可以避免這類問題。

統(tǒng)一不同設備的數(shù)據(jù)表示

采用標準補碼表示,使不同廠家的設備的數(shù)據(jù)可以統(tǒng)一被處理。

但需要注意,二進制補碼需要處理符號位擴展問題,左移時需要適當維護符號位。并且 debug 和顯示需做轉換。使用二進制補碼可以提高傳感器數(shù)據(jù)處理的效率與質量。

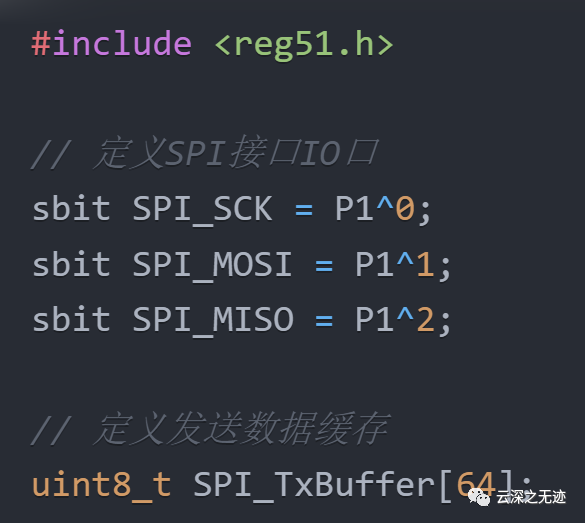

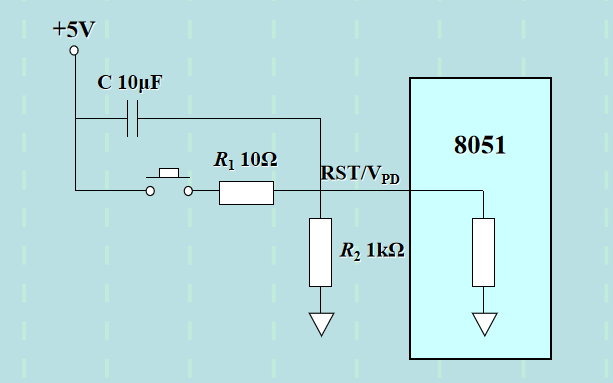

那說了這么多,自己模擬一個協(xié)議可能是最好的,這里就用51單片機來搞這個。

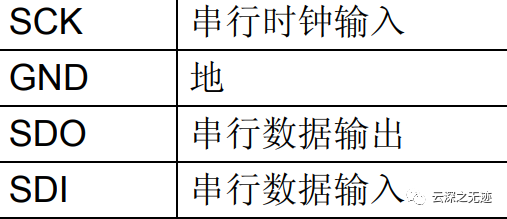

使用的引腳

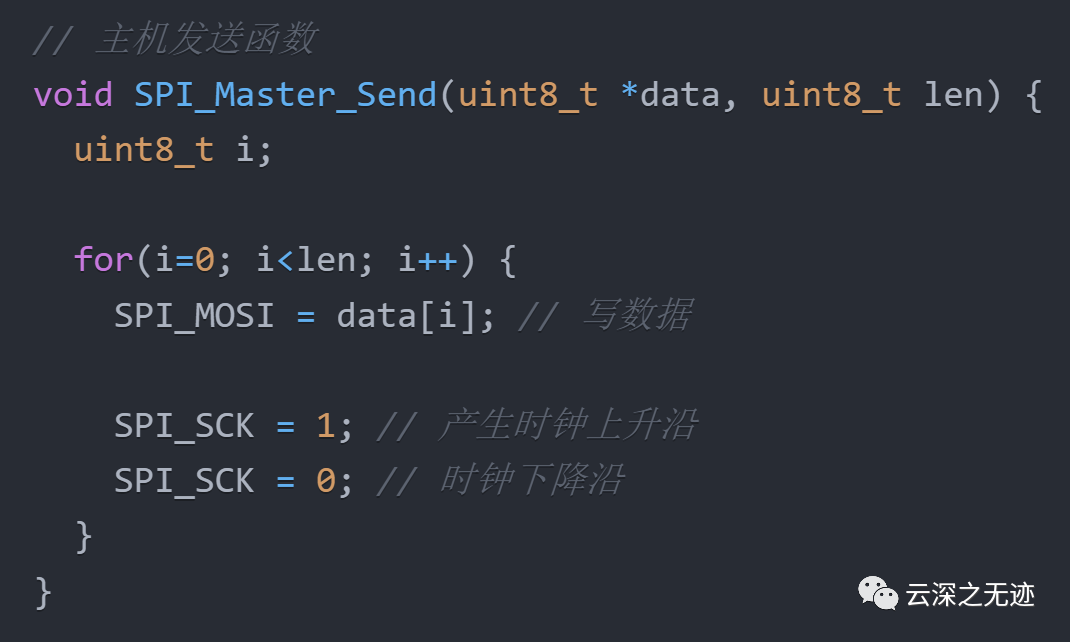

遍歷需要發(fā)送的數(shù)據(jù)字節(jié)數(shù)組,一位一位寫入MOSI口。同時通過設置SCK為1和0來模擬SPI時鐘的上升沿和下降沿。

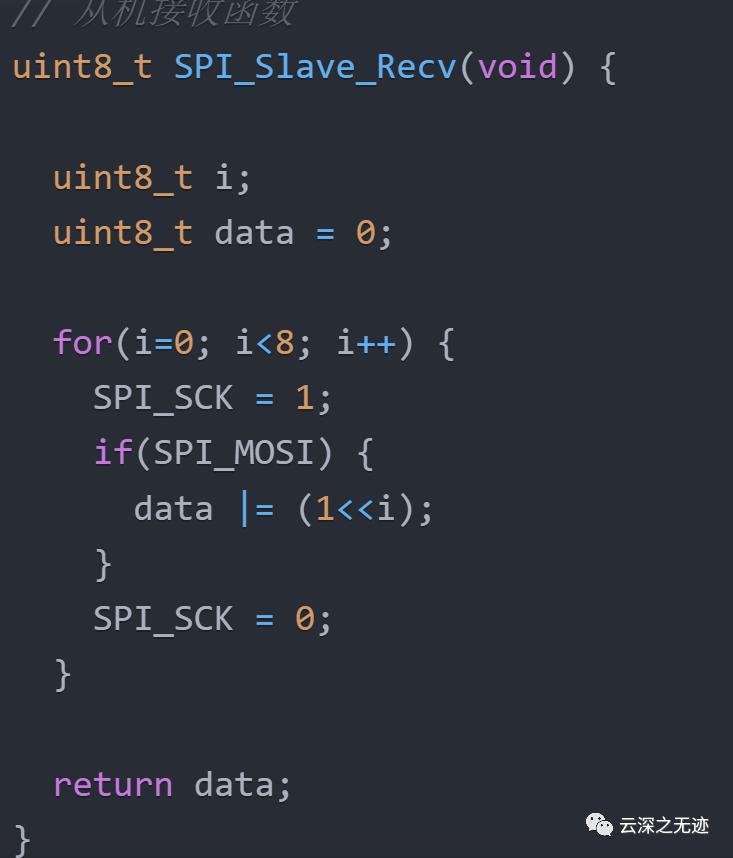

在一個8位循環(huán)內,讀取MOSI的每一位數(shù)據(jù),在SCK上升沿時采樣,并寫入data變量。SCK下降沿準備采樣下一位。

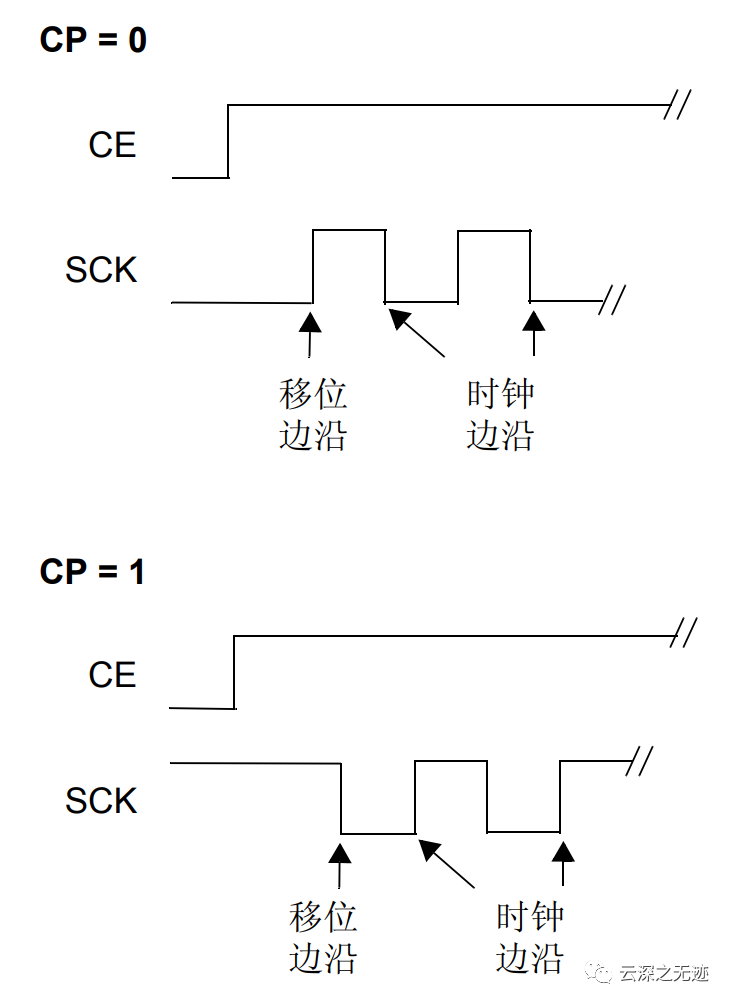

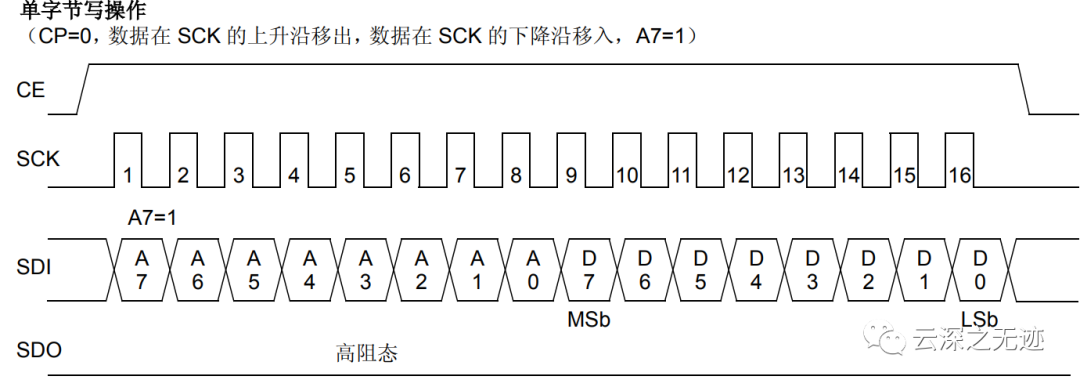

傳感器具有能在SCK輸入信號為有效高電平或低電平時工作的能力。當 CE 信號變成高電平時,檢測到 SCK 的 無效狀態(tài),而時鐘輸入 (CP)的極性決定數(shù)據(jù)是在系統(tǒng)時鐘的上升沿或下降沿移入或移出,

看眼引腳

這個圖給出了用于傳送數(shù)據(jù)到寄存器和從寄存器移出數(shù)據(jù)的相應時鐘邊沿。 每個時鐘脈沖傳送一位數(shù)據(jù) ,數(shù)據(jù)位以 8 位為一組傳送。

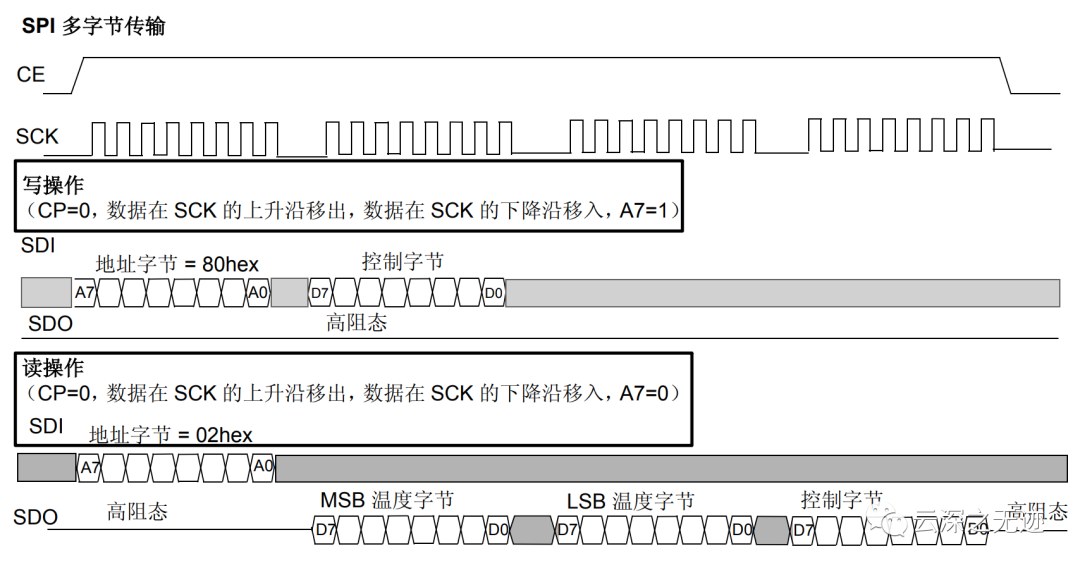

A是地址,D是數(shù)據(jù)。先發(fā)送地址字節(jié),隨后為數(shù)據(jù)。

數(shù)據(jù)可以采用單字節(jié)或多字節(jié)包的方式進行傳送,在 3 字節(jié)包中,數(shù)據(jù)序列包括溫度數(shù)據(jù)的 MSb、溫度數(shù)據(jù)的 LSb 和緊接著的控制寄存器數(shù)據(jù)。通過向寄存器寫入所需數(shù)據(jù)包的最高地址來啟動多字節(jié)讀功能。

串行輸出: SCLK : SCK, CLK.

主輸出 –> 從輸入: MOSI : SIMO, SDI(對于“從”設備), DI, DIN, SI, MTST.

主輸入 ←- 從輸出: –> MISO : SOMI, SDO (對于“從”設備), DO, DOUT, SO, MRSR.

從選擇: SS : nCS, CS, CSB, CSN, EN, nSS, STE, SYNC.

多數(shù)從設備的輸出是三態(tài)的,當該從設備沒有被選中的時候它們的MISO信號就為高阻(邏輯上斷開連接)。不具有三態(tài)輸出的器件是不能同其它器件共享SPI總線部分的,只能是一個從設備跟主設備相連。

單片機GPIO引腳的三態(tài)(Tri-state)是指該引腳可以處于三種狀態(tài):

1.推挽輸出: 引腳被配置為輸出,可以被置高電平(1)或者低電平(0)。

2.開漏輸出: 引腳被配置為開漏輸出,可以被置低電平(0),或處于高阻抗狀態(tài)(Z)。

3.高阻輸入: 引腳被配置為輸入,此時處于高阻抗狀態(tài)(Z),可以檢測外部信號的高低電平。

文章的最后解惑一下。

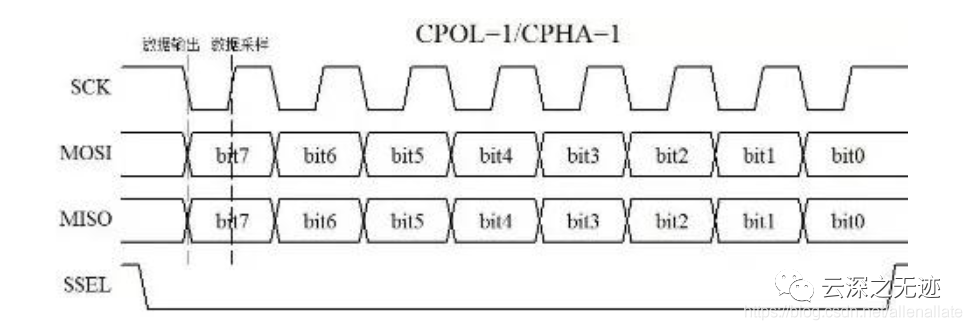

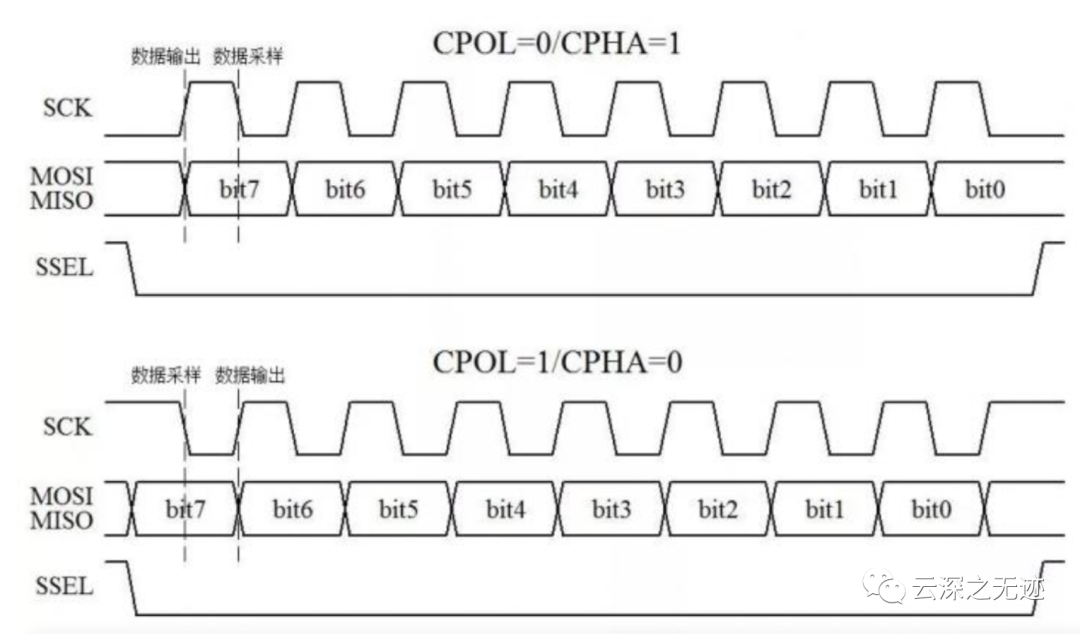

這里以最常見的SPI3模式說下時序圖怎么看。

當數(shù)據(jù)未發(fā)送時以及發(fā)送完畢后,SCK都是高電平,因此CPOL=1。看最前面。

在SCK第一個沿(下降沿)的時候,MOSI和MISO會發(fā)生變化。同時SCK第二個沿(上升沿)的時候,數(shù)據(jù)是穩(wěn)定的,此刻采樣數(shù)據(jù)是合適的,也就是上升沿即一個時鐘周期的后沿鎖存讀取數(shù)據(jù),即CPHA=1。

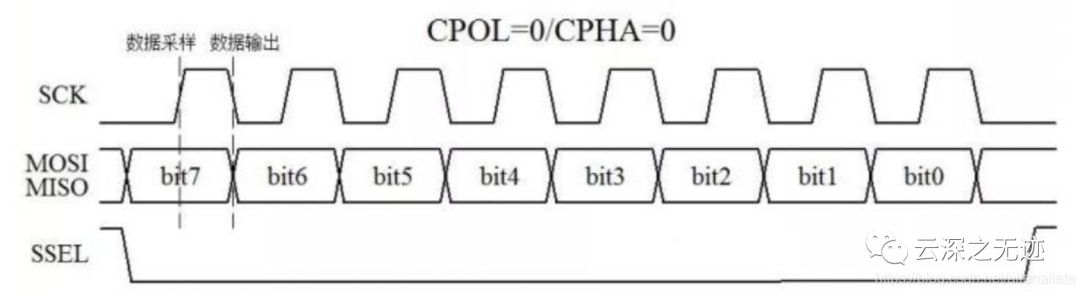

當CPHA=0、CPOL=0時SPI總線工作在方式0,如下圖。簡化起見把MOSI和MISO合在一起了。

SPI0通信時序圖

SPI1和SPI2

當CPHA=0、CPOL=1時SPI總線工作在SPI1

當CPHA=1、CPOL=0時SPI總線工作在SPI2。

SPI1和SPI2通信時序圖

要點,看發(fā)送前的時鐘,然后看兩個邊沿對應的數(shù)據(jù)線,判斷什么時候是保持邊沿的。適合采樣的。

審核編輯:湯梓紅

-

嵌入式系統(tǒng)

+關注

關注

41文章

3567瀏覽量

129230 -

接口

+關注

關注

33文章

8497瀏覽量

150835 -

SPI

+關注

關注

17文章

1701瀏覽量

91326 -

uart

+關注

關注

22文章

1227瀏覽量

101173

原文標題:?嵌入式系統(tǒng)低速接口-SPI(完結)

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

調試嵌入式系統(tǒng)設計中的低速串行總線(二)

DSP嵌入式系統(tǒng)人機接口設計

中低速數(shù)據(jù)采集系統(tǒng)設計,DSP嵌入式系統(tǒng)開發(fā)典型案例

嵌入式硬件通信接口協(xié)議中的串行通信接口-SPI

嵌入式系統(tǒng)教程之嵌入式系統(tǒng)的IO模塊詳細資料說明

嵌入式常見的通信接口/協(xié)議

嵌入式軟件接口怎么測試,嵌入式系統(tǒng)接口測試策略.doc

嵌入式Linux UART

嵌入式linux系統(tǒng)和嵌入式android系統(tǒng)的區(qū)別和聯(lián)系

嵌入式硬件通信接口協(xié)議-SPI(一)協(xié)議基礎

嵌入式系統(tǒng)串口UART接口為啥沒有數(shù)據(jù)輸出

嵌入式系統(tǒng)串口UART接口為啥沒有數(shù)據(jù)輸出

嵌入式系統(tǒng)低速接口SPI和UART的區(qū)別

嵌入式系統(tǒng)低速接口SPI和UART的區(qū)別

評論