大家好,這里是射頻學(xué)堂,今天給大家整理了一下一些知名外企射頻類(lèi)崗位面試題集,這些外企包括:Apple, Qualcomm, MediaTek, Intel, Samsung, Skyworks, Keysight, pSemi, Qorvo, Anokiwave 等等。

所以無(wú)論是初級(jí)崗位面試還是高級(jí)崗位,面試前最好能把這些問(wèn)題搞清楚,做到有備無(wú)患。

直接上題了:

How will you design a PA with 30 dBm output power? What load impedance for PA will you choose, at what point will you start thinking of power combining?

Breakdown mechanisms in MOS. How it happens? What is gate breakdown, what is drain source breakdown etc.? Go into physics of breakdown.

Have you designed any ESD protection circuit?

What is the impedance looking into gate of transistor with degeneration inductor?

Say you have matched LNA by doing source degeneration and a series inductor at input. What is the overall transconductance of the circuit?

How can you introduce real part in input impedance of CS amplifier?

How does device size affect noise in LNA design?

Can you derive the noise figure of common source amplifier?

How do you optimize transistor (in terms of bias, device size and layout) for ft, fmax and NF?

Do you know how to design bandgap, PTAT etc?

There are two current mirror transistor, one mirroring current from other. How do you increase the matching between the transistors?

How can you match Vth of transistors?

Vth increases with channel length or decreases? why?

Increasing bias current of cmos increases the voltage gain or decreases it?

How would you design two stage amplifier? Do you know how to compensate it?

Why Miller compensation does pole splitting? You also add some resistor in Miller compensation, why?

What is input impedance of CS amplifier with and without Cgd cap?

Derive output impedance expression of CS amplifier including Cgd.

How to increase gain of amplifier? How do you increase output impedance? Add current source load, stack devices, super transistor, how else? What about current? Is there a sweet spot for it?

What is the IIP3 of two cascaded blocks? Under what conditions this cascade IIP3 formula is not valid?

How is IM3 affected when you increase one tone amplitude and other remains fixed?

What is the relation between IIP3 and HD3?

What is the noise figure of two cascaded amplifiers?

Say you are given two amplifiers with some NF. You cannot change the amplifier design. Is there anything you can do to reduce the system noise?

What linearity metrics do you use for PAs? (P1,IIP3,ACLR,EVM,AM-AM, AM-PM)

How does AM-AM or AM-PM effect EVM?

Do you know what is memory effect?

Draw Pout vs Efficiency curve of class A, B and AB amplifier

If you are in class AB, how can you increase efficiency of the PA? assume passives are ideal.

How do you bias PA? How do you take care of thermal runaway?

What breakdown voltage in lower in CMOS and why? gate to drain or drain to source?

For which impedance do you match your PA? Your signal has PAPR, your output impedance is dynamically varying. Which impedance would you choose?

What is active load pull? Why do you use it?

Cascode LNA. How do you choose device size of input transistor? How do you choose Lg and Ls inductors? How do you choose cascode transistor size? How does cascode affect NF?

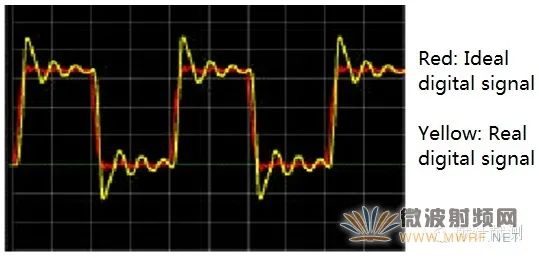

Draw time domain waveform of output of RC and RL low pass and high pass filters if the input is square wave.

What is current crowding in inductors? what are step symmetric inductors? pros and cons between signle ended and differential inductors?

If you have CS amplifier, and gate is terminated with very high impedance, assume there is Cgd capacitance. What is the output impedance?

How do you match 200 to 50 ohms? what is S21? Suppose the matching inductor has 1ohm series resistance. What will be the S21 now? (popular question)

What is the resonance frequency, Q and BW of parallel RLC tank?

Series resistor and inductor. If you adjust there values in such a way that Q remains same. How would it move on Smith chart for different values of R?

Say a typical oscillator circuit with LC load. What is the output impedance when it oscillates? What is the output impedance when it is in transient phase where oscillations are trying to build-up?

Say parallel LC tank. What is the current in tank during resonance vs source current?

What happens if I,Q are mismatched in RX? what about in TX?

How do you layout a transistor? what techniques do you use to reduce parasitis? How to choose number of fingers?

Pole zero analysis of typical OTA

Say single stage differential opamp. If load transistors have mismatch, dc offset is produced. How would you take care it? Like how would you size the transistors, big or small?

What is the significance of ft (transition frequency) and fmax (frequency at which unilateral gain becomes one) of transistor

This is a current mirror circuit. Say noise is added at this point. What will be its transfer function to output?

Input impedance of CG? What is impact of positive feedback from ro on input impedance?

How does AM-AM and AM-PM affects IM3s?

What is single side band modulation? Typical in TX where you only want to transmit one side band that is either flo+fbb or flo-fbb but not both together

Movement of constellation points (in EVM measurements) with AM-AM, AM-PM, noise, memory effect etc

If antenna impedance is varying, how do you take care of it in PA design?

An ideal amplifier with gain -1, input output connected with resistor R, what is the Zin?

How does the spectrum of square wave look like? What if you change the duty cycle to 25%?

哈哈,這么多題,看完之后發(fā)現(xiàn)大部分我也答不上來(lái)。繼續(xù)搬磚學(xué)習(xí)啦。

編輯:黃飛

-

ESD

+關(guān)注

關(guān)注

48文章

2012瀏覽量

172734 -

射頻

+關(guān)注

關(guān)注

104文章

5551瀏覽量

167556 -

RFIC

+關(guān)注

關(guān)注

1文章

60瀏覽量

24442

原文標(biāo)題:知名外企射頻面試題集 之 RFIC 篇

文章出處:【微信號(hào):射頻學(xué)堂,微信公眾號(hào):射頻學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字工程師需要掌握的射頻知識(shí)

電子工程師必備基礎(chǔ)知識(shí)手冊(cè)

電子工程師硬件工程師基礎(chǔ)知識(shí)

電子工程師基礎(chǔ)知識(shí)

數(shù)字工程師需要掌握哪些射頻知識(shí)呢?

電源工程師需要哪些知識(shí)

射頻工程師需要了解的知識(shí)

面向非射頻測(cè)試工程師的射頻測(cè)量基礎(chǔ)

軟件工程師面試前需要準(zhǔn)備什么

硬件工程師必備要了解哪些基礎(chǔ)知識(shí)

如何準(zhǔn)備算法工程師的面試需要知道哪些知識(shí)技能

華為射頻工程師面試經(jīng)驗(yàn)分享

電子工程師必備基礎(chǔ)知識(shí)

面試射頻工程師需要知道的基礎(chǔ)知識(shí)

面試射頻工程師需要知道的基礎(chǔ)知識(shí)

評(píng)論