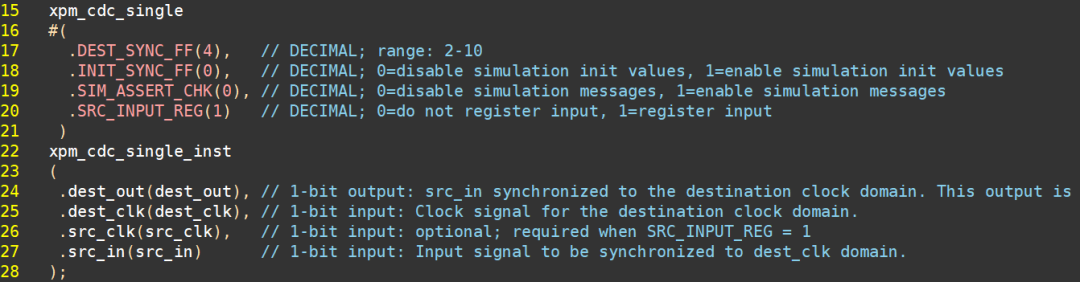

單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數DEST_SYNC_FF決定了級聯觸發器的個數,取值范圍為2~10;參數INIT_SYNC_FF決定了仿真時是否使用初始值;參數SIM_ASSERT_CHK用于檢查仿真中的問題;參數SRC_INPUT_REG用于是否對輸入信號(待跨時鐘域信號)在自身時鐘下寄存一拍。

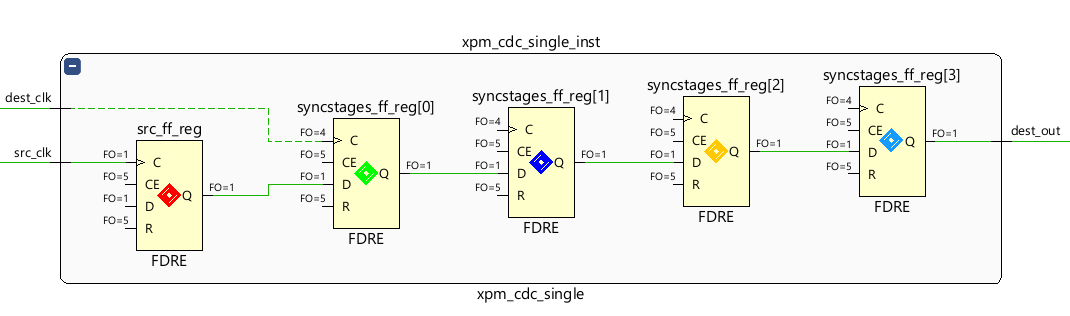

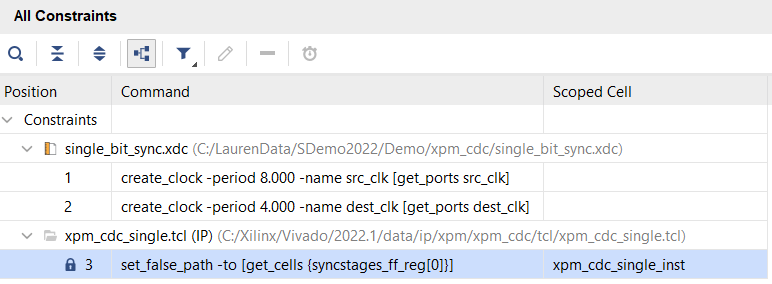

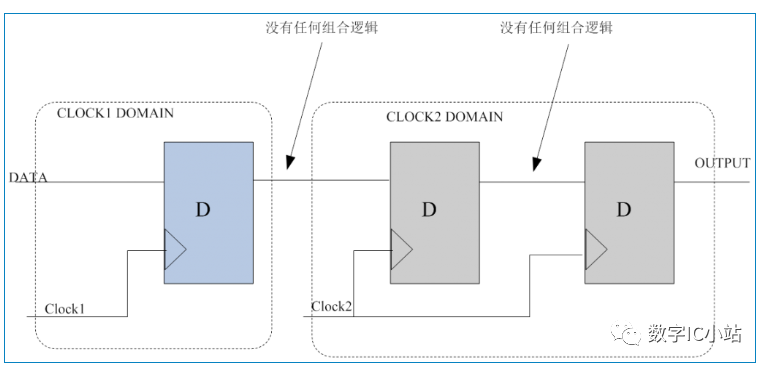

從綜合結果來看,當DEST_SYNC_FF設置為4,SRC_INPUT_REG設置為1時,形成如下圖所示電路。可用看到第一個觸發器位于src_clk時鐘域下,后續4個觸發器位于dest_clk時鐘域下。同時,xpm_cdc_single自帶約束將圖中紅色標記觸發器到綠色標記觸發器之間的路徑設置為偽路徑,使用set_false_path約束。

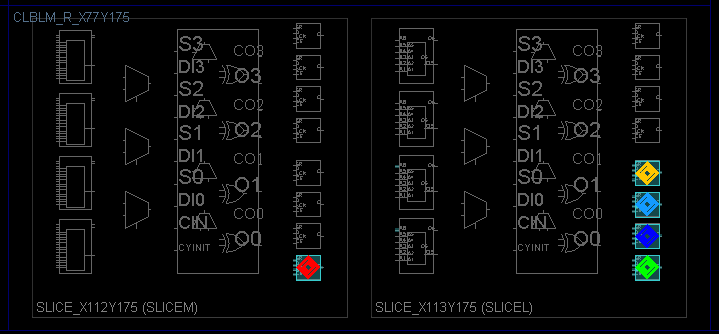

從最終的布線結果來看,工具會將后面4個觸發器放置的同一個SLICE內,這是因為這4個觸發器的屬性ASYNC_REG都被設置為TRUE。

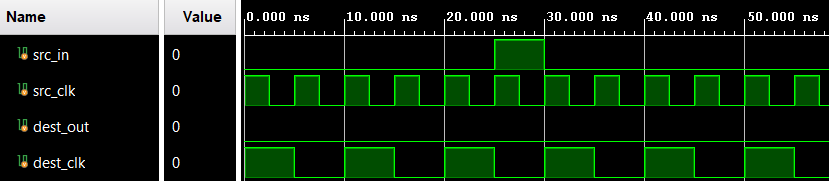

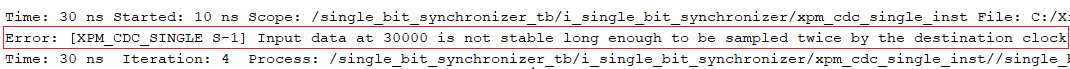

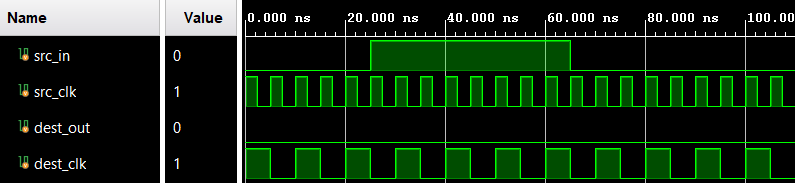

從仿真結果來看,如果出現如下情形,即輸入信號在高有效時無法被接收時鐘穩定地采樣到至少兩次,那么仿真就會給出Error信息。

滿足此條件時,就不會顯示此Error信息。這也告訴我們,工程實踐中,要確保待跨時鐘域信號在高有效時可以被接收時鐘至少穩定地采樣到兩次。

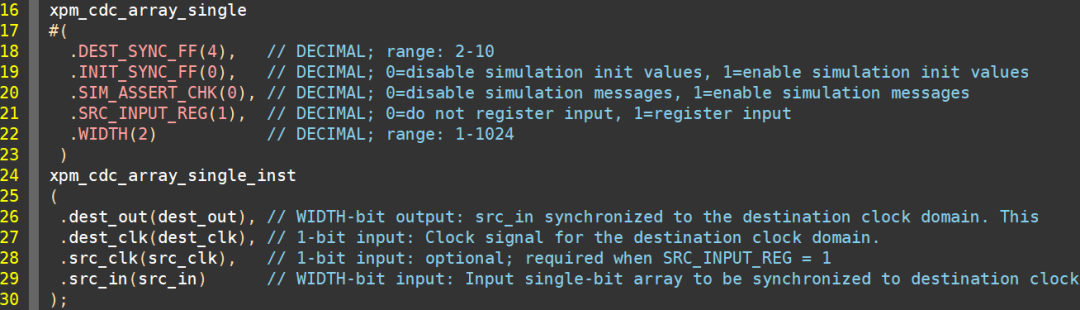

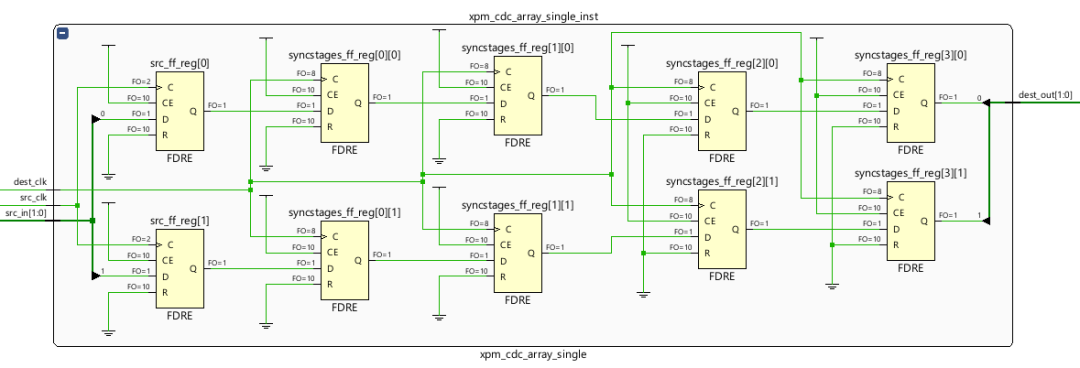

此外,XPM_CDC還提供了xpm_cdc_array_single,與xpm_cdc_single相比只多了一個參數WIDTH,用于指定位寬,但是需要注意的是盡管從形式上看傳輸的是一個多位寬數據,但實際上,每位是彼此相對獨立沒有關聯的。

例如,位寬為2,綜合結果如下,可以看到其實就是兩個xpm_cdc_single合并而成。

-

電路設計

+關注

關注

6667文章

2430瀏覽量

203420 -

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

時鐘域

+關注

關注

0文章

52瀏覽量

9529 -

輸入信號

+關注

關注

0文章

447瀏覽量

12542

原文標題:跨時鐘域電路設計:單位寬信號如何跨時鐘域

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

跨時鐘域電路設計:單位寬信號如何跨時鐘域

跨時鐘域電路設計:單位寬信號如何跨時鐘域

評論