首先簡單說明下Chris為什么會寫這一篇本來應該屬于東哥講的工藝知識的文章哈!這篇文章的誕生完全是出于一次偶然的交談,這天Chris在飲水機旁裝水,剛好看到隔離封裝部門的同事小馬哥也過來,他剛和某友商板廠開完會,估計是討論了板廠做金手指這類型板子的時候關于鍍金后的引線殘留工藝能力,于是隨口和Chris提了一嘴,說“不知道5mil到15mil的引線殘留到底對信號的SI性能有沒有影響啊!”的確,我們見到過很多加工出來后帶引線殘留的金手指板,但是之前的確沒去量化過它的影響!

于是Chris毫不猶豫的答應小馬哥,會抽空進行引線殘留的研究,看看引線對信號有什么影響。當然,Chris心里面還是有數(shù)的,大概知道對多高速率的信號才有造成影響。1G,2G的信號當然問題不大了,比較引線的長度也就是10mil上下的量級。于是Chris把研究的對象放在了更高速的PCIE信號上面,原因有兩種,一是PCIE的信號速率到達16Gbps到32Gbps(4.0和5.0協(xié)議),另外就是我們說的金手指基本上都是用于PCIE信號的傳輸,當然另外占很大比例的就是DDR的內存條了。于是毫不意外,我們研究的對象就鎖定在了PCIE的信號。

什么,不太了解金手指的鍍金工藝甚至為什么要鍍金?這樣的話可能需要大家先去看看東哥的文章或者直接騷擾他。Chris在這個場合就不展開了介紹工藝方面的問題了,免得說著說著文章字數(shù)多了,關鍵時候又要再戛然而止,只能等下周才有結論了哦!根據Chris和封裝小馬哥的進一步溝通,知道了某家板廠對金手指的工藝能力是這樣的:

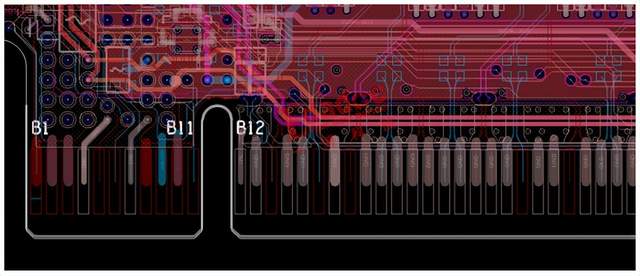

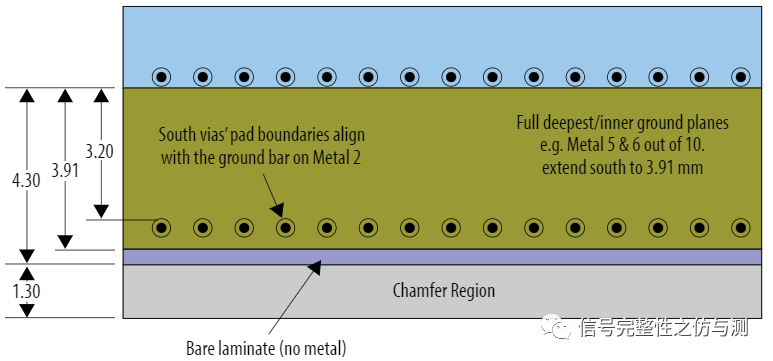

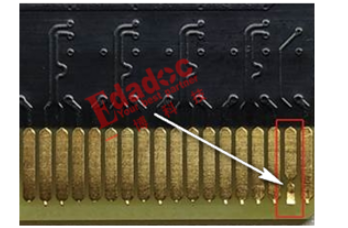

首先小馬哥介紹了這家板廠的兩種對金手指處理的工藝能力,一種引線殘留在5mil左右,另一種是通過常規(guī)機械成型的方法,引線殘留最大能到15mil。其中5mil內的引線工藝是通過干膜蝕刻的方法達到的,如下圖所示。

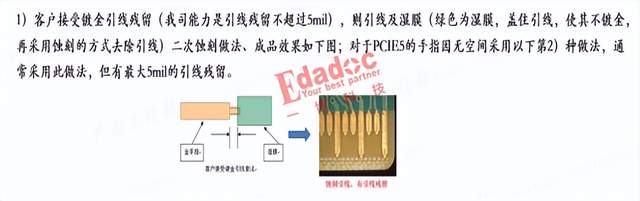

15mil的機械成型的方法就真的全靠物理加成了,是通過倒邊的方法來實現(xiàn)!

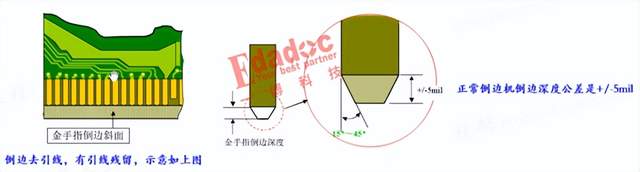

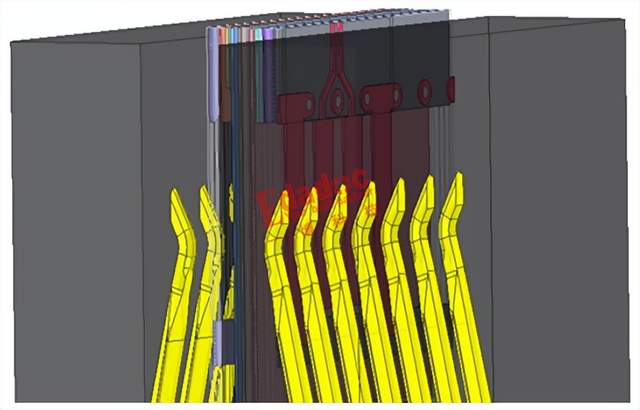

還是那句哈,大家如果對工藝實現(xiàn)本身感興趣的話,就去找東哥問個明白。下面的都是Chris的高速仿真驗證的時間了哈!當然上面都說到了這家板廠是去做傳輸PCIE5.0的金手指,那Chris就直接以5.0來進行研究了。說時遲那時快,Chris翻出了之前做過的一個PCIE5.0的金手指項目建好的模型,那么我們就去研究在理想沒有引線殘留、5mil引線殘留,還有就是最惡劣的15mil引線殘留下三種case對PCIE5.0信號的影響,建模如下所示:

對,我們模擬出三種引線狀態(tài)不同的case,那么我們下面就是要驗證這三個金手指模型都插到PCIE的slot槽上的時候,去看他們各自性能的表現(xiàn)。對,就是下面這樣的模型!

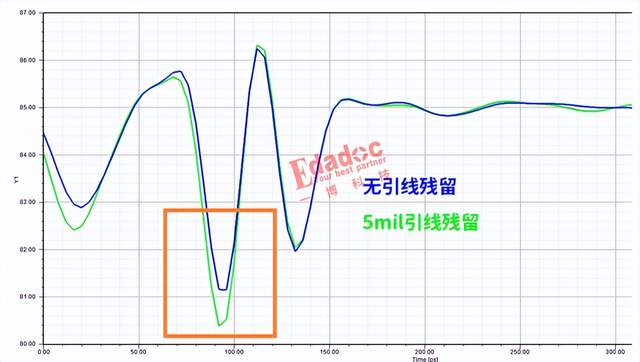

那么我們首先來看看沒有引線殘留的理想狀態(tài)下和有5mil的引線殘留兩個模型插到slot后的TDR阻抗的對比情況,如下所示:

感覺還好啊,阻抗也就是降低1個歐姆左右,基本上沒啥影響啊!看起來如果能做到5mil以內的引線殘留的話,對信號質量的影響其實是可控的哈!

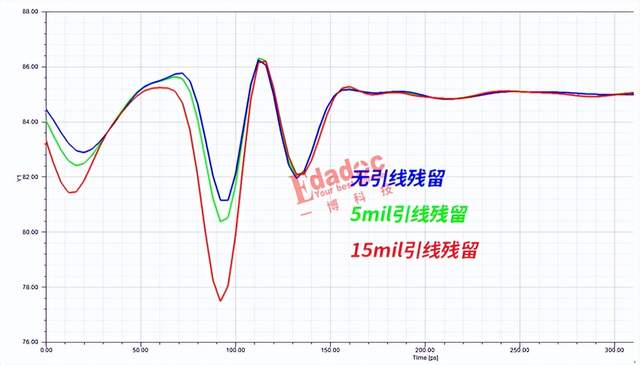

那如果引線殘留有15mil呢,那我們再接著往下看哈,同樣,我們仿真15mil的case3模型,然后把TDR阻抗的結果放到一起來進行對比,這樣影響不就來了嘛!

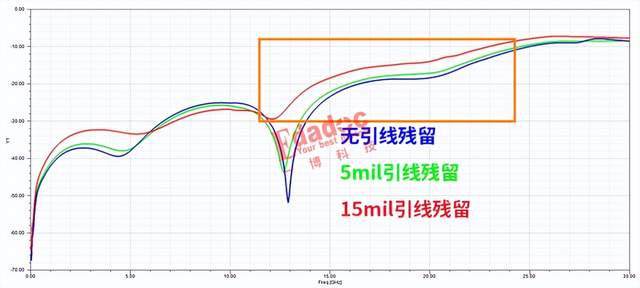

果然,15mil的引線殘留影響就大很多了,阻抗比無引線殘留的情況下要降低4-5歐姆,這是一個不少的量級了。這時候我們去看另外一個頻域指標回波損耗的話,也能明顯看到15mil引線殘留的惡化。

簡單總結下咯,看來金手指的鍍金引線殘留工藝也很有“先見之明”,工藝難度高的5mil內的引線殘留的確對信號質量影響不大,但是去到工藝難度稍低的15mil內引線殘留影響就真的不小了。對于我們SI來說,就是在設計中需要把這部分的影響考慮進去,在這個基礎上來評估信號裕量是否足夠了哈!

審核編輯 黃宇

-

金手指

+關注

關注

0文章

37瀏覽量

11655 -

高速信號

+關注

關注

1文章

222瀏覽量

17677 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發(fā)布評論請先 登錄

相關推薦

PCIe Gen5 Card金手指仿真與設計(上)

設計干貨分享:PCB“金手指”從設計到生產全流程

看似多余實則無用的金手指鍍金引線對高速信號有影響嗎?

金手指氧化的原因及預防方法

沉金和金手指在PCB電路板中的作用是什么

關于超微雙網卡工控主板金手指的詳細介紹

普通金手指的設計要求

pcb金手指怎么畫 pcb金手指設計技巧

看似多余實則無用的金手指鍍金引線對高速信號有影響嗎?

看似多余實則無用的金手指鍍金引線對高速信號有影響嗎?

評論