銦化合物(Indium compounds )在3D存儲器計算和射頻集成方面顯示出巨大的潛力,但還需要更多的研究。

研究人員繼續在3D設備集成方面取得進展,特別是與銦錫氧化物(ITO)有關,這種物質在顯示制造中得到了廣泛的應用。近期的研究表明,摻雜錫、鎵或鋅組合的不同的銦氧化物化合物可能會提高晶體管的特性,如高載流子遷移率和穩定的閾值電壓。但氧化物空位控制仍然是可靠的設備集成、BEOL金屬化和CMP工藝的關鍵。

3D在FEOL、BEOL和封裝中

單片3D集成描述了在單塊硅片上“就地”建造兩層或更多設備層的過程。這種3D的使用與3D封裝概念形成對比,3D封裝概念是在一個封裝中組合幾個完成的芯片,使用設備層分別制造然后再組合的層轉移技術。不同的方法都歸于“單片”之下,具體取決于特定設備的需求。單片集成也不排除在轉移層下使用不同的基板。

例如,CFETs首先在FEOL中堆疊基于硅或SiGe的PMOS和NMOS設備層,然后進行任何互連金屬化。層轉移通常用于組合CFETs中的不同層。CFETs減少了一對互補晶體管的占地面積,增加了整體晶體管密度。

但是,3D集成還可以用來縮小電路相關部分之間的距離,減少互連路徑的電阻,并提高整體速度。例如,常被提議作為解決內存帶寬瓶頸問題的方案的存儲器計算模塊,可能被直接放置在主CPU邏輯之上。射頻設備本身并不需要積極的縮放,但可以從3D集成提供的較短的電路路徑中受益。

在這些存儲器計算和射頻集成應用中,這些設備是BEOL流程的一部分,因此面臨嚴格的熱限制。為了防止銅擴散,處理溫度不能超過400°C。研究人員提議使用碳納米管和2D半導體,但這些技術仍然相對不成熟。

然而,銦氧化物半導體相對成熟,今天在顯示應用中得到了廣泛的使用。這些銦氧化物半導體可能包括錫(Sn)、鎵和/或鋅摻雜物。這些層通常通過濺射(物理氣相沉積)沉積,因為這個過程容易達到所需的低處理溫度。

將ITO從顯示器移至芯片

銦錫氧化物(ITO)可能是最成熟的基于銦的半導體,擁有幾十年的顯示行業制造歷史。在最近的VLSI技術研討會上,Yuye Kang及其在新加坡國立大學的同事調查了設備性能指標與通道厚度之間的關系。他們將ITO濺射到準備好的帶有鎢背門和氟化鉿柵極介質的基板上。使用3.5 nm的ITO通道和提高的ITO源和漏電極,他們似乎穩定了有效載流子遷移率為72cm2/V-sec。

盡管按照硅標準,該載流子遷移率較低,但 72cm2/V-sec 明顯優于之前報告的ITO器件的值。進一步將溝道厚度減小至2nm改善了亞閾值擺幅和閾值電壓,但器件遷移率惡化。

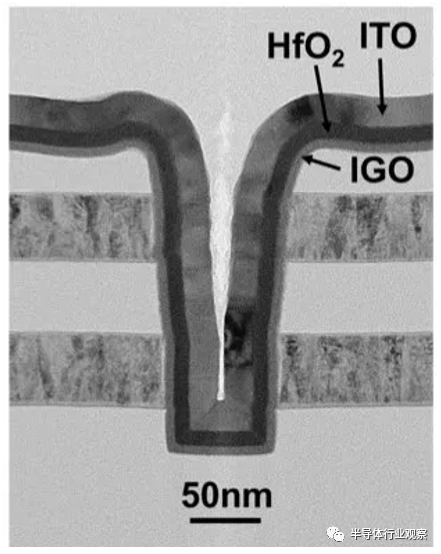

圖 1:測試結構展示了 IGO、ITO 和 HfO2的共形 ALD ,可以鈍化氧空位,同時實現比濺射更深的結構。來源:2023年VLSI研討會

眾所周知,界面散射會降低非常薄的半導體通道(包括硅通道)的遷移率。在銦基氧化物中,氧空位還會導致遷移率下降和閾值電壓不穩定。東京大學的 Kaito Hikake 及其同事在研究氧化銦鎵 (IGO) 時提出,環境中的氧氣也可以擴散到通道中,從而形成深層陷阱。控制氧含量和鈍化與氧相關的缺陷是這些材料面臨的根本挑戰,研究人員正在采取幾種不同的方法。新加坡國立大學的一個獨立小組在 Sonu (Devi) Hooda 提出的工作中使用了 ITO/IGZO(氧化銦鎵鋅)異質結構。在他們的工作中,ITO 厚度控制溝道載流子濃度,補償氧缺陷。同時,異質結構避免了僅在 ITO 中出現的 SS 退化和閾值電壓偏移。有效移動性,110 厘米處2/V-sec,優于其他結果,而且重要的是,與通道厚度無關。

含有或不含鎵的氧化銦

Kaito Hikake 的小組重點研究了 In-Ga-Zn 三元相圖中的 In-Ga 部分。純氧化銦實現更高的遷移率;純氧化鎵允許更大的帶隙。介于兩者之間,氧化銦鎵 (IGO) 最大限度地提高了熱穩定性。因此,雖然 IGO 在理論上非常有趣,但之前很少有關于實際設備的報道。

東京大學研究人員確定,In3Ga2Ox在遷移率、閾值電壓和穩定性之間提供了最佳權衡。雖然可以通過濺射進行沉積,但研究人員對垂直柱 FET 結構特別感興趣,并因其保形性以及出色的厚度和成分控制而選擇了 ALD。通過交替GaOx和InOx子周期,他們定義了膜的組成。接下來,他們重復這種ALD異質結構沉積盡可能多的次數,以產生所需的總體厚度。

研究人員制造了帶有 ITO 柵極電極和氧化鉿柵極電介質的單柵極和雙柵極器件。雙柵極器件比單柵極器件實現了更好的驅動電流和遷移率,這顯然是由于頂部電介質層對溝道的鈍化所致。具體地,使用臭氧(O3)源生長的ALD HfO2穩定了漏極電流和遷移率,而不改變閾值電壓。其他鈍化工藝,包括濺射 SiO2和使用 H2O氧源的 HfO2 ALD,導致強烈的負閾值電壓漂移。

最后,Zhuo Cheng Chang及其普渡大學的同事觀察到,鎵確實有助于穩定這些器件,但相對于純 In2O3 ,仍然會降低電氣性能。他們將氧化銦中閾值電壓的不穩定性歸咎于氧空位的產生在柵極偏壓應力下,空位充當淺施主。他們認為,O2退火可以鈍化這些潛在的施主位點,而不會引入Zn或Ga摻雜的負面影響。

實用性和BEOL設備

這里討論的器件都無法與領先的CMOS競爭。然而,它們與非晶硅(αSi)和其他可以使用低溫工藝的半導體處于同一區域。然而,無論具體材料如何,很明顯,基于銦的氧化物半導體在制造和使用過程中對氧濃度都極其敏感。實際器件的正確封裝對于在濕法清洗、CMP 以及晶體管制造和 BEOL 步驟之后的其他工藝步驟中保護它們至關重要。這些材料的靈活成分是否會成為一種優勢,為工藝工程師提供多種方法來根據其特定需求優化設備,還是成為一致、可靠行為的根本障礙,還有待觀察。

審核編輯:湯梓紅

-

3D

+關注

關注

9文章

2863瀏覽量

107328 -

存儲器

+關注

關注

38文章

7452瀏覽量

163606 -

封裝

+關注

關注

126文章

7784瀏覽量

142724 -

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

CMP

+關注

關注

6文章

141瀏覽量

25942

原文標題:3D存內計算,新突破

文章出處:【微信號:晶揚電子,微信公眾號:晶揚電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

液晶顯示器中常用芯片類型

液晶顯示器是什么原理制造的

液晶顯示器制造工藝流程基礎技術

低阻ITO玻璃的制造工藝

石墨烯電極將催生超薄軟性OLED顯示器

基于光電顯示用透明導電膜及玻璃(ITO)的原理

曲面顯示器是怎么設計的

顯示器處理器芯片是什么?顯示器處理器芯片市場的發展趨勢

新研究:將ITO從顯示器移至芯片

新研究:將ITO從顯示器移至芯片

評論