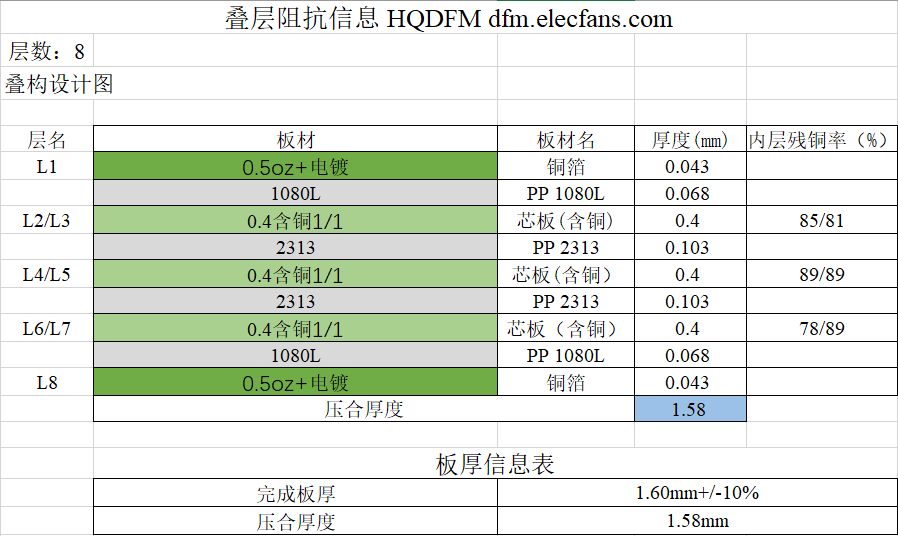

8層通孔板1.6mm厚度疊層與阻抗設計

在8層通孔板疊層設計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。

建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用1oZ,厚度為1.6mm。

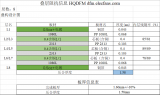

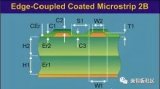

板厚推薦疊層如下圖(上)所示(8層通孔1.6mm厚度推薦疊層),阻抗線寬線距如下圖(下)所示(8層通孔1.6mm厚度各阻抗線寬線距)。

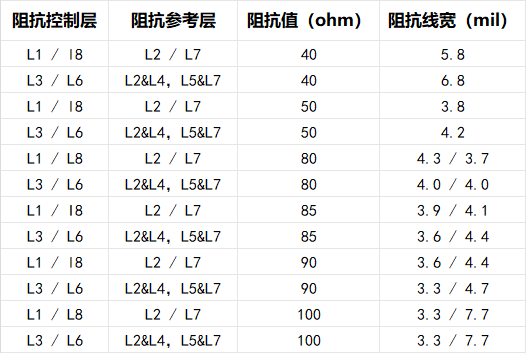

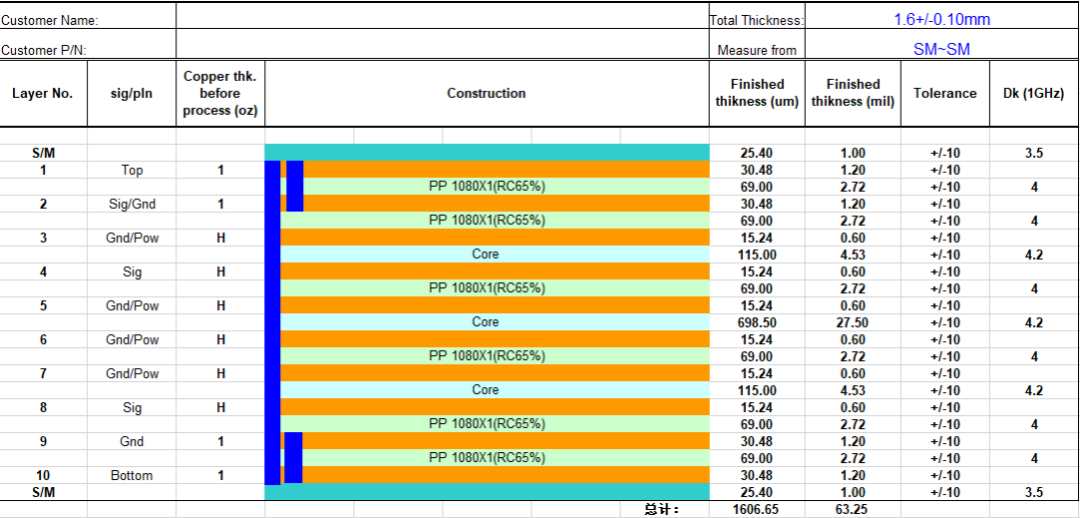

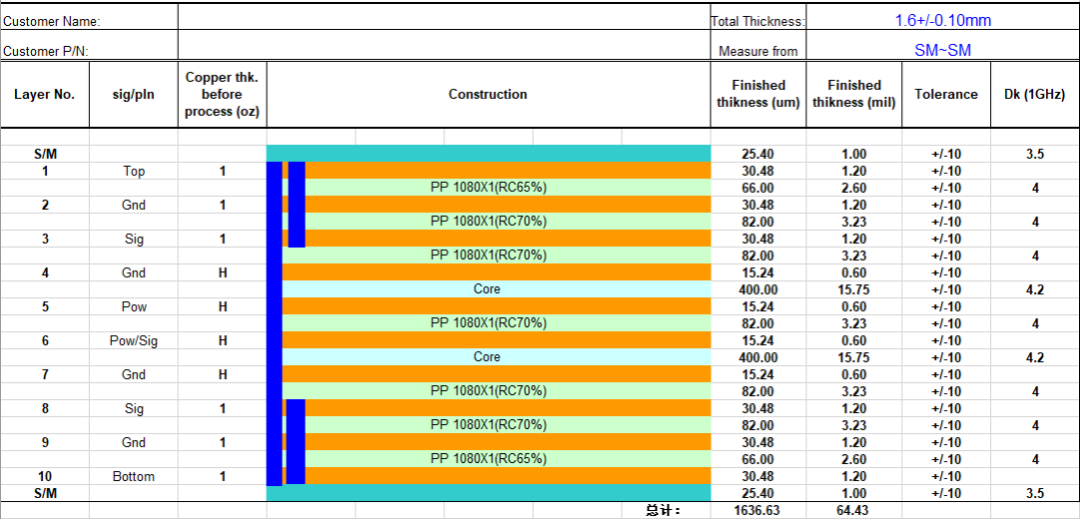

10層1階HDI板1.6mm厚度疊層與阻抗設計

在10層1階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。

建議層疊為TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建議采用1oZ,其它內層采用HoZ。

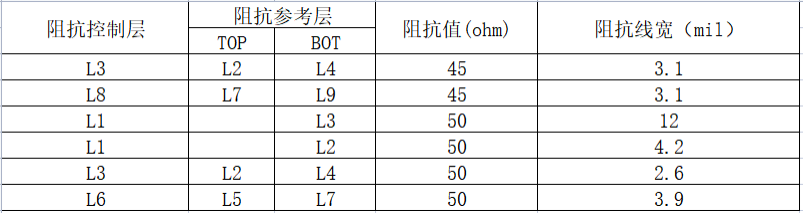

板厚推薦疊層如下圖(上)所示(10層1階HDI板疊層設計),阻抗線寬線距如下圖(下)所示(10層1階HDI板阻抗設計)。

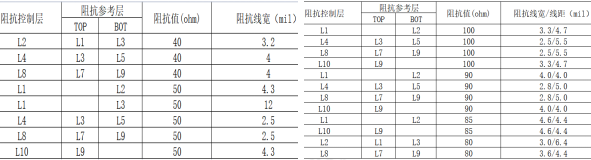

10層2階HDI板1.6mm厚度疊層與阻抗設計

在10層2階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。

建議層疊為TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建議采用1oZ,其它內層采用HoZ。

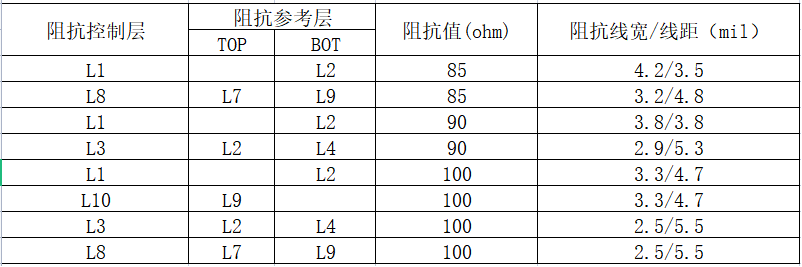

板厚推薦疊層如下圖(上)所示(10層2階HDI板疊層設計),阻抗線寬線距如下圖(中、下)所示(10層2階HDI板單端、差分阻抗設計圖)。

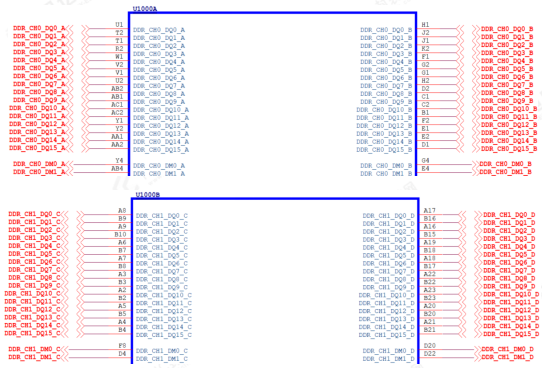

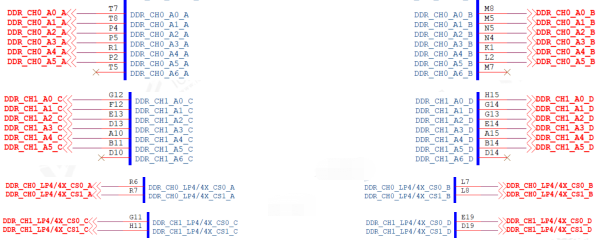

DDR電路阻抗線與阻抗要求

所有通道數據DQ、DM單端信號阻抗40歐姆,如果疊層無法滿足40歐目標阻抗,至少保證阻抗滿足45ohm±10%,40歐目標阻抗信號余量會更大,45歐目標阻抗信號余量會更小,如下圖是CH0與CH1通道數據DQ、DM阻抗線。

所有通道地址、控制單端信號阻抗40歐姆,如下圖是CH0與CH1通道地址、控制阻抗線。

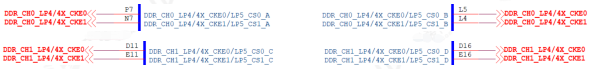

CKE單端信號阻抗50歐姆,如下圖是CH0與CH1通道CKE阻抗線。

所有通道數據鎖存信號DQS與時鐘差分信號阻抗80歐姆,如果疊層無法滿足80歐目標阻抗,至少保證阻抗滿足90ohm±10%,如下圖是CH0與CH1通道DQS與CLK差分阻抗線。

阻抗的知識點非常多,相信大家也竟然為此困擾,這里推薦一款可以一鍵智能計算阻抗自動疊層的工具:華秋DFM軟件,使用其阻抗計算功能,可以高效輕松反算和計算所需阻抗和線寬線距等。

華秋DFM軟件是國內首款免費PCB可制造性和裝配分析軟件,擁有300萬+元件庫,可輕松高效完成裝配分析。其PCB裸板的分析功能,開發了19大項,52細項檢查規則,PCBA組裝的分析功能,開發了10大項,234細項檢查規則。

基本可涵蓋所有可能發生的制造性問題,能幫助設計工程師在生產前檢查出可制造性問題,且能夠滿足工程師需要的多種場景,將產品研制的迭代次數降到最低,減少成本。

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

專屬福利

上方鏈接下載還可享多層板首單立減50元

每月1次4層板免費打樣

并領取多張無門檻“元器件+打板+貼片”優惠券

審核編輯 黃宇

-

電路

+關注

關注

172文章

5852瀏覽量

171945 -

阻抗

+關注

關注

17文章

941瀏覽量

45835 -

DDR

+關注

關注

11文章

711瀏覽量

65237 -

疊層

+關注

關注

0文章

28瀏覽量

9829

發布評論請先 登錄

相關推薦

淺談PCB疊層設計原則及阻抗設計

DDR電路的疊層與阻抗設計

DDR電路的疊層與阻抗設計

評論