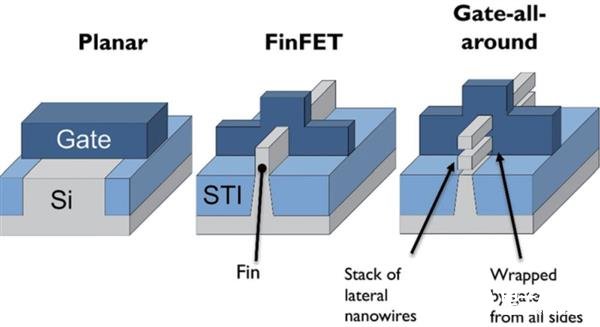

GAA,一般指全環繞柵極晶體管(Gate-All-Around FET)。GAA被廣泛認為是鰭式結構(FinFET)的下一代接任者。下面簡單介紹一下GAA器件集成工藝與關鍵挑戰。

GAA器件集成工藝——主要流程與關鍵工藝

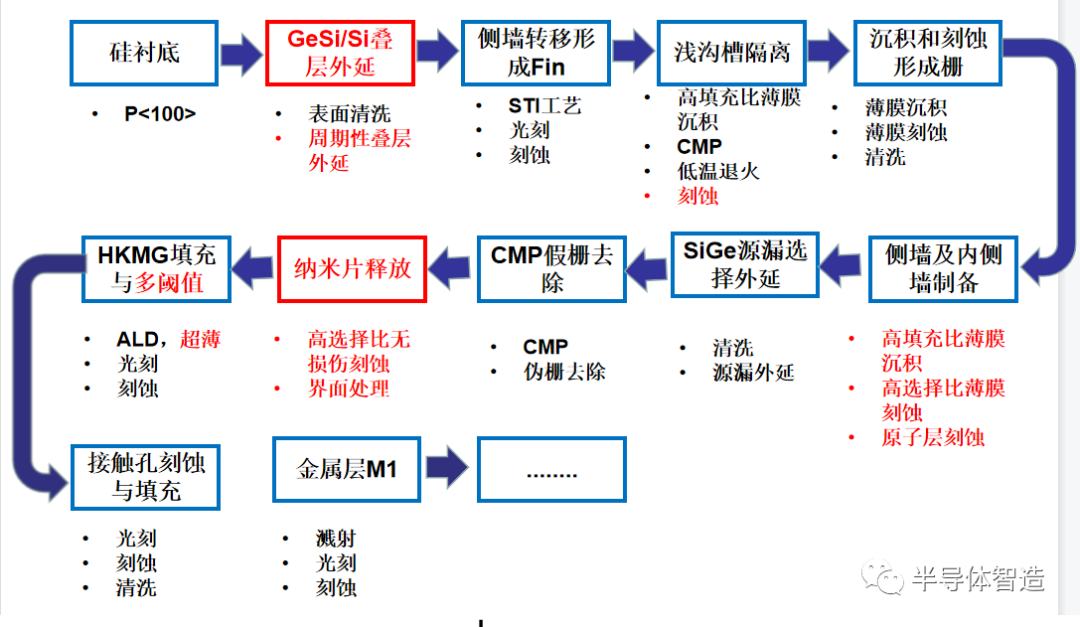

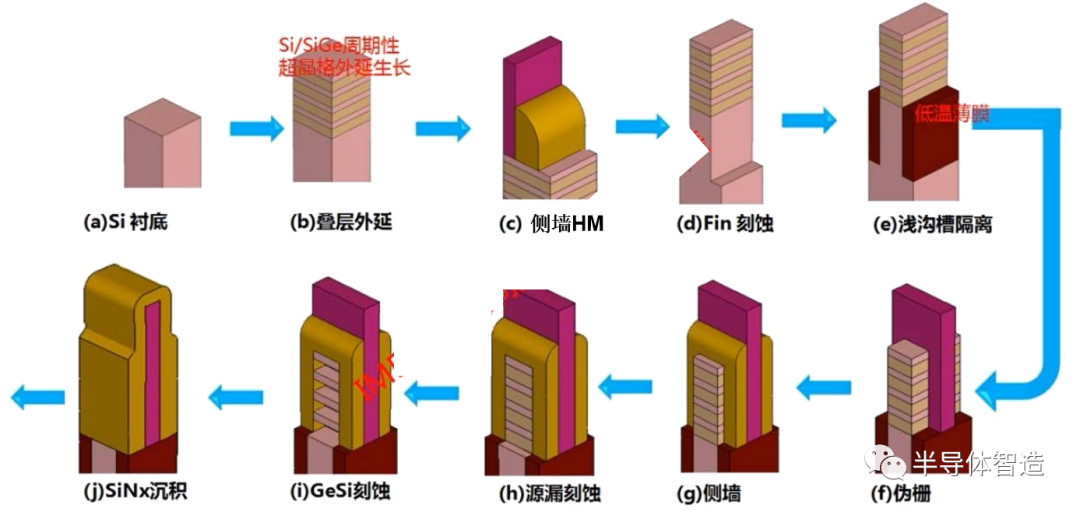

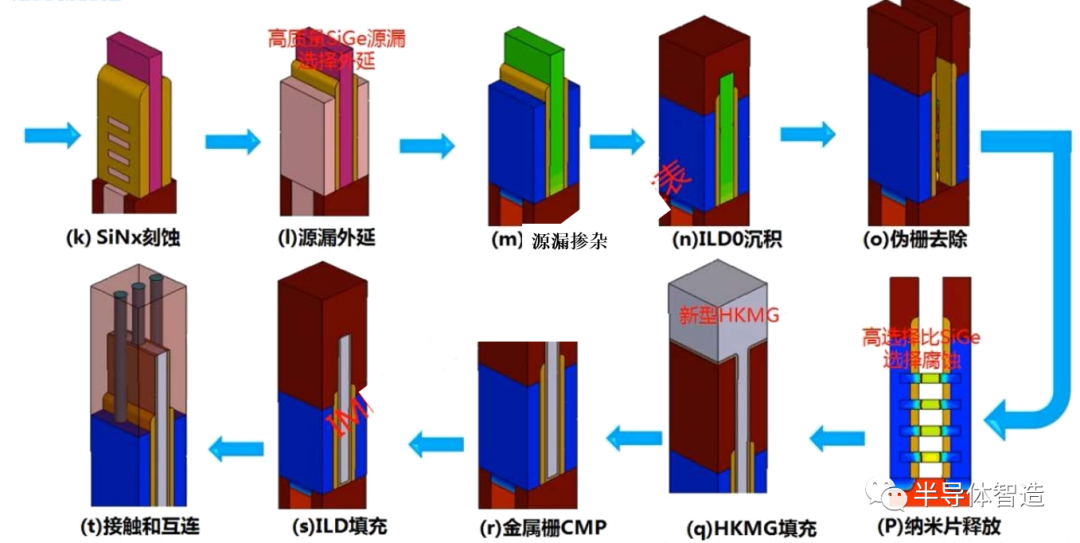

環柵硅納米片(GAA NS)主要流程工藝

硅納米片GAA器件——主要工藝流程

硅納米片GAA器件——關鍵技術與挑戰

3nm技術節點GAA器件工藝制備和集成應用所面臨的挑戰

N/P MOS性能差異大(Si-100)/<110>溝道)

前道Ge元素具有沾污風險,限制工藝溫度

內側墻集成挑戰大,工藝不成熟

HKMG多閾值實現困難(空間有限)

高選擇比納米溝道釋放工藝(干法、濕法、對形貌、表面等要求)

難以滿足電路所有器件需求,如I/O、HV等)

底層納米片溝道非理想因素(寄生電阻、閾值漂移)

寄生電容與寄生電阻優化挑戰大

硅納米片GAA器件——納米線釋放工藝優化

GAA堆疊納米片溝道釋放工藝優化

采用GeSi高選擇腐蝕溶液,腐蝕速率不斷增加,48h后,速率飽和

GeSi RTA退火在750度時腐蝕速率最慢,溫度高于或低于750度,腐蝕速率都會加快

GeSi層腐蝕的速率與其厚度呈正相關

硅納米片GAA器件——熱預算控制優化

GAA堆疊納米片器件熱預算控制優化

Ge/Si在900度以下,幾乎沒有相互擴散

Ge/Si在900度時,出現相互擴散

Ge/Si在1000度時,嚴重相互擴散

光刻工藝——挑戰及技術難點

3nm技術節點GAA器件→更小的溝道及金屬線尺寸,并且NS具有寬度變化性

M0、柵和Fin制備等關鍵層需要使用高級極紫外光刻(EUV)技術

3nm技術節點gate pitch為42nm,器件最小周期為21nm

必需使用EUV光刻技術,并結合HNA、DP技術

EUV計算光刻技術是關鍵環節之一

源漏選擇性外延——挑戰及技術難點

SiGe外延工藝選擇性挑戰:多介質表面(SiN,SiO,Dummy Gate)和不同晶面生長

圖形密度效應影響:SiGe的厚度和濃度分布不均勻

SiGe源漏原位摻雜:更高的Ge組分(大于40%),更高的摻雜濃度,更低的電阻率

GAA中溝道橫向外延與縱向外延的質量控制

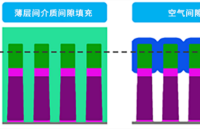

內側墻工藝——挑戰及技術難點

內側墻控制NS溝道在釋放工藝中向源漏方向的橫向腐蝕

該工藝包含高選擇比各向異性刻蝕、高填充比薄膜沉積和高質量選擇外延等多個具有挑戰性的工藝環節

高選擇比SiGe空腔刻蝕(對Si、硬掩模、STI等露出物高選擇比)

側面空腔保形性填充( -般ALD SiNx材料) ;

高選擇比內側墻刻蝕(露出Si溝道,對Si、SiO2、 SiGe同時高選擇比)

源漏的選擇性外延( SiGe源漏外延并和溝道良好連接)

原子層刻蝕工藝——挑戰及技術難點

原子層刻蝕(ALE) 為ALD的逆過程,其挑戰和難點:

新型三維器件結構溝道及很多精細化圖形制備需要原子層刻蝕技術;

反應源的尋找及自限制條件是其技術難點

新型金屬柵材料、新型襯底材料(Ge , SiGe, III-V族)等需要新刻蝕方案;

刻蝕過程中要求原子級精細化的無損刻蝕

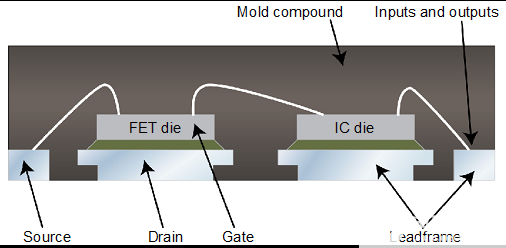

高k介質金屬柵——挑戰及技術難點

GAA器件中HKMG的集成挑戰

挑戰1 :堆疊NW/NS溝道中HK/MG填充空間狹窄,受限于Lg和Tsus

挑戰2 :傳統通過TiN/TaN及功函數層的薄膜厚度來實現多閾值面臨極大挑戰

挑戰3 :不同寬度(不同功能)的納米片GAA器件對HKMG的功函數需求不同

解決方案:設計簡單的HKMG結構,ALD生長超薄膜實現保型覆蓋,偶極子實現多閾值調節等

低阻接觸工藝——挑戰及技術難點

源漏接觸電阻成為制約器件性能提升的重要因素降低源漏接觸電阻率

低阻接觸工藝的關鍵挑戰:

接觸面積的縮減

反應源的尋找及自限制條件影響金屬與n-SiGe和p-SiGe形成極低接觸電阻率

源漏雜質固濃度限制

高質量的金-半接觸界面

自對準接觸工藝——挑戰及技術難點

自對準接觸孔工藝(Self Aligned Contact, SAC), 減小接觸尺寸,提升集成

該技術的關鍵是解決接觸孔層與柵極層光刻對準偏差,依靠設計合適的膜層,和開發特殊的接觸孔刻蝕工藝來獲得自對準效果

孔刻蝕對柵極頂部側墻材料的高選擇比(尤其是角位置)是一個較大的技術

自對準接觸工藝——研究進展

SAC技術早期用在DRAM上,采用C4F8/CO, C4F8/CH2F2氣體刻蝕ILD層; 7nm以下F inFET和GAAI藝也必須用到SAC工藝

可靠性技術——必要性

可靠性技術研發是新器件技術走向產業化規模應用的一個重大瓶頸問題

可靠性技術研發涉及多個環節,在尺寸縮小、走向系統集成的未來面臨更多挑戰

縮短研發周期,提前介入新器件技術可靠性研究十分必要

國際上針對先進器件的可靠性研發細節都是“黑盒子”

可靠性技術——挑戰及技術難點

新器件在開展可靠性研究上面臨諸多技術挑戰:

新結構導致可靠性問題更加嚴重和錯綜復雜; →表征技術/壽命預測難題?新材料導致可靠性退化機理分析存在更多未知因素; →機理分析難題

器件的小尺寸對可靠性測試精度和準確度提出更高要求: →測試技術難題

可靠性技術——設備需求

先進器件的可靠性量測對測試設備精度提出更高的需求:

更低的電流值/電容值:小尺寸器件量測;

更強的屏蔽效果:降低外界干擾/噪聲量測;

納秒級的快速測量系統:準確評估器件可靠性,降低恢復特性;

-

工藝

+關注

關注

4文章

578瀏覽量

28752 -

晶體管

+關注

關注

77文章

9634瀏覽量

137848 -

FET

+關注

關注

3文章

630瀏覽量

62890 -

光刻工藝

+關注

關注

1文章

28瀏覽量

1819 -

GAA

+關注

關注

2文章

36瀏覽量

7437

原文標題:GAA技術--3nm器件集成工藝與關鍵挑戰

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

美國從EDA下絆子,3nm工藝關鍵技術GAA將與中國無緣?

創新混頻器是射頻電路設計的關鍵器件之一

LTE基站發射機的RF IC集成設計方案

RF電路的集成挑戰如何解決

歸納碳化硅功率器件封裝的關鍵技術

MEMS與IC集成工藝介紹 NEMS器件在IC 中的應用

5nn重奪領導地位 GAA工藝性能提升將會更明顯

Intel放棄FinFET晶體管轉向GAA晶體管 GAA工藝性能提升或更明顯

GAA器件集成工藝與關鍵挑戰

GAA器件集成工藝與關鍵挑戰

評論