何為信號完整性的分析

信號完整性包含:波形完整性(Waveform integrity)時序完整性(Timing integrity)電源完整性(Power integrity)信號完整性分析的目的就是用小的成本,快的時間使產品達到波形完整性、時序完整性、電源完整性的要求;我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,所以我們研究訊號完整性就需要研究差分訊號,訊號的反射,訊號的串擾等等參數,今天我們系統性的回顧下!

1

信號完整性的定義

信號完整性(Signal Integrity):就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳送到接收端,我們就稱該信號是完整的,當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性,當信號不能正常響應時,就出現了信號完整性問題。

何為高速差分訊號傳輸

隨著信號速率的提高,差分互連得到越來越多的應用。實際上差分對是具有耦合的傳輸線,其主要用的是差分信號的特征,用差分對來實現。差分信號利用兩個輸出驅動來驅動兩條傳輸線。其中一根攜帶信號,另一根攜帶它的互補信號,兩條傳輸線上面的壓差就是需要傳輸的信息。

在差分信號的傳輸過程中,主要是以兩條傳輸線為傳輸載體,差分驅動器輸出的是邊緣能夠對齊的兩個信號,但是正好方向相反,如下圖所示。兩個高速信號分別傳輸,接收端在信號抵達接收器時對兩個信號作差分檢測,得到的差值就是差分信號,但是今天我們聊的是信號完整性,就是我們常說的SI參數,其名詞解釋就是指訊號線上的信號質量,訊號完整性不是由單一某一個因素導致的,而是訊號通訊過程中和設計中可能引起的多種因素引起的,我們也需要知道相關測試參數名詞的解釋!

傳輸線(Transmission Line):由兩個具有一定長度的導體組成回路的連接線,我們稱之為傳輸線,有時也被稱為延遲線。

上升/下降時間(Rise/Fall Time):信號從低電平跳變為高電平所需要的時間,通常是量度上升/下降沿在10%-90%電壓幅值之間的持續時間,記為Tr。

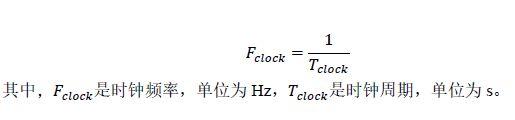

截止頻率(Knee Frequency):這是表征數字電路中集中了大部分能量的頻率范圍(0.5/Tr),記為Fknee,一般認為超過這個頻率的能量對數字信號的傳輸沒有任何影響。

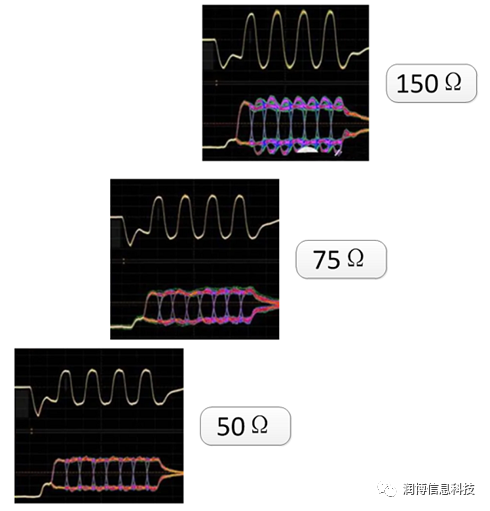

特征阻抗(Characteristic Impedance):交流信號在傳輸線上傳播中的每一步遇到不變的瞬間阻抗就被稱為特征阻抗,也稱為浪涌阻抗,記為Z0。可以通過傳輸線上輸入電壓對輸入電流的比率值(V/I)來表示。

傳輸延遲(Propagation delay):指信號在傳輸線上的傳播延時,與線長和信號傳播速度有關,記為tPD。

趨膚效應(Skin effect):指當信號頻率提高時,流動電荷會漸漸向傳輸線的邊緣靠近,甚至中間將沒有電流通過。與此類似的還有集束效應,現象是電流密集區域集中在導體的內側。

反射(Reflection):指由于阻抗不匹配而造成的信號能量的不完全吸收,發射的程度可以有反射系數ρ表示。

串擾:串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲干擾,這種干擾是由于傳輸線之間的互感和互容引起的。

屏蔽效率(SE):是對屏蔽的適用性進行評估的一個參數,單位為分貝。吸收損耗:吸收損耗是指電磁波穿過屏蔽罩的時候能量損耗的數量。

反射損耗:反射損耗是指由于屏蔽的內部反射導致的能量損耗的數量,他隨著波阻和屏蔽阻抗的比率而變化。

校正因子:表示屏蔽效率下降的情況的參數,由于屏蔽物吸收效率不高,其內部的再反射會使穿過屏蔽層另一面的能量增加,所以校正因子是個負數,而且只使用于薄屏蔽罩中存在多個反射的情況分析。

差模EMI:傳輸線上電流從驅動端流到接收端的時候和它回流之間耦合產生的EMI,就叫做差模EMI。共模EMI:當兩條或者多條傳輸線以相同

2

反射系數

首先我們說一下訊號完整性里面最重要的參數之一:

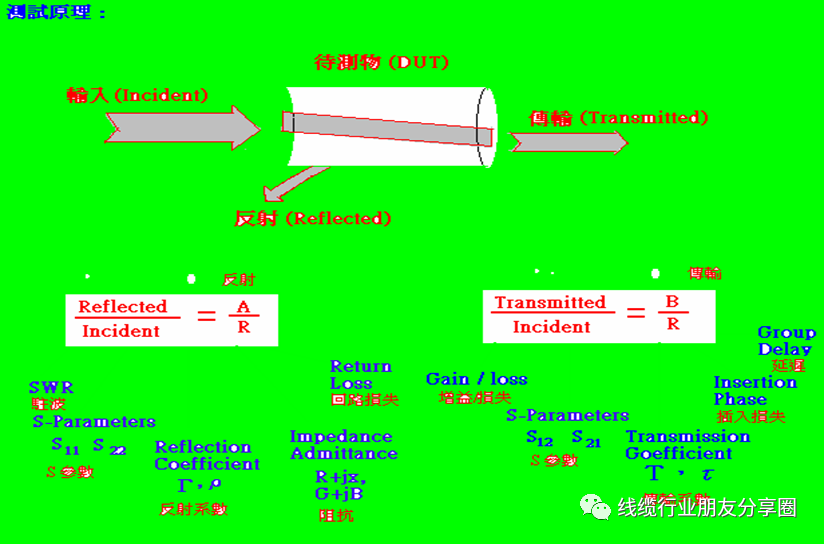

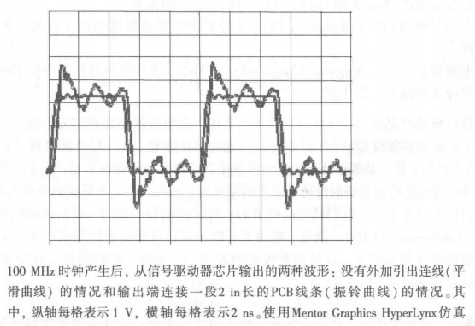

反射:反射--初始波

當驅動器發射一個信號進入傳輸線時,信號的幅值取決于電壓、緩沖器的內阻和傳輸線的阻抗。驅動器端看到的初始電壓決定于內阻和線阻抗的分壓。S參數都是帶限的,即每個S參數都有一個截斷頻率fstop,S參數只有頻率低于fstop的信息。在頻域-時域轉換的時候,這種終止會引入截斷誤差。在時域反射曲線中表現為以1/fstop的振蕩,即紋波。這個振蕩的幅度,取決于輸入上升沿的頻譜。越快的上升沿,時域反射的振蕩會越強。因此選擇合適的上升沿非常重要。一般地,截斷頻率為fstop的S參數在求解時域反射的時候,可以用的最快上升沿(20-80%)為:比如一個fstop = 20GHz 的S參數,如果上升沿超過25ps(20-80%),那么輸出的時域反射曲線就會出現較明顯的紋波。如果上升沿慢于25ps,那么紋波會很小而可忽略。

反射產生的原因

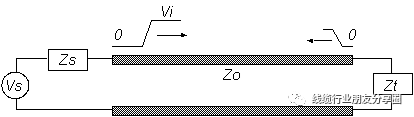

當發送器件將數字信號送到互連線上時,初始信號大小( )取決于發送器件的電壓(

)取決于發送器件的電壓( )、源內阻(

)、源內阻( )和互連線的特性阻抗(

)和互連線的特性阻抗( ),如圖1所示:

),如圖1所示:

圖1 互連線上的反射現象

其等于互連線特性阻抗在它與源內阻的分壓,如式(1),

如果互連線終端接到一個與互連線特性阻抗( )精確匹配的阻抗,那么互連線上的電壓保持為,直到發送器件再次發送信號。而如果互連線終端所接阻抗不為

)精確匹配的阻抗,那么互連線上的電壓保持為,直到發送器件再次發送信號。而如果互連線終端所接阻抗不為 ,而為

,而為 ,則傳輸到終端的信號一部分端接到地,而其余的部分將朝發送器件方向反射。反射信號分量的多少取決于負載端反射系數

,則傳輸到終端的信號一部分端接到地,而其余的部分將朝發送器件方向反射。反射信號分量的多少取決于負載端反射系數 .

.

于是,初始入射電壓達到終端時,信號的一部分

,將返回發送器件,并與入射電壓疊加,這時負載端的電壓為

,將返回發送器件,并與入射電壓疊加,這時負載端的電壓為 +

+

,如果反射分量

,如果反射分量

達到發送器件,發現源內阻也與特性阻抗不相等(匹配),

達到發送器件,發現源內阻也與特性阻抗不相等(匹配),

會被再一次的反射,反射信號的多少取決于源端反射系數

會被再一次的反射,反射信號的多少取決于源端反射系數 .

.

這時源端的電壓則變為 +

+

+

+ +

+

反射會在互連線上不斷地進行,直到達到穩定,源端和負載端的穩定電壓都為,

反射會在互連線上不斷地進行,直到達到穩定,源端和負載端的穩定電壓都為,

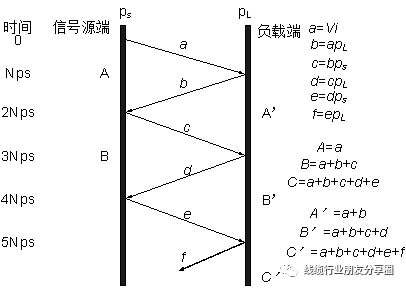

格形圖是在源內阻和端接負載都為線性時理解反射產生機理的一種方法。如下圖所示

如圖中,左邊豎線代表互連線的源端,右邊豎線代表負載端,而兩條豎線之間的斜線代表信號在源端和負載端來回反射,圖中自頂向下,表示時間的增加,相鄰時刻之間的時間增量等于互連線的延遲。另外,圖中兩豎線頂端標有相應的反射系數,小寫字母表示互連線上傳播的反射信號大小,包括從源端和從負載端反射回的,大寫字母代表源端的電壓,帶撇的大寫字母表示負載端的電壓。

3

串擾參數

串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲。串擾是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對象(Victim)上引起感應電流從而導致的電磁干擾。而感性耦合則是由于干擾源上的電流變化產生的磁場在被干擾對象上引起感應電壓從而導致的電磁干擾。因此,信號通過一導體時會在相鄰的導體上引起兩類不同的噪聲信號:容性耦合信號和感性耦合信號。

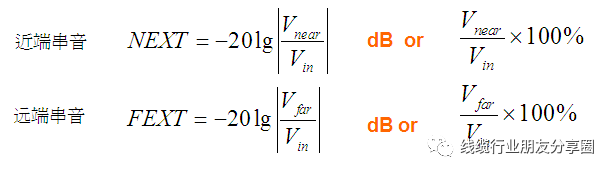

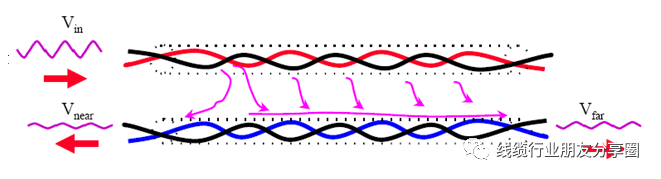

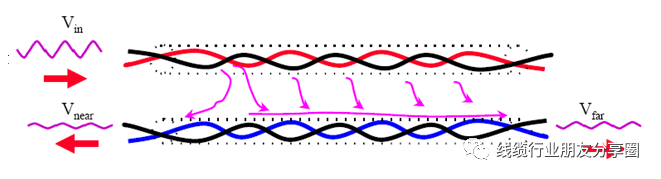

串音主要分為近端串音和遠端串音兩大類;它們的峰值定義為,近端串音係數NEXT和遠程串音係數FEXT;其中Vin為動態線中信號電壓;Vnear和Vfar為靜態線上近端和遠端測得的串音電壓.

計算公式如下(串音—Cross Talk 單位—dB)

一對訊號線傳輸時的高頻電容電感效應與 Impedance匹配效應,產生對相鄰訊號線造成的干擾現象。

NEXT(Near End Cross Talk)---近端串音,發生在傳輸源一端的串音現象

FEXT(Far End Cross Talk)---遠端串音,發生在接收一端的串音現象

dB=20 Log(V1/V0)

V1-相鄰訊號線檢出電壓

V0-原訊號源輸出電壓

兩線路之間互相干擾的電磁雜訊,一般會隨著頻率之昇高而增加。

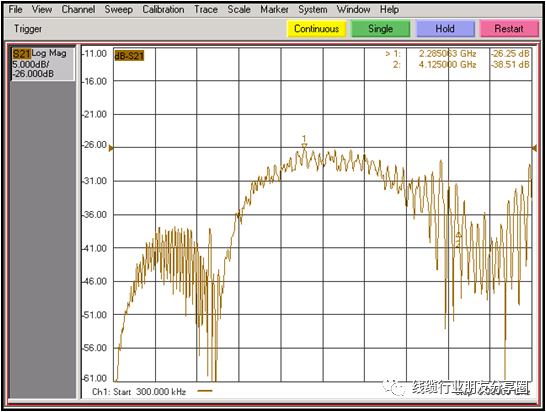

其量測可以NA或TDR來量測,其計算公式如下:

如果Xtalk數值越趨近于0 dB(or近100%)時,表示雜訊干擾的情況越嚴重,反之,Xtalk dB數值越大(or近0%)時,表示雜訊干擾的情況越少

實際量測中的串音測試圖形

SSN(同步開關噪音)

開關噪音由差分對間的感性耦合引起,當傳輸線上電流變化時,會在鄰近的傳輸線上耦合出感 應電壓,并激起感應電流,對鄰近傳輸線上的信號產生干擾.

解決方式:

由于差分信號的特性,可以激勵差分對進入奇模模態,在此模態下, 差分對本身對耦合噪音有很好的抑制作用.另外可以通過對線包鋁箔屏蔽來減弱對其他鄰近差分對的干擾.

在高頻通信中,我們更關心的是串音干擾而不是SSN;串音干擾是相鄰傳輸線對內或對間由于寄生電感,電容耦合產生的噪音;對傳輸線上的信號影響很大;必須加以控制;否則會引起信號波形的嚴重失真,導致接收端誤判斷.

串音產生原理

串音干擾可以從電容電感耦合角度去理解,也可以從差分信號和共模信號分量角度去理解.

耦合角度描述:

當動態線上有信號通過時,在信號的上升延區域(即電壓電流變化的區域).由于線對間的互感和互容的耦合作用,在靜態線上將感應出電流,由于噪音電流在靜態線上每個方向上感受到的阻抗都相同,所以前向和后向的電流量將相等. 其中一半向后流回到近端,產生近端串音;另一半向前流動到遠程,產生遠程串音.

舉例分析串音產生的機理和改善方式

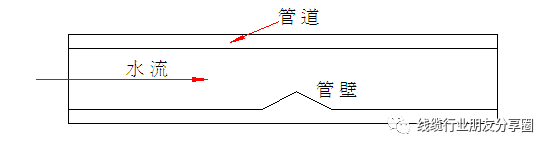

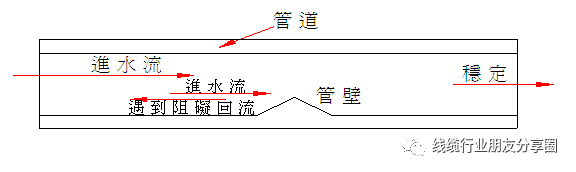

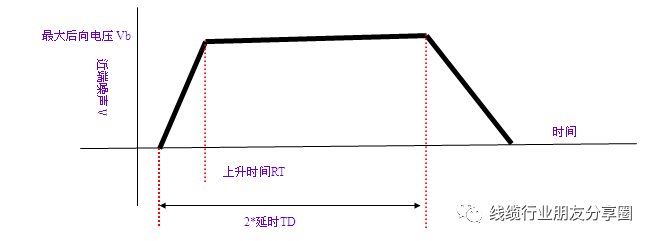

管道裡的水向前流,過程中由于管道孔徑或管道有凸起物等諸多因素讓水流的速度發生有不穩定的現象,但是當到達終點接收端后,有個穩定的接收后,其輸入的水流將達到一個穩定狀態,但是在過程中仍有由于遇到障礙而往后流的水流向供水端,這段額外的阻止時間為延時TD,近端串音就是水流從不穩定額外的阻止時間并持續2*TD的時間,如下圖解說:

當兩條傳輸線靠近時,互容和互感將增加,從而使NEXT增加)近端串音:

當信號前沿傳輸了一個飽和長度后,近端的電流將達到一個穩定值;而當動態線上的信號到達遠端端接電阻后;就不再有耦合噪音電流,但是靜態線上還有后向電流流向靜態線的近端,這段額外時間等于時延TD.;近端串音就是耦合電流上升到一個恒定值并持續2*TD,然后下降到0,其中上升時間等于信號的上升時間,如下圖解說

遠程串音:耦合到靜態線上前向傳播的噪音,移動速度與動態線上的信號前沿向遠端傳播的速度相同.在靜態線上的每一步,一半噪音電流會迭加在已經存在的沿線噪音上.直到信號前沿到達遠端,才有電流出現.即信號達到遠端時,遠端噪音同時到達.因此遠端噪音電流為一個很短的負向脈衝,持續時間等于信號的上升時間TD.近端和遠端串音的特徵,決定了遠端串音將在高頻率段產生很大威脅,而近端串音則在中頻率段影響較大.

從差分信號分量和共模信號分量角度描述:

近端串音:

差分信號分量和共模信號分量在差分對上所感受到的阻抗不同,這 一阻抗上的差異將導致,靜態線產生近端串音.若阻抗上的這一差異越大則NEXT將越大.

遠程串音:

由于共模信號分量和差分信號分量電力線分佈不同,所感受到的有效介電係數不同,導致它們的傳播速度不同.差分信號分量將先到達遠端,而共模信號分量稍晚點到達遠端.它們的差值將導致遠程串音,若這一速度差異越大將導致遠端串音能量越大,FEXT越大;串音干擾由于相鄰線間的耦合產生.耦合度越高,串音干擾越大;頻率越高,串音干擾越大;電容穩定性越差,串音越嚴重;此外,低特性阻抗有利于低串音,絕緣材料介電係數越小,串音越低。

-

信號

+關注

關注

11文章

2739瀏覽量

76170 -

時序

+關注

關注

5文章

370瀏覽量

37186 -

電路系統

+關注

關注

0文章

67瀏覽量

12872

發布評論請先 登錄

相關推薦

信號完整性分析科普

信號完整性分析科普

評論