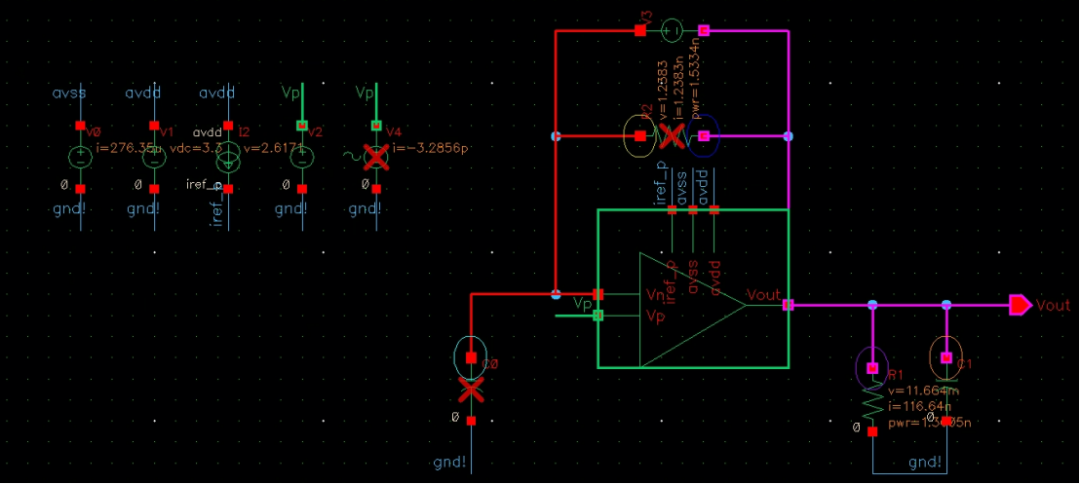

stb分析可以得到環路增益的bode圖,但卻不能看到環路中其他位置的AC增益大小,這在需要分析不同級的放大倍數時造成了困難。解決這個問題,可以按照下圖所示的方法設計testbench。

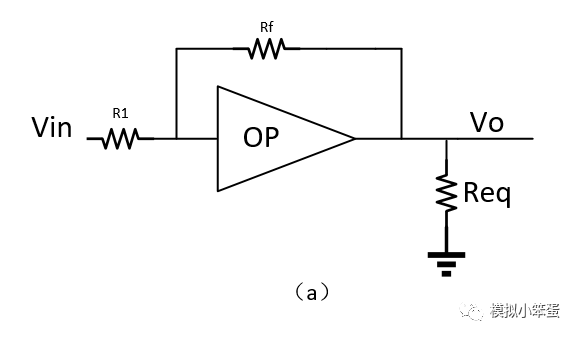

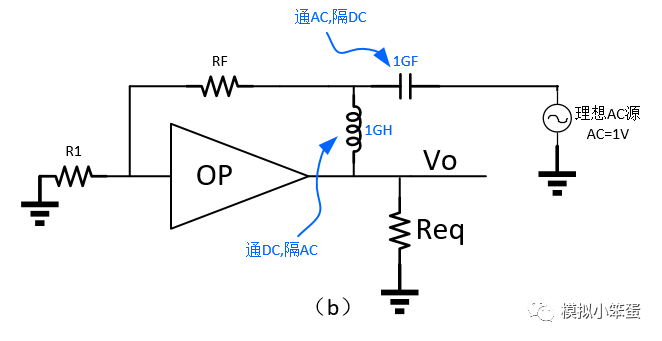

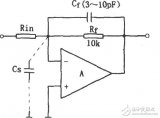

圖1

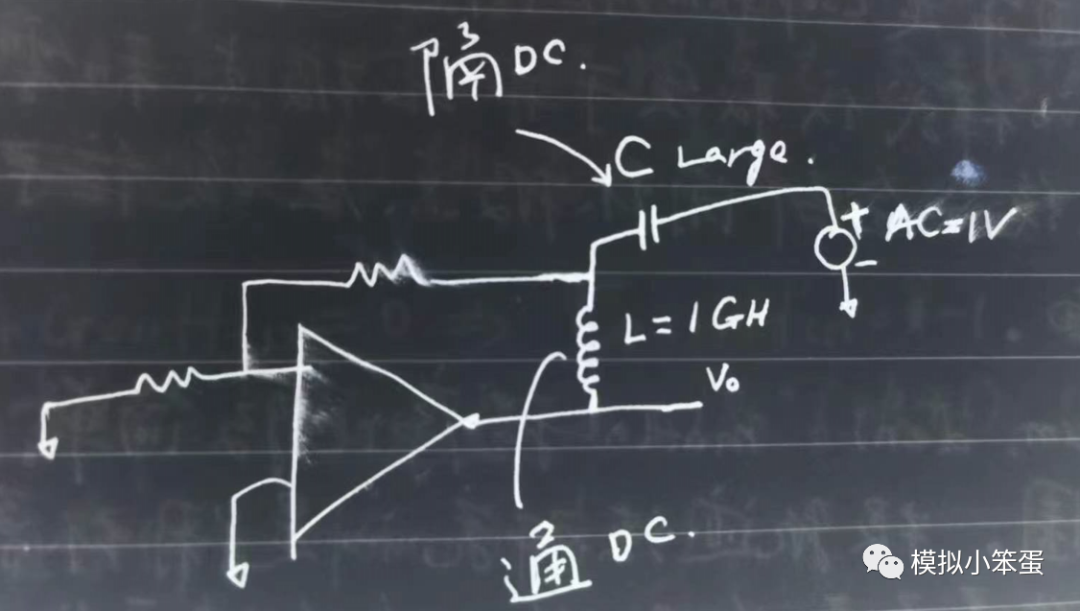

以圖1a為例,對環路斷環進行仿真時,除了用stb分析方式之外,可以用如圖1b所示添加L、C的辦法進行環路增益仿真。L的作用是通直流交流,所以電路可以認為存在直流連接,此時負反饋環路認為沒有斷開,因此可以保證電路直流工作點的正常。但交流時,由于L設定值很大,呈現出很大的交流阻抗,相當于“斷路”,所以在交流角度此處路徑又是斷開的。再看電容C,它的作用是通交流隔直流。直流時,所加的AC激勵源直流電平被電容隔開,不會對環路造成影響。交流時的信號可以通過電容、RF、R1的網絡施加到OP輸入端。

使用圖1的仿真辦法,激勵源AC=1V,收集到的Vo即為環路增益大小。除了這點之外,可以看到電路中任何一點的小信號增益和相位情況,這一點對分析電路尤其有幫助。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

運放

+關注

關注

47文章

1152瀏覽量

52975 -

仿真

+關注

關注

50文章

4043瀏覽量

133416 -

AC

+關注

關注

1文章

588瀏覽量

84303 -

負反饋

+關注

關注

6文章

216瀏覽量

30020

發布評論請先 登錄

相關推薦

運放-單電源運放和雙電源運放

本文轉自:http://www.sohu.com/a/321387578_100281310(1)分析分析:單電源運放和單電源運

發表于 11-06 18:21

?56次下載

運放的共模抑制比高有什么作用?共模抑制比比較高的運放有哪些啊?

運放的共模抑制比高有什么作用?共模抑制比比較高的運放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一個衡量

L、C對運放AC分析的輔助作用

L、C對運放AC分析的輔助作用

評論