在光電子融合中,硅光子學(xué)發(fā)揮著核心作用。硅光子學(xué)是一種利用CMOS制程技術(shù),支援半導(dǎo)體工業(yè)在硅基板上整合光接收元件、光調(diào)變器、光波導(dǎo)和電子電路等元件的技術(shù)。負(fù)責(zé)轉(zhuǎn)換光訊號(hào)和電訊號(hào)的光收發(fā)器,和集成電路芯片的混合,已逐漸轉(zhuǎn)變?yōu)榻庋b光學(xué)元件和共封裝光學(xué)元件。最終的光電融合是3D共封裝光學(xué),即三維整合。可以毫不夸張地說,基于硅光子的光電子融合,將會(huì)是未來計(jì)算機(jī)系統(tǒng)和資訊網(wǎng)路的關(guān)鍵技術(shù)。

提高芯片的處理速度,對(duì)于提高計(jì)算機(jī)性能至關(guān)重要,但由于簡(jiǎn)單的小型化和高積集度有先天性的限制,因此平行處理器架構(gòu)和3D電路結(jié)構(gòu)的發(fā)展正被半導(dǎo)體產(chǎn)業(yè)所關(guān)注。這樣的技術(shù)發(fā)展帶動(dòng)了芯片間所需訊息傳輸頻寬的增加,預(yù)計(jì)2025-2030年對(duì)頻寬的需要將超過10Tbit/s。然而,傳統(tǒng)電線的傳輸速度有10Tbit/s左右的限制,而且功耗也是一個(gè)嚴(yán)重的問題。

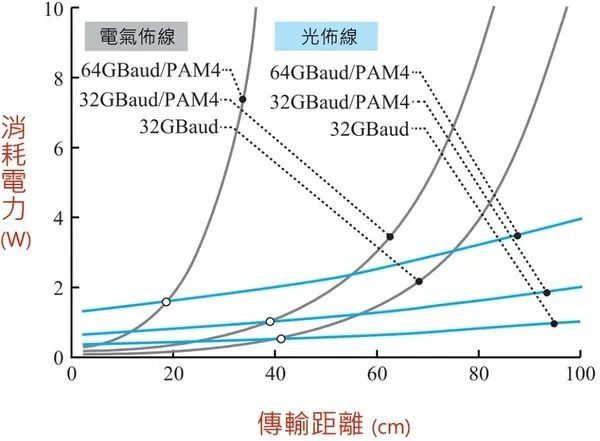

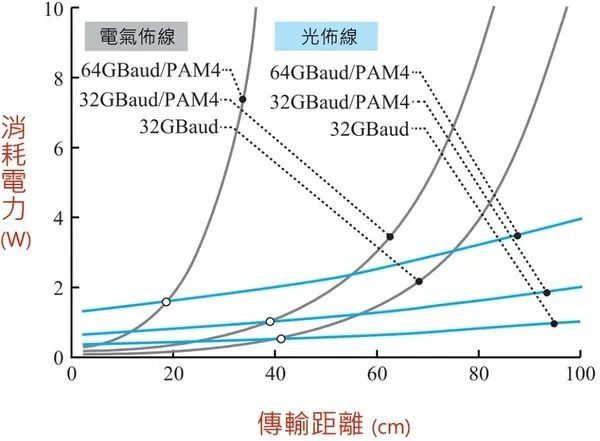

所以為了突破頻寬限制和功耗的障礙,高科技產(chǎn)業(yè)對(duì)光電融合的期望越來越高,這使得光訊號(hào)和電訊號(hào)密不可分。光電融合預(yù)計(jì)將擴(kuò)展到連接服務(wù)器中CPU的布線、連接CPU和電路的I/O,甚至CPU內(nèi)部的布線。圖一顯示了電氣布線和光布線的功耗與傳輸距離的關(guān)系。同時(shí)可以看發(fā)現(xiàn),當(dāng)傳輸頻寬增加時(shí),即使距離很短,光布線也變得更有優(yōu)勢(shì)性。

圖一: 顯示了電氣布線和光布線的功耗與傳輸距離的關(guān)系性。(source:電子情報(bào)通信學(xué)會(huì)-日本;作者整理)

云服務(wù)和5G需求帶動(dòng)硅光子成長(zhǎng)

根據(jù)日本Research Nester的一份關(guān)于硅光子的市場(chǎng)報(bào)告中顯示,2022年硅光子市場(chǎng)規(guī)模約為20億美元。預(yù)計(jì)到2035年底,硅光子全球市場(chǎng)規(guī)模將達(dá)到550億美元,2023-2035年間的復(fù)合年增長(zhǎng)率高達(dá)29.80%。

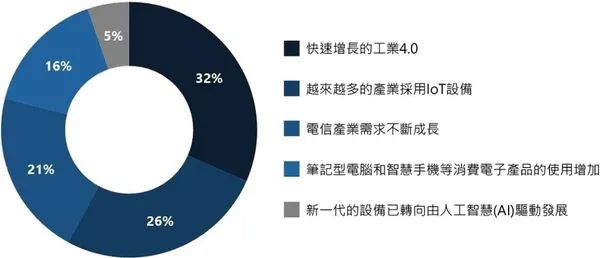

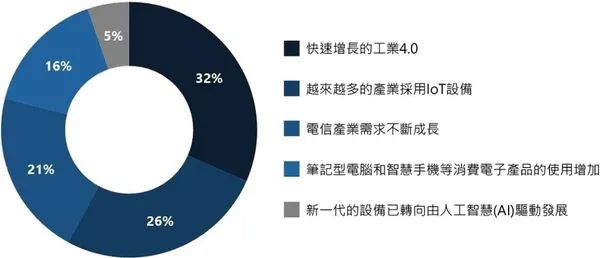

市場(chǎng)增長(zhǎng)可歸因于對(duì)基于云端的服務(wù)和5G技術(shù)的需求激增,以及光電子技術(shù)的進(jìn)步。整體因素包括了,快速成長(zhǎng)的工業(yè)4.0、越來越多的產(chǎn)業(yè)采用IoT設(shè)備、電信產(chǎn)業(yè)需求不斷成長(zhǎng)、筆記型電腦和智慧手機(jī)等消費(fèi)電子產(chǎn)品的使用增加,以及新一代的設(shè)備已轉(zhuǎn)向由人工智慧(AI)驅(qū)動(dòng)發(fā)展(圖二)。

圖二: 對(duì)于硅光子市場(chǎng)成長(zhǎng)的貢獻(xiàn)因素。

(source:Research Nester;作者整理)

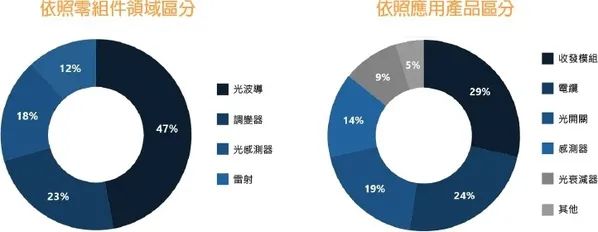

硅光子市場(chǎng)依照零組件領(lǐng)域可區(qū)分為,光波導(dǎo)、調(diào)變器、光感測(cè)器、雷射。其中雷射的部分,預(yù)計(jì)到2035年將成為最大的市場(chǎng)占有硅光子零件,約為35%。而在應(yīng)用產(chǎn)品方面則可區(qū)分為收發(fā)模組、電纜、光開關(guān)、感測(cè)器、光衰減器、其他(圖三)。

圖三: 根據(jù)硅光子市場(chǎng)產(chǎn)品分類的比例統(tǒng)計(jì)。(source:Research Nester;作者整理)

共同封裝光學(xué)的現(xiàn)狀和挑戰(zhàn)

就如上述,由于5G、物聯(lián)網(wǎng)、人工智慧和高效能運(yùn)算應(yīng)用的興起,數(shù)據(jù)中心流量以近30%的復(fù)合年成長(zhǎng)率增長(zhǎng)。此外,近四分之三的數(shù)據(jù)中心流量被保留或暫存在數(shù)據(jù)中心內(nèi),再加上傳統(tǒng)的可插拔光學(xué)元件的成長(zhǎng)速度,比數(shù)據(jù)中心流量的增長(zhǎng)速度慢得許多,因此應(yīng)用需求與傳統(tǒng)可插拔光學(xué)元件的能力之間的差距不斷擴(kuò)大,這種的趨勢(shì)將會(huì)導(dǎo)致

延緩5G、物聯(lián)網(wǎng)、人工智慧和高效能運(yùn)算應(yīng)用等的擴(kuò)大性,所以需要更新的封裝技術(shù)來解決此一問題。

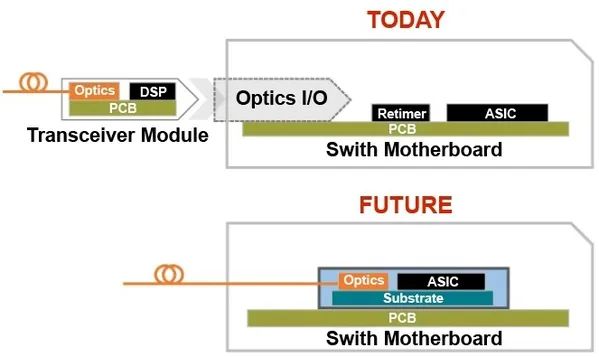

一種顛覆性的封裝技術(shù),共同封裝光學(xué)元件(Co-packaged optics;CPO)就被提出來,透過先進(jìn)的封裝技術(shù),以及電子學(xué)和光子學(xué)的最佳化整合,來大幅縮短電氣鏈路長(zhǎng)度,從而提高互連頻寬密度和能源效率。因此CPO被廣泛認(rèn)為是未來數(shù)據(jù)中心互連的一個(gè)最有效的解決方案。

包括了Intel、Broadcom和IBM等,全球國(guó)際半導(dǎo)體技術(shù)領(lǐng)先業(yè)者,都已經(jīng)投入大量資金對(duì)CPO技術(shù)展開深入研究。這是一個(gè)跨學(xué)科的研究領(lǐng)域,涉及了光子元件、集成電路設(shè)計(jì)、封裝、光子元件建模、電子-光子整合模擬、應(yīng)用和技術(shù)(圖四)。

圖四: 透過CPO技術(shù)將光子元件與ASIC整合到同一基板上。

(source:Broadcom;作者整理)

光子封裝的縮放

在過去數(shù)十年里,摩爾定律不斷的導(dǎo)引著CMOS制造技術(shù)發(fā)展,因此大多數(shù)人也認(rèn)為硅光子學(xué)應(yīng)該遵循這種規(guī)模化趨勢(shì),并致力于透過低成本制造光子集成電路(PIC)來快速達(dá)到規(guī)模經(jīng)濟(jì)。

然而,與電子元件不同,光子元件的縮放本質(zhì)上是困難的。光子元件的尺寸主要由材料的折射率對(duì)比度決定,因此硅光子元件的整體尺寸仍保持在微米級(jí)別,很難縮減到納米級(jí)別。因此,當(dāng)我們談?wù)摴韫庾拥目s放時(shí),實(shí)際上是探討先進(jìn)的制造技術(shù)如何實(shí)現(xiàn)光子封裝的縮放。

封裝概念與制程達(dá)到深度融合

要實(shí)現(xiàn)極高密度的光輸入/輸出,就必須采用高效的光纖耦合結(jié)構(gòu)。耦合結(jié)構(gòu)有光柵耦合器和邊緣耦合器兩種。光柵耦合器通常利用簡(jiǎn)單的兩步驟蝕刻制程生產(chǎn),來實(shí)現(xiàn)垂直光耦合。而光柵耦合器具有相對(duì)較寬的對(duì)準(zhǔn)容差、較小的光學(xué)頻寬和較高的偏振靈敏度。

因此,與邊緣耦合器不同,光柵耦合器通常是用于晶圓級(jí)測(cè)試,而不是商業(yè)性產(chǎn)品。邊緣耦合器可實(shí)現(xiàn)較小的耦合損耗和較大的光學(xué)頻寬,這對(duì)于實(shí)際應(yīng)用來說是理想的。然而,邊緣耦合器在制造過程中需要底切(Undercut)和深蝕刻技術(shù),而這就會(huì)影響著元件穩(wěn)定性和可靠性的問題。

On-chip光源的整合是硅光子學(xué)的主要挑戰(zhàn)之一。只依賴硅基材料很難形成高性能雷射器。因此便開發(fā)出在硅光子芯片上進(jìn)行III-V化合物材料的異質(zhì)材料整合,或異質(zhì)結(jié)構(gòu)整合的技術(shù),但這對(duì)硅光子制造技術(shù)來說,還是需要進(jìn)行重大調(diào)整。

未來,從2.5D CPO到3D CPO,CPO制程將不僅僅是一種封裝技術(shù),而是一種制造與封裝的結(jié)合,需要設(shè)計(jì)與制程的共同最佳化,來讓封裝概念與制程達(dá)到深度融合。

設(shè)法降低光纖封裝難度

在目前大多數(shù)CPO解決方案中,光輸入和光輸出的路徑中都使用了邊緣耦合器。邊緣耦合器經(jīng)過精心設(shè)計(jì),可同時(shí)滿足高對(duì)準(zhǔn)容差和低插入損耗的要求。通過V型槽(V-groove)結(jié)構(gòu)進(jìn)行被動(dòng)式的對(duì)準(zhǔn),典型的光纖到芯片損耗可控制在-1.5 dB。使用熱移相器(Thermal Phase Shifters)等結(jié)構(gòu)更有助于進(jìn)一步提高對(duì)準(zhǔn)容差。由于硅光子收發(fā)器是高速開關(guān)組裝CPO系統(tǒng)的重要構(gòu)件,其中多個(gè)收發(fā)器模組緊鄰開關(guān)ASIC。如圖所示,中心交換機(jī)ASIC周圍有成百上千根光纖,其中既有保持偏極(Polarization-Maintaining;PM)光纖,也有非保持偏極光纖。所以必須透過采用高階調(diào)變技術(shù)和On-chip光源的整合來減少光纖數(shù)量,降低光纖封裝難度。

圖五: 用于光輸入的保持偏極光纖和用于光輸出的非保持偏極光纖的混合封裝。(source:《Co-packaged optics (CPO): status, challenges, and solutions》)

利用異質(zhì)結(jié)構(gòu)整合和異質(zhì)整合

On-chip光源的整合方法包括異質(zhì)結(jié)構(gòu)整合(例如雷射二極體的Flip-Chip Bonding)和異質(zhì)整合(例如,Wafer-Level Material Bonding)。

在Flip-Chip Bonding方法中,將一般雷射二極體透過共晶焊接的方式貼合在硅光子芯片上。雷射芯片和硅光子芯片之間采用Mechanical stops和fiducial marks進(jìn)行高精度非主動(dòng)式對(duì)準(zhǔn)。因?yàn)槔昧顺墒斓睦咨涠O體產(chǎn)品,來簡(jiǎn)化了開發(fā)過程,進(jìn)而實(shí)現(xiàn)了快速商業(yè)化。而在Wafer-Level Material Bonding方法中,雷射器是在硅光子芯片制造過程中所形成的,所以III-V材料和硅波導(dǎo)之間的模式轉(zhuǎn)變器需要對(duì)生產(chǎn)線前端的制程進(jìn)行修改。雷射電極的制造會(huì)導(dǎo)致生產(chǎn)線后端的制程改變。

總之,硅光子生產(chǎn)線需要大規(guī)模重建,來實(shí)現(xiàn)異質(zhì)整合。然而這兩種方法都需要考慮散熱和應(yīng)變所引起的性能下降問題,以便將來能順利應(yīng)用于CPO(圖六)。

圖六: (a) On-chip光源的異質(zhì)結(jié)構(gòu)整合;(b)異質(zhì)材料整合。(source:《Co-packaged optics (CPO): status, challenges, and solutions》)

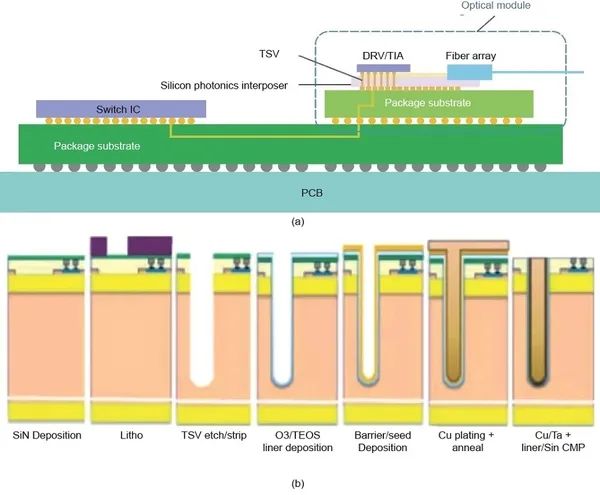

在3D-CPO的結(jié)構(gòu)下,硅光子芯片可作為中介層,實(shí)現(xiàn)更短的電路連接和更低的功耗。最近,imec展示了一種嵌入硅通孔(TSV)結(jié)構(gòu)的混合組裝光學(xué)模組,其射頻的頻寬超過了110 GHz,為下一代需要在100G baud速率運(yùn)作的硅光子模組克服了障礙(圖七)。在硅光子芯片上制造TSV需要額外的制程技術(shù),包括高寬比的Bosch深反應(yīng)性蝕刻,和晶圓薄化制程,這些都可能會(huì)帶來產(chǎn)量和可靠性方面的問題。

圖七: imec發(fā)表一款TSV結(jié)構(gòu)的混合組裝光學(xué)模組:(a)使用具有TSV結(jié)構(gòu)的硅光子插層的混合組裝光模組。(b)硅光子插層上的TSV制程。(source:imec;作者整理)

隨著高整合化趨勢(shì)的發(fā)展,標(biāo)準(zhǔn)硅光子制造技術(shù)必須與封裝的發(fā)展相適應(yīng)。為了滿足CPO的要求,需要開發(fā)先進(jìn)的硅光子制造技術(shù)和元件結(jié)構(gòu)。這對(duì)于CPO應(yīng)用設(shè)計(jì)人員來說,與晶圓代工廠密切合作以實(shí)現(xiàn)設(shè)計(jì)-制程的共同最佳化將更為有效。

硅材料對(duì)于硅光子學(xué)發(fā)展的限制

傳統(tǒng)上,硅光子學(xué)(SiPh)被理解為基于主導(dǎo)常規(guī)電子電路的材料的積集光子學(xué):硅和氧化硅(二氧化硅)。在科學(xué)文獻(xiàn)中,這種類型的集成光子學(xué)通常稱為絕緣體上硅(SOI),該術(shù)語(yǔ)也用于特種半導(dǎo)體技術(shù)。

從嚴(yán)格意義上講,SOI材料可能是3D光子系列中最受限制的技術(shù),該系列還包括基于氮化硅(SiN)和磷化銦(InP)的技術(shù)。由于其間接帶隙,硅無法產(chǎn)生增益或雷射,也就是說該材料不能用于構(gòu)建主動(dòng)組件,例如光源和放大器。SiN也是如此,但這種材料比SOI具有更低的光損耗和更廣泛的光譜覆蓋范圍。

InP是唯一一種無需外部幫助即可執(zhí)行所有功能的半導(dǎo)體,但也具有SOI在損耗和光譜覆蓋范圍方面的缺點(diǎn)。Si和SiN平臺(tái)通常都依賴于與InP的某種形式的整合(如果僅作為光源的話)。做到這一點(diǎn)的最佳方法是針對(duì)特定應(yīng)用。

當(dāng)然,SOI的特性足以滿足許多有趣的應(yīng)用。光可以有效地導(dǎo)入和導(dǎo)出芯片,并且可以使用重要的被動(dòng)組件,例如千兆赫調(diào)變器和光感測(cè)器。除此之外,還能夠利用數(shù)十年的硅制程經(jīng)驗(yàn)(300mm晶圓、高產(chǎn)量、與CMOS共同整合、各種先進(jìn)的3D制程技術(shù)),因此硅光子學(xué)在未來還是有很大的發(fā)展空間。

然而,SiPh越來越多地被解釋為可以在CMOS晶圓廠中制造的任何類型的光子元件。在這種情況下,SiPh和SiN可以變成一個(gè)實(shí)體,因?yàn)楹笳咭部膳cCMOS相容。但有一個(gè)限制,制造光損耗極低的高階SiN波導(dǎo)需要很高的熱預(yù)算,所以這可能與無法與其他功能的形成相容性整合。

而因?yàn)镃MOS制造環(huán)境受到嚴(yán)格控制,某些材料是被禁止的,包括InP和其他III-V族半導(dǎo)體。另一方面,CMOS的定律并不是一成不變的。在過去的幾十年里,晶圓廠導(dǎo)入了幾種新材料來維持摩爾定律的運(yùn)行。所以如果有強(qiáng)有力的商業(yè)策略,這一切皆是有可能的。然而,目前還沒有任何光子學(xué)應(yīng)用能夠產(chǎn)生足以保證主流晶圓廠進(jìn)行此類調(diào)整的數(shù)量。

未來SiPh需要引進(jìn)更多的新材料,來不斷改進(jìn)性能和成本。例如,隨著數(shù)據(jù)中心收發(fā)器的訊號(hào)速率超過200 Gb/s下,實(shí)現(xiàn)足夠的調(diào)變器頻寬和可接受的光損耗,就變得具有挑戰(zhàn)性。這些障礙只能透過在混合物中引入新材料來解決。

此外,急需了解透過在前端處理環(huán)境之外,有哪些無法使用的材料,或包含這些材料的組件,可以在滿足CMOS規(guī)則的同時(shí)引入新材料。但目前,還不清楚什么是最合適的整合,以及何時(shí)可以大規(guī)模展開。除了數(shù)據(jù)和電信之外,應(yīng)用研究仍處于起步階段。不過隨著SiPh所彰顯出的吸引力、商業(yè)策略的鞏固和市場(chǎng)拉力的增加,或許材料極限將被證明并不像以前想像的那么困難。

來源:半導(dǎo)體芯聞

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19170瀏覽量

229179 -

CMOS

+關(guān)注

關(guān)注

58文章

5687瀏覽量

235157 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27043瀏覽量

216419 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7428瀏覽量

87727 -

硅光芯片

+關(guān)注

關(guān)注

5文章

46瀏覽量

6004

原文標(biāo)題:潛力無限的硅光芯片

文章出處:【微信號(hào):芯長(zhǎng)征科技,微信公眾號(hào):芯長(zhǎng)征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

云服務(wù)和5G需求帶動(dòng)硅光子成長(zhǎng)

云服務(wù)和5G需求帶動(dòng)硅光子成長(zhǎng)

評(píng)論