用D觸發(fā)器設(shè)計(jì)一個(gè)序列發(fā)生器 怎么用D觸發(fā)器做序列信號(hào)發(fā)生器?

序列發(fā)生器是數(shù)字電子技術(shù)中常用的電路模塊之一,它可以用來生成一系列的數(shù)字信號(hào)序列。在數(shù)字電路中,D觸發(fā)器是一種被廣泛使用的數(shù)字邏輯組件,在很多應(yīng)用場景中都可以用來構(gòu)建序列發(fā)生器。本文將介紹使用D觸發(fā)器設(shè)計(jì)序列發(fā)生器的方法和步驟。

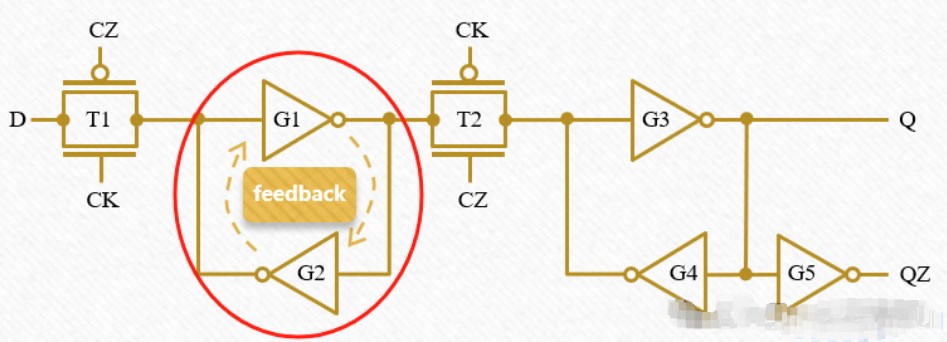

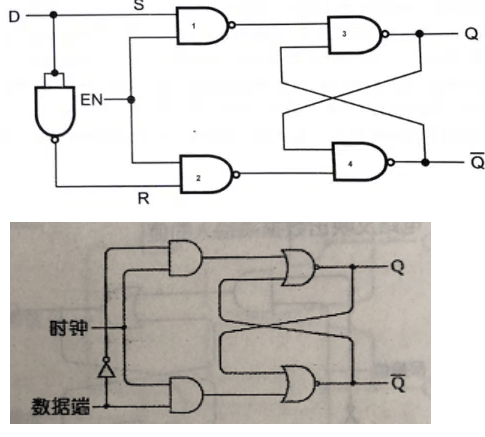

首先,我們需要了解D觸發(fā)器的基本原理和性質(zhì)。D觸發(fā)器是一種時(shí)序電路,它可以存儲(chǔ)和延遲一個(gè)輸入信號(hào),并在時(shí)鐘信號(hào)到來時(shí)輸出這個(gè)輸入信號(hào)的狀態(tài)。

其中,D表示輸入端輸入的電平,Q表示輸出端輸出的電平,CLK表示時(shí)鐘信號(hào)。當(dāng)時(shí)鐘信號(hào)從低電平變?yōu)楦唠娖剑ㄉ仙兀r(shí),D觸發(fā)器將輸入端的值D存儲(chǔ)到內(nèi)部,同時(shí)輸出端的值Q也隨之變化。當(dāng)時(shí)鐘信號(hào)從高電平變?yōu)榈碗娖剑ㄏ陆笛兀r(shí),D觸發(fā)器不受外界信號(hào)的影響,內(nèi)部的狀態(tài)保持不變。

使用D觸發(fā)器可以構(gòu)建一個(gè)簡單的二進(jìn)制序列發(fā)生器。假設(shè)我們要生成一個(gè)從0到7的8位二進(jìn)制循環(huán)序列,我們可以按照以下步驟進(jìn)行設(shè)計(jì)。

1. 首先,需要定義一個(gè)8位計(jì)數(shù)器,用來計(jì)數(shù)并產(chǎn)生序列。

2. 通過D觸發(fā)器和與門,建立時(shí)序電路,實(shí)現(xiàn)時(shí)序控制。

3. 將輸出端的二進(jìn)制信號(hào)接入到各個(gè)D觸發(fā)器的D端。

4. 通過時(shí)鐘信號(hào),不斷切換D觸發(fā)器的狀態(tài),使得每個(gè)時(shí)鐘周期都能夠產(chǎn)生一個(gè)新的二進(jìn)制數(shù)。

5. 最后將輸出端的信號(hào)進(jìn)行顯示或接入其他模塊進(jìn)行進(jìn)一步處理。

在此基礎(chǔ)上,我們可以進(jìn)一步設(shè)計(jì)出更加復(fù)雜的序列發(fā)生器。例如,可以通過串聯(lián)多個(gè)D觸發(fā)器,構(gòu)建更高位數(shù)的二進(jìn)制序列;還可以使用多路選擇器和計(jì)時(shí)器,實(shí)現(xiàn)隨機(jī)序列或者周期變化的序列。

總之,D觸發(fā)器是構(gòu)建數(shù)字序列發(fā)生器的重要組件之一,掌握使用D觸發(fā)器設(shè)計(jì)序列發(fā)生器的方法和技巧,對(duì)于數(shù)字電子技術(shù)的學(xué)習(xí)和應(yīng)用都有很大幫助。

序列發(fā)生器是數(shù)字電子技術(shù)中常用的電路模塊之一,它可以用來生成一系列的數(shù)字信號(hào)序列。在數(shù)字電路中,D觸發(fā)器是一種被廣泛使用的數(shù)字邏輯組件,在很多應(yīng)用場景中都可以用來構(gòu)建序列發(fā)生器。本文將介紹使用D觸發(fā)器設(shè)計(jì)序列發(fā)生器的方法和步驟。

首先,我們需要了解D觸發(fā)器的基本原理和性質(zhì)。D觸發(fā)器是一種時(shí)序電路,它可以存儲(chǔ)和延遲一個(gè)輸入信號(hào),并在時(shí)鐘信號(hào)到來時(shí)輸出這個(gè)輸入信號(hào)的狀態(tài)。

其中,D表示輸入端輸入的電平,Q表示輸出端輸出的電平,CLK表示時(shí)鐘信號(hào)。當(dāng)時(shí)鐘信號(hào)從低電平變?yōu)楦唠娖剑ㄉ仙兀r(shí),D觸發(fā)器將輸入端的值D存儲(chǔ)到內(nèi)部,同時(shí)輸出端的值Q也隨之變化。當(dāng)時(shí)鐘信號(hào)從高電平變?yōu)榈碗娖剑ㄏ陆笛兀r(shí),D觸發(fā)器不受外界信號(hào)的影響,內(nèi)部的狀態(tài)保持不變。

使用D觸發(fā)器可以構(gòu)建一個(gè)簡單的二進(jìn)制序列發(fā)生器。假設(shè)我們要生成一個(gè)從0到7的8位二進(jìn)制循環(huán)序列,我們可以按照以下步驟進(jìn)行設(shè)計(jì)。

1. 首先,需要定義一個(gè)8位計(jì)數(shù)器,用來計(jì)數(shù)并產(chǎn)生序列。

2. 通過D觸發(fā)器和與門,建立時(shí)序電路,實(shí)現(xiàn)時(shí)序控制。

3. 將輸出端的二進(jìn)制信號(hào)接入到各個(gè)D觸發(fā)器的D端。

4. 通過時(shí)鐘信號(hào),不斷切換D觸發(fā)器的狀態(tài),使得每個(gè)時(shí)鐘周期都能夠產(chǎn)生一個(gè)新的二進(jìn)制數(shù)。

5. 最后將輸出端的信號(hào)進(jìn)行顯示或接入其他模塊進(jìn)行進(jìn)一步處理。

在此基礎(chǔ)上,我們可以進(jìn)一步設(shè)計(jì)出更加復(fù)雜的序列發(fā)生器。例如,可以通過串聯(lián)多個(gè)D觸發(fā)器,構(gòu)建更高位數(shù)的二進(jìn)制序列;還可以使用多路選擇器和計(jì)時(shí)器,實(shí)現(xiàn)隨機(jī)序列或者周期變化的序列。

總之,D觸發(fā)器是構(gòu)建數(shù)字序列發(fā)生器的重要組件之一,掌握使用D觸發(fā)器設(shè)計(jì)序列發(fā)生器的方法和技巧,對(duì)于數(shù)字電子技術(shù)的學(xué)習(xí)和應(yīng)用都有很大幫助。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

發(fā)生器

+關(guān)注

關(guān)注

4文章

1362瀏覽量

61621 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2253瀏覽量

94351 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

47862 -

信號(hào)發(fā)生器

+關(guān)注

關(guān)注

28文章

1452瀏覽量

108652 -

數(shù)字序列發(fā)生器

+關(guān)注

關(guān)注

0文章

3瀏覽量

5802

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

怎么用jk觸發(fā)器變成t觸發(fā)器

JK觸發(fā)器 :具有四種基本的邏輯功能,分別是保持、復(fù)位、設(shè)置和反轉(zhuǎn)。這些功能由J和K兩個(gè)輸入端口的信號(hào)共同決定。 T觸發(fā)器 :具有單一的輸

d與rs觸發(fā)器間功能的轉(zhuǎn)換

與RS觸發(fā)器的基本概念 D觸發(fā)器 D觸發(fā)器是一種具有數(shù)據(jù)輸入(

d觸發(fā)器和d鎖存器的區(qū)別是什么

。D觸發(fā)器有兩個(gè)輸入端,一個(gè)是數(shù)據(jù)輸入端D,另一個(gè)是時(shí)鐘輸入端CLK;兩

d觸發(fā)器和jk觸發(fā)器的區(qū)別是什么

,可以存儲(chǔ)一位二進(jìn)制信息。觸發(fā)器的輸出狀態(tài)取決于輸入信號(hào)和觸發(fā)器的當(dāng)前狀態(tài)。觸發(fā)器的分類主要有D

t觸發(fā)器變?yōu)?b class='flag-5'>d觸發(fā)器的條件

在數(shù)字電路設(shè)計(jì)中,觸發(fā)器是一種非常重要的存儲(chǔ)元件,用于存儲(chǔ)一位二進(jìn)制信息。觸發(fā)器的種類很多,其中最為常見的有JK觸發(fā)器、

d觸發(fā)器是電平觸發(fā)還是邊沿觸發(fā)

電平觸發(fā)D觸發(fā)器的特點(diǎn) 電平觸發(fā)D觸發(fā)器是一種在輸

t觸發(fā)器與d觸發(fā)器的區(qū)別和聯(lián)系

)。 1. 觸發(fā)器的基本概念 觸發(fā)器是一種具有記憶功能的電路,它可以存儲(chǔ)一位二進(jìn)制信息。在數(shù)字電路中,觸發(fā)器通常由兩

主從觸發(fā)器都是下降沿觸發(fā)嗎

沿觸發(fā),也可以是下降沿觸發(fā),具體取決于設(shè)計(jì)和應(yīng)用需求。 主從觸發(fā)器的原理 主從觸發(fā)器由兩個(gè)觸發(fā)器

基于D觸發(fā)器的音頻信號(hào)發(fā)生器電路圖 D觸發(fā)器的工作原理和脈沖特性

D觸發(fā)器(Data Flip-Flop或Delay Flip-Flop)是數(shù)字電子電路中一種重要的存儲(chǔ)器件,主要用于存儲(chǔ)1位二進(jìn)制數(shù)據(jù)。它具有記憶功能,能夠在特定的時(shí)鐘脈沖作用下,將輸入端的信

數(shù)字序列信號(hào)發(fā)生器如何測量

數(shù)字序列信號(hào)發(fā)生器(Digital Sequence Signal Generator,簡稱DSSG)是一種用于生成數(shù)字序列

d觸發(fā)器的功能 d觸發(fā)器的狀態(tài)方程

。D觸發(fā)器是一種雙穩(wěn)態(tài)邏輯器件,它可以在時(shí)鐘信號(hào)的作用下將輸入數(shù)據(jù)存儲(chǔ),并在時(shí)鐘上升沿或下降沿時(shí)將存儲(chǔ)的數(shù)據(jù)傳遞到輸出端。 D

如何用jk觸發(fā)器構(gòu)成t觸發(fā)器?t觸發(fā)器邏輯功能有哪些

如何用JK觸發(fā)器構(gòu)成T觸發(fā)器 JK觸發(fā)器是一種基本的觸發(fā)器電路,由兩個(gè)輸入端J和K控制,以及兩

d觸發(fā)器的邏輯功能 d觸發(fā)器sd和rd作用

了解一下D觸發(fā)器的邏輯功能。D觸發(fā)器是一種存儲(chǔ)設(shè)備,它可以存儲(chǔ)和傳輸

d觸發(fā)器有幾個(gè)穩(wěn)態(tài) d觸發(fā)器和rs觸發(fā)器的區(qū)別

的區(qū)別 輸入方式不同: D觸發(fā)器只有一個(gè)輸入端D,用來接收輸入信號(hào); RS

d觸發(fā)器有記憶功能嗎 D觸發(fā)器的基本原理

D觸發(fā)器(D flip-flop)可以存儲(chǔ)一位二進(jìn)制數(shù)據(jù)的狀態(tài),因此具有記憶功能。D觸發(fā)器通常用

用D觸發(fā)器設(shè)計(jì)一個(gè)序列發(fā)生器 怎么用D觸發(fā)器做序列信號(hào)發(fā)生器?

用D觸發(fā)器設(shè)計(jì)一個(gè)序列發(fā)生器 怎么用D觸發(fā)器做序列信號(hào)發(fā)生器?

評(píng)論