pcb連線寄生電容一般多少

隨著電子產品制造技術的成熟和發展,隨之而來的是布線技術的迅速發展。不同的 PCB 布線技術對于電路性能的影響不同,而其中最常見的問題之一就是 PCB 連線寄生電容。這種電容可能會對電路的性能和穩定性產生影響。因此,在 PCB 布線設計中,充分了解寄生電容的產生原因和處理方法是非常必要的。

什么是 PCB 連線寄生電容

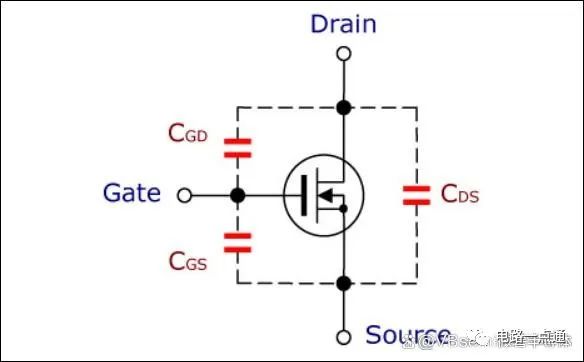

維基百科上對于 PCB 連線寄生電容的定義是“由于 PCB 上信號線之間的相互耦合而導致的電容效應”。簡而言之,就是在 PCB 上布線過程的中,由于導線之間的相互影響和距離的縮短,導致電容的產生。

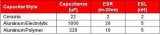

為了更好地理解 PCB 連線寄生電容,可以將其與常見的電容器進行對比。電容器由兩個金屬板分離,中間隔著一種絕緣材料,形成一定的電容值。而 PCB 連線寄生電容指的是 PCB 上不同的導體之間存在一定的電容值,這是由于不同導體上的電荷分布情況通電后的作用,經過布線處理后形成的。

兩個相鄰的導線,假設兩條導線之間的距離很近,在通電后存在電場一定會壓縮介質厚度,產生電容效應。這種情況是無法避免的,但可以通過一定的處理方法,減少電容的產生。

寄生電容的產生原因

PCB 連線寄生電容產生的原因是信號線之間的相互影響和距離的縮短,它產生的原因可以歸納為以下幾個方面:

1. 兩條不同的 PCB 線路之間的距離較小時,兩條線路之間的電場會產生交叉,在高頻帶下更為明顯。

2. 當兩條導線同時通電時,它們之間的電場會互相影響。

3. PCB 上導線材料的選擇也可能會影響產生的電容值。

4. 寄生電容的值還受到某些布線方法的影響,例如 “直角彎曲” 或使用“VCCA” 接地等。

如何降低 PCB 連線寄生電容的影響

為了降低 PCB 連線寄生電容的影響,我們可以通過以下幾種方法:

1. 增加信號線之間的間距

增加信號線之間的間距是減少 PCB 連線寄生電容的常見方法之一。當兩個線路之間的間距增加時,線路之間的電場會減弱,從而降低線路之間的電容值。

2. 減少 PCB 平面上的走線

減少 PCB 平面上的走線是減少 PCB 連接寄生電容的常見方法。當走線數量減少時,其它線路之間的受影響的細節會更小,從而使寄生電容值變小。

3. 使用地平面和屏蔽

使用地平面和屏蔽也是減少 PCB 連線寄生電容的有效方法。如果在 PCB 的外圍區域設置一個地平面和一個屏蔽罩,可以阻止電場相互影響,從而減少電容的產生。

4. 創造一個對稱布局

創造對稱布局是減少 PCB 連線寄生電容的潛在方法之一。在 PCB 布局設計中,盡可能保持對稱布局,可以減少線路之間的影響和相互作用。當線路布局對稱時,線路之間的交叉和電荷積聚將變得更為平衡,從而減少電容的產生。

總體而言,降低 PCB 連線寄生電容對于電路性能和輸出有著非常關鍵的意義。通過合適的 PCB 布線技術和設計方法,可以減少 PCB 連線寄生電容的影響,優化電路的穩定性和可靠性,并提高產品在市場上的競爭力。

-

電容器

+關注

關注

63文章

6199瀏覽量

99306 -

pcb

+關注

關注

4317文章

23002瀏覽量

396236 -

寄生電容

+關注

關注

1文章

291瀏覽量

19192

發布評論請先 登錄

相關推薦

半大馬士革工藝:利用空氣隙減少寄生電容

深入解析晶振時鐘信號干擾源:寄生電容、雜散電容與分布電容

退耦電容一般用多大

仿真的時候在哪些地方添加寄生電容呢?

在LF411CD的放大模塊出現輸出會發生振蕩,請問該元件輸入端(2端)與GND間的寄生電容多大?

普通探頭和差分探頭寄生電容對測試波形的影響

igbt功率管寄生電容怎么測量大小

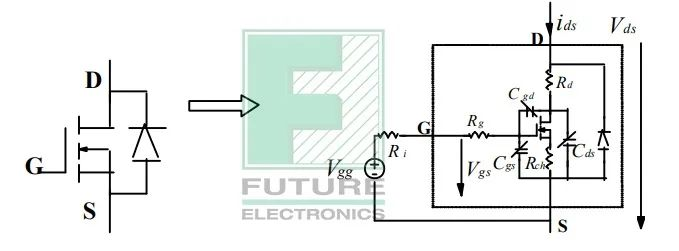

IGBT柵極下拉電阻和穩壓二極管的作用?

你知道嗎?晶振為何不宜置于PCB邊緣?

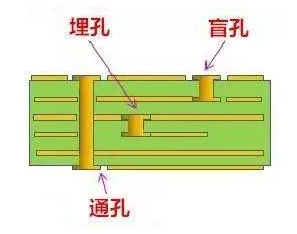

PCB生產中的過孔和背鉆有些什么樣的技術?

pcb連線寄生電容一般多少

pcb連線寄生電容一般多少

評論