1 LVPECL與LVPECL之間的連接

LVPECL 到LVPECL 的連接分直流耦合和交流耦合兩種形式

1.1 直流耦合

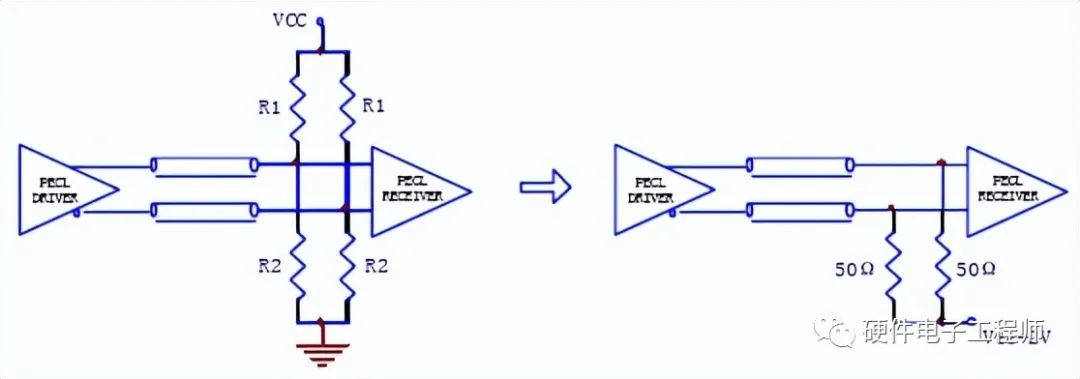

LVPECL 負載一般考慮是通過50Ω接到Vcc-2V 的電源上,一般該電源是不存在的,通常的做法是利用電阻分壓網絡做等效電路,如圖3.1 中所示,該等效電路應滿足如下方程:

圖3.1 等效電路

Vcc ? 2 V = Vcc R2/(R1+R2)

R1*R2/(R1 + R2)=50Ω

解上面方程組,得到:

R1 = 50VCC/(VCC-2V) R2 = 25VCC

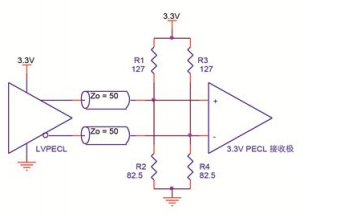

圖3.2 給出了這兩種供電情況時的詳細電路。

圖3.2 PECL電路之間直流耦合

在3.3V 供電時,電阻按5%的精度選取,R1為130Ω,R2為82Ω;在5V 供電時(此時為PECL電平),R1為82Ω,R2為130Ω。

1.2 交流耦合

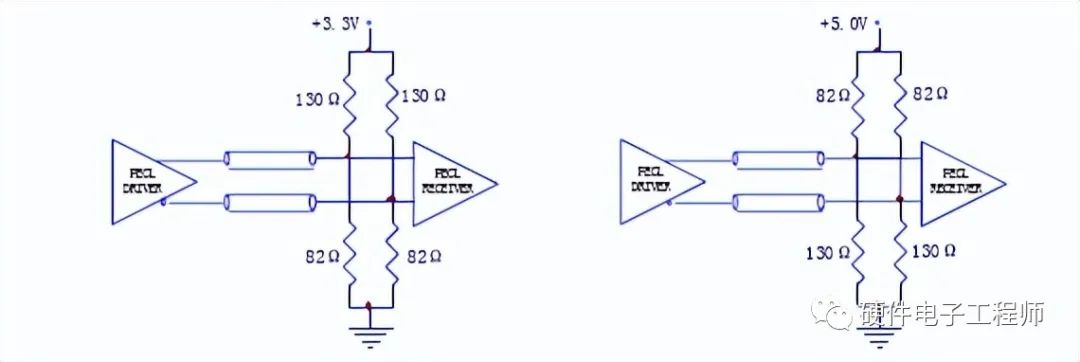

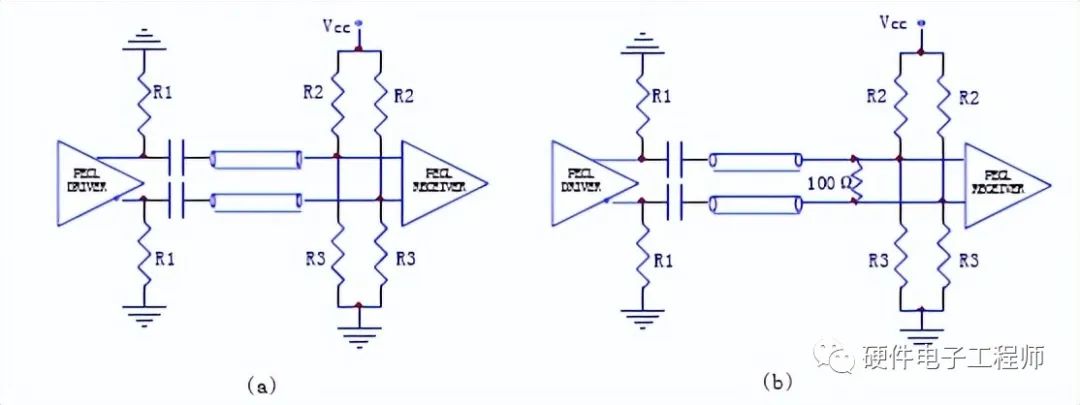

PECL 的輸出共模電壓需固定在Vcc-1.3V,在選擇直流偏置電阻時僅需該電阻能夠提供

14mA 到地的通路,這樣R1=(Vcc-1.3V)/14mA。在3.3V 供電時,R1=142Ω,5V 供電時,R1=270Ω。然而這種方式給出的交流負載阻抗低于50Ω,在實際應用中,3.3V 供電時,R1 可以從142Ω到200Ω之間選取,5V 供電時,R1 可以從270Ω到350Ω之間選取,原則是讓輸出波形達到最佳。

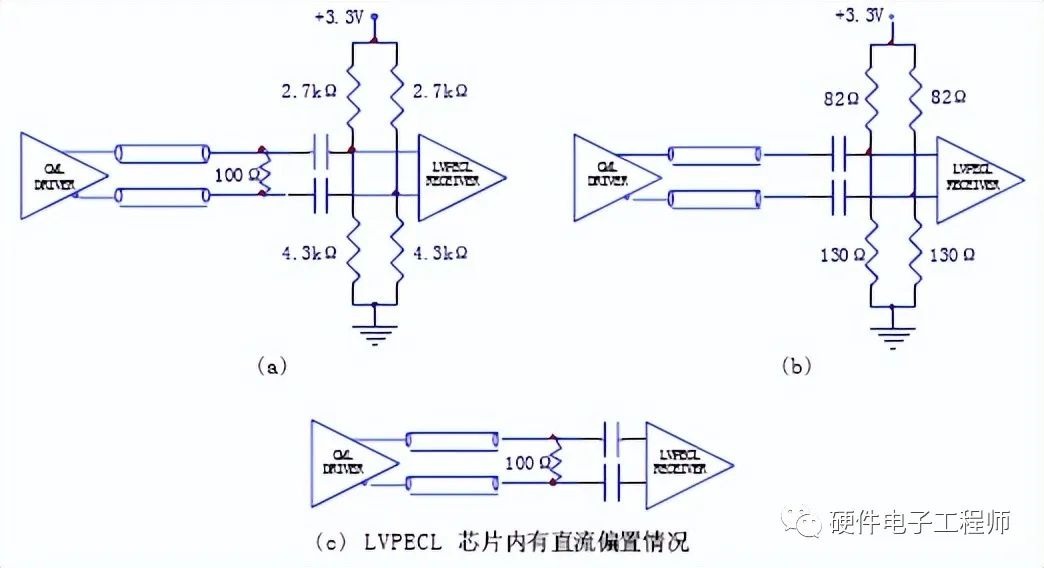

圖3.3中分別給出了兩種電路結構,在圖3.3 (a)有一個缺點就是它的功耗較大,當對功耗有要求時,可以采用圖3.3(b)所示電路結構。

圖3.3 PECL電路間交流耦合

在圖3.3 (a)中,R2和R3通常選取:

R2 = 82 ? / R3 = 130 ? +3.3 V供電時

R2 = 68 ? / R3 = 180 ? +5 V供電時

在圖3.3 (b)中,R2和R3通常選取:

R2 = 2.7 K? / R3 = 4.3 K? +3.3 V供電時

R2 = 2.7 K? / R3 = 7.8 K? +5 V供電時

2 LVDS與LVDS接口的連接

LVDS 用于低壓差分信號點到點的傳輸,該方式有三大優點,從而使得它更具有吸引力:

(1)LVDS 傳輸的信號擺幅小,從而功耗低,一般差分線上電流不超過4mA,負載阻抗為100Ω。這一特征使它適合做并行數據傳輸。

(2)LVDS 信號擺幅小,從而使得該結構可以在2.4V 的低電壓下工作。

(3)LVDS 輸入單端信號電壓可以從0V 到2.4V 變化,單端信號擺幅為400mV,這樣允許輸入共模電壓從0.2V 到2.2V范圍內變化,也就是說LVDS 允許收發兩端地電勢有±1V的落差。

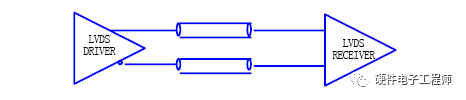

圖3.4 LVDS間連接

因為LVDS 的輸入與輸出都是內匹配的,所以LVDS 間的連接可以如圖3.4那樣直接連接。但在設計時需要確認芯片內部,其接收端差分線對間是否已有100Ω電阻匹配,若沒有則需在外面加100Ω電阻,電阻需靠近接收端放置。

3 CML電平之間的連接

CML 是所有高速數據接口形式中最簡單的一種,它的輸入與輸出是匹配好的,從而減少了外圍器件,也更適合于在高的頻段工作。它所提供的信號擺幅較小,從而功耗更低。

CML 接口的輸出電路形式是一個差分對,該差分對的集電極電阻為50Ω。假定CML 輸出負載為一50Ω上拉電阻,則單端CML 輸出信號的擺幅為Vcc~Vcc-0.4V。在這種情況下,差分輸出信號擺幅為800mV,共模電壓為Vcc-0.2V。若CML輸出采用交流耦合至50Ω負載,這時的直流阻抗有集電極電阻決定,為50Ω,CML 輸出共模電壓變為Vcc-0.4V,差分信號擺幅仍為800mV。

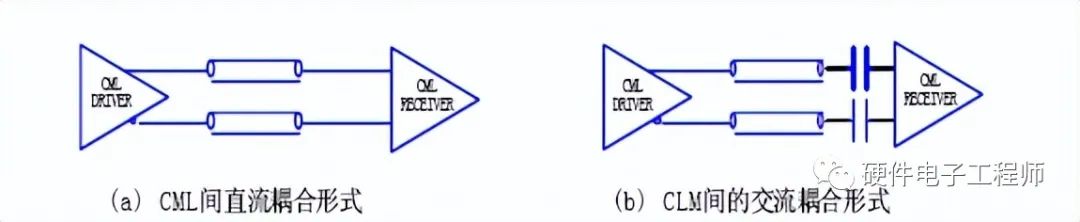

CML 到CML 之間連接分兩種情況:

(1)當收發兩端的器件使用相同的電源時,CML 到CML 可以采用直流耦合方式,這時不需加任何器件;

(2)當收發兩端器件采用不同電源時,一般要考慮交流耦合,如圖3.5 中所示,注意這時選用的耦合電容要足夠大,以避免在較長連0 或連1 情況出現時,接收端差分電壓變小。

圖3.5 CML接口間連接

4 LVPECL到CML的連接

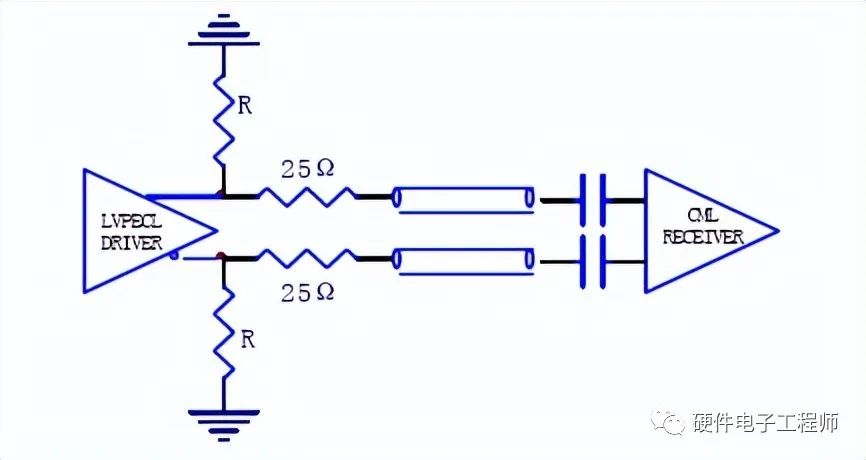

4.1 交流耦合

LVDS到CML的交流耦合連接方式如圖3.6 所示。在LVPECL的兩個輸出端各加一個到地的偏置電阻,電阻值選取范圍可以從142Ω到200Ω。如果LVPECL 的輸出信號擺幅大于CML 的接收范圍,可以在信號通道上串一個25Ω的電阻,這時CML 輸入端的電壓擺幅變為原來的0.67 倍。

圖3.6 LVPECL到CML的交流耦合連接

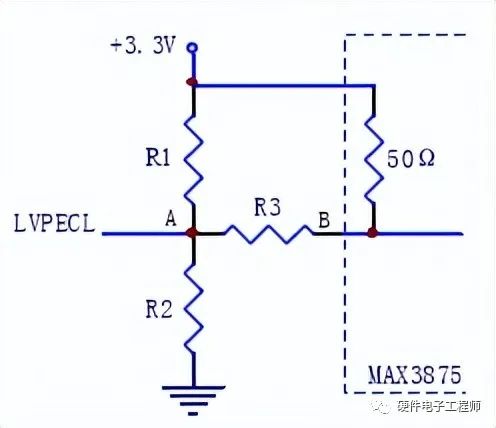

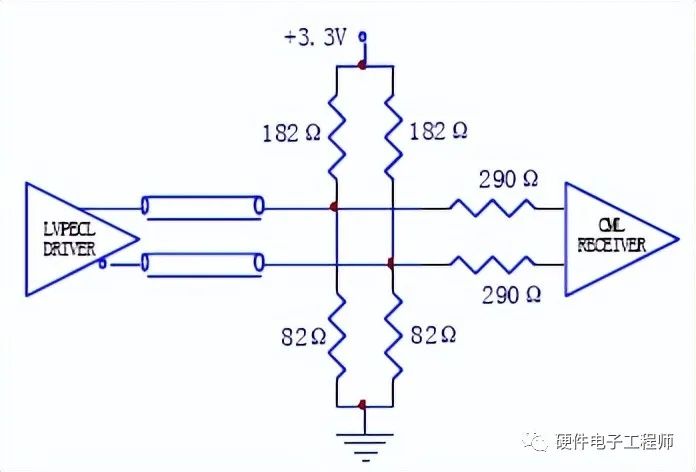

4.2 直流耦合

在LVPECL 到CML 的直流耦合連接方式中需要一個電平轉換網絡,如圖3.7(a)中所示。該電平轉換網絡的作用是匹配LVPECL 的輸出與CML的輸入共模電壓。一般要求該電平轉換網絡引入的損耗要小,以保證LVPECL 的輸出經過衰減后仍能滿足CML 輸入靈敏度的要求;另外還要求自LVPECL端看到的負載阻抗近似為50Ω。下面以LVPECL驅動MAX3875 的

(a)直流耦合時電阻網絡

(b)直流耦合連接

圖3.7 LVPECL到CML的直流耦合連接

CML 輸入為例說明該電平轉換網絡。如前所述,電阻網絡需滿足:

VA = VCC - 2.0V = R2·VCC /(R2 + R1//(R3 + 50Ω))

VB = VCC - 0.2V = (VCC·R3 + 50Ω·(VCC - 1.3V))/(R3 + 50Ω)

Zin = R1// R2 // (R3 + 50 ?)= 50 ?

Gain = 50 /(R3 + 50) ≥ 0.125

求解上面的方程組,我們得到R1=182Ω,R2=82Ω,R3=290Ω,VA=1.35V,VB=3.11V,Gain=0.147,Zin=49Ω。

LVPECL 到MAX3875 的直流耦合結構如圖3.7(b) 所示。對于其它產品的CML 輸入,最小共模電壓和靈敏度可能不同,設計時可修改VB值,再根據上面的公式計算所需的阻值。

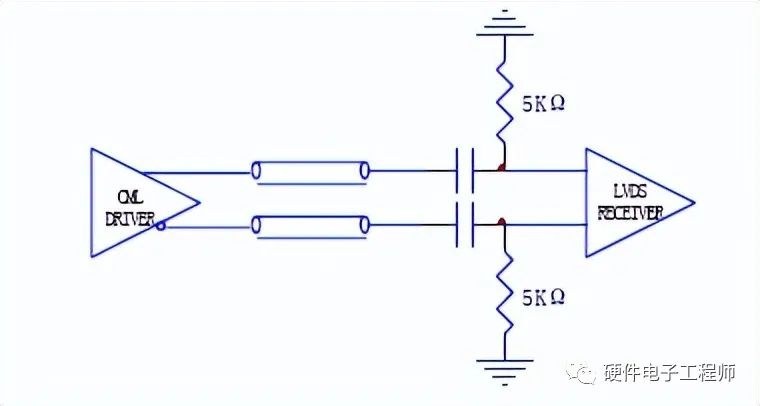

5 CML到LVPECL的連接

圖3.8中,給出了CML到LVPECL的交流耦合連接。由于CML與LVPECL接口的中心電平不同,

圖3.8 CML到LVPECL的交流耦合連接

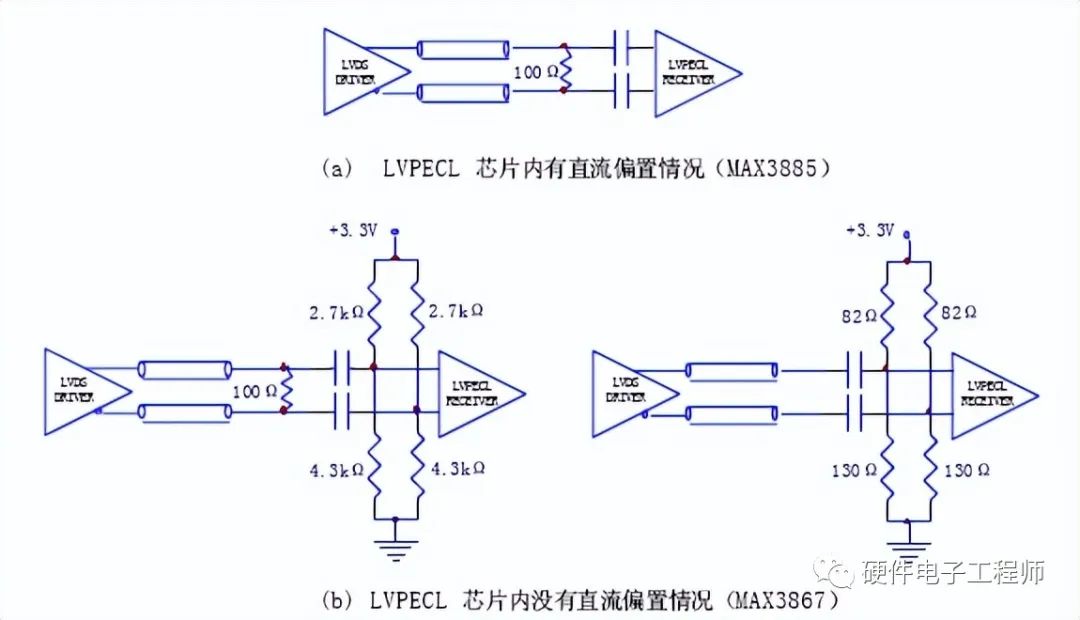

通常采用交流耦合,LVPECL輸入接口需要外加直流偏置,保證中心電平在VCC-1.3V,圖8(a)、(b)分別是外部加直流偏置電阻的連接方式。其中,(a)的連接方式功耗較低。(c)為芯片內已有直流偏置時的連接電路。

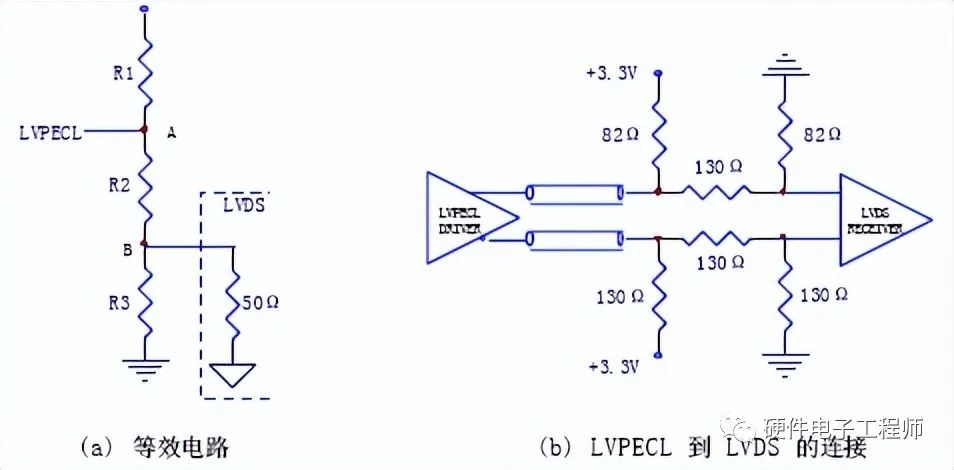

6 LVPECL到LVDS的連接

6.1 直流耦合

LVPECL到LVDS 的直流耦合結構需要一個電阻網絡,如圖3.9中所示,設計該網絡時有這樣幾點必須考慮:首先,我們知道當負載是50Ω接到Vcc-2V 時,LVPECL 的輸出性能是最優的,因此我們考慮該電阻網絡應該與最優負載等效;然后我們還要考慮該電阻網絡引入的衰減不應太大,LVPECL 輸出信號經衰減后仍能落在LVDS 的有效輸入范圍內。

注意LVDS 的輸入差分阻抗為100Ω,或者每個單端到虛擬地為50Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等.經計算,電阻值為:R1=182Ω,R2=48Ω,R3=48Ω。電阻靠近接收側放置。

圖3.9 LVPECL到LVDS的直流耦合結構

6.2 交流耦合

LVPECL 到LVDS 的交流耦合結構如圖3.10 所示,LVPECL 的輸出端到地需加直流偏置電阻(142Ω到200Ω),同時信號通道上一定要串接50Ω電阻,以提供一定衰減。LVDS 的輸入端到地需加5KΩ電阻,以提供近似0.86V 的共模電壓。

圖3.10 LVPECL到LVDS的交流耦合結構

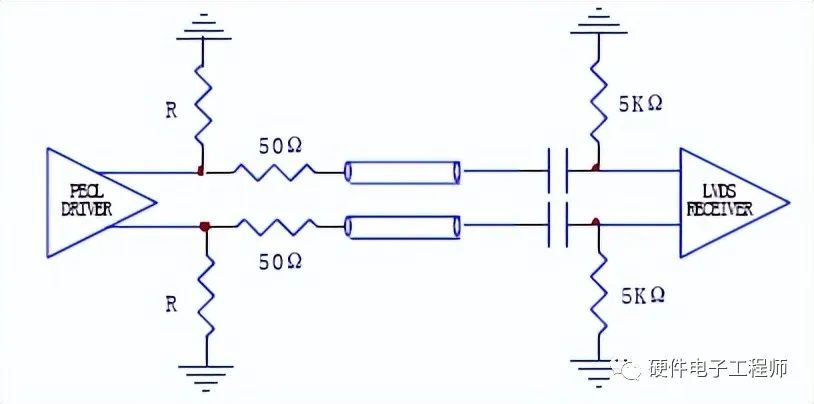

7 LVDS到LVPECL的連接

7.1 直流耦合

LVDS到LVPECL 的直流耦合結構中需要加一個電阻網絡,如圖3.11 所示,該電阻網絡完成直流電平的轉換。LVDS輸出電平為1.2V,LVPECL的輸入電平為Vcc-1.3V。LVDS 的輸出是以地為基準,而LVPECL 的輸入是以電源為基準,這要求考慮電阻網絡時應注意LVDS 的輸出電位不應對供電電源敏感;

另一個問題是需要在功耗和速度方面折中考慮,如果電阻值取的較小,可以允許電路在更高的速度下工作,但功耗較大,LVDS 的輸出性能容易受電源的波動影響;

還有一個問題就是要考慮電阻網絡與傳輸線的匹配。經計算,電阻值選取為:R1=374Ω,R2=249Ω,R3=402Ω,VA=1.2V,VB=2.0V,RIN=49Ω,Gain=0.62。LVDS 的最小差分輸出信號擺幅為500mV,在上面結構中加到LVPECL 輸入端的信號擺幅變為310mV,該幅度低于LVPECL 的輸入標準,但對于絕大多數MAXIM 公司的LVPECL 電路來說,該信號幅度是足夠的。設計中可根據器件的實際性能作出自己的判斷。

圖3.11 LVDS到LVPECL的直流耦合結構

7.2 交流耦合

LVDS 到LVPECL 的交流耦合結構較為簡單,只需要LVPECL輸入側加直流偏置,滿足其中心電壓的要求。圖3.12 (a)、(b)兩種為常用到的結構。

圖 3.12 LVDS到LVPECL的交流耦合結構

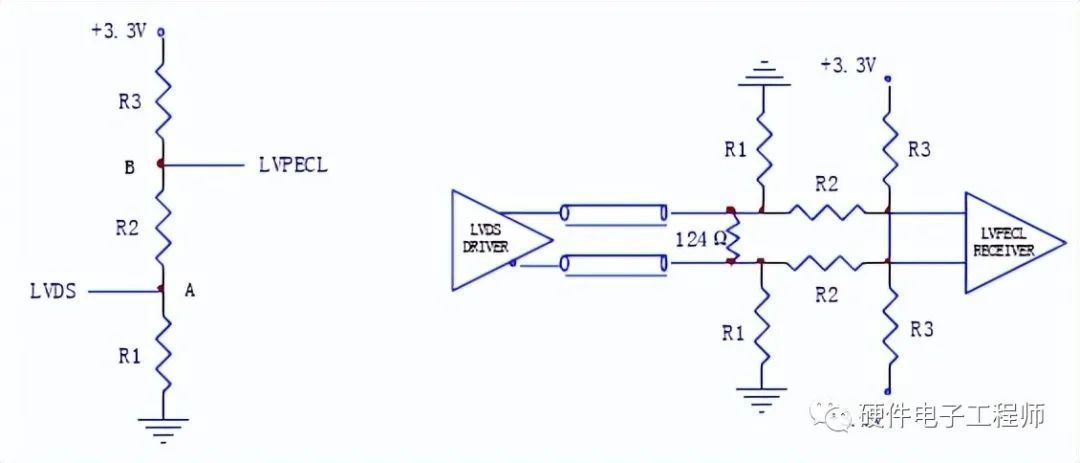

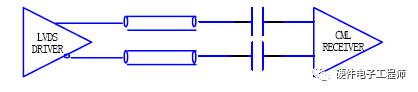

8 CML到LVDS的連接

CML到LVDS的連接通常采用交流耦合結構,圖3.13、14給出了兩種電路結構,需注意CML 的輸出信號擺幅應落在LVDS 的有效工作范圍內。

圖3.13 CML到LVDS的交流耦合結構

圖3.14 CML到LVDS的交流耦合結構

9 差分信號設計原則

在差分信號傳輸設計中,不同類型的差分線,其輸入輸出的中心電平不同,擺幅也不同。但設計中,以下設計原則還是比較通用的。

(1)差分線的正、負端要求等長。一般來說,對于155Mbps的差分線對,其長度差應控制在160mil以內,建議控制在80mil以內;622Mbps的差分線對,控制在40mil以內;其余按速率類推,或根據datasheet推薦的值進行約束。

(2)差分阻抗控制在100 +/-10%Ω。

(3)數據差分線與其它非時鐘信號線的邊到邊間距應大于2倍線寬,與時鐘信號線或時鐘差分線應大于3倍線寬。

(4)一般來說,差分線在布線時盡量走內層,且要鄰近平面層,表層走線盡量短;

(5)對于高速差分線為減少過孔數目,有時也允許走表層。差分線的過孔數目越少越好,在需要打過孔的情況下,差分線正、負信號線要成對打過孔,也即若正端信號線需要打過孔換層,負端信號線也需要在相應的位置打過孔。一般來說,155Mbps速率的差分線對,其過孔應數目控制在4個以內,622MGbps及1.25Gbps速率的應控制在3個以內;而2.5Gbps速率及以上的差分對,除在BGA下出線必須打過孔以及壓接式接插件必須的壓接過孔外,在其信號走線的其它位置盡量不要再打過孔。

(6)時鐘信號在不同電平間轉換時,盡量采用交流耦合結構。交流耦合電容,選取不宜太小,通常1GHz以上頻率選0.01μF,以下的選取0.1μF。瀉放電阻和匹配電阻在PCB中的布局和選擇。對于有泄放電阻或終端匹配電阻的差分接口電路,泄放電阻R1應盡量放在驅動pin附近,匹配電阻R2和R3盡量靠近接收pin;

(7)考慮到散熱和能承受的額定功率,最好選擇選擇0603封裝的電阻,或者0805封裝的電阻,不應選用0402及更小封裝的電阻,否則應具體計算該電阻上的功耗。

審核編輯:劉清

-

PCB板

+關注

關注

27文章

1442瀏覽量

51508 -

電阻器

+關注

關注

21文章

3760瀏覽量

62040 -

電平轉換器

+關注

關注

1文章

173瀏覽量

19547 -

LVPECL

+關注

關注

2文章

27瀏覽量

17917 -

交流耦合

+關注

關注

0文章

32瀏覽量

12158

原文標題:PECL/CML/LVDS高速接口互連電路設計

文章出處:【微信號:電子設計聯盟,微信公眾號:電子設計聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互轉換過程介紹

LVPECL、VML、CML、LVDS 與LVDS之間的接口連接轉換

LVPECL驅動器終端設計介紹

如何將Virtex 5 LVPECL_25連接到另一個設備的3.3v lvpecl?

如何在LVPECL、VML、CML、LVDS和子LVDS接口之間轉換

如果ad9680的clk和sysref信號采用lvpecl格式輸入,交流耦合的話前端網絡如何設計?

SN65LVCP23,pdf(2x2 LVPECL Cros

設計LVPECL終端需要考慮那些原因

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

獲得連接:LVPECL、VML、CML、LVDS 與子 LVDS 之間的接口連接

SN65CML100D 1.5 Gbps LVDS/LVPECL/CML-TO-CML轉換器/中繼器數據表

LVPECL與LVPECL之間是如何進行連接的?LVPECL到CML的連接?

LVPECL與LVPECL之間是如何進行連接的?LVPECL到CML的連接?

評論