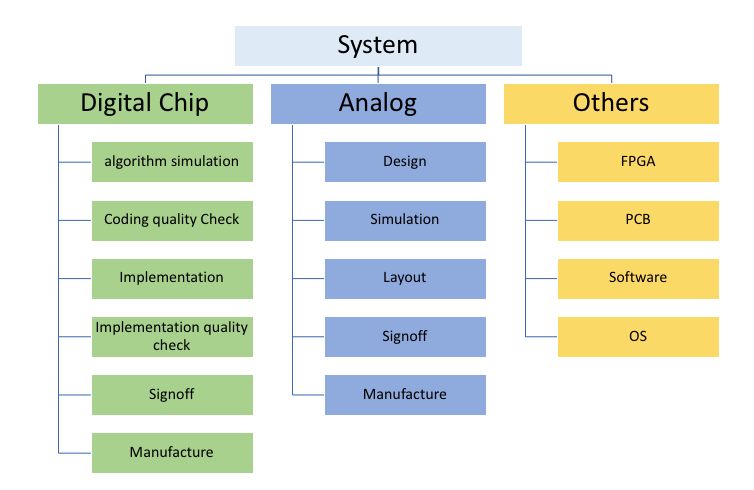

在各方助力下,集成電路成了時代熱點,有大量文章在寫芯片設計之復雜之困難,老驢打算從EDA 使用角度捋一遍芯片設計流程。在老驢畫出第一副圖之后,發現熟知的只有數字電路部分的一小段,對系統、軟件及上層應用完全無知,只能歸類為Others。

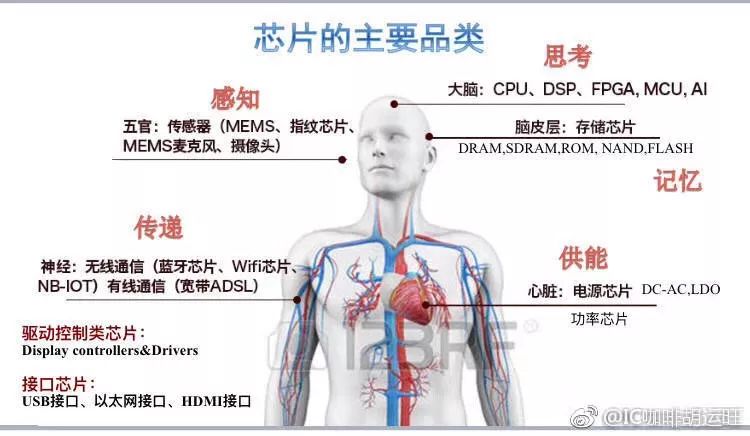

于消費者而言,一個可以使用的系統,有數字集成電路部分、模擬集成電路部分、系統軟件及上層應用部分。關于各個部分的功能,借用IC 咖啡胡總的精品圖可以一目了然。外部世界是一個模擬世界,故所有需要與外部世界接口的部分都需要模擬集成電路,模擬集成電路將采集到的外部信息轉化成0/1 交給數字集成電路運算處理,再將數字集成電路運算處理完的信號轉化成模擬信號輸出;而這一切的運算過程都是在系統軟件的號令跟監控下完成的,故曰:芯片是骨架,系統軟件是靈魂。

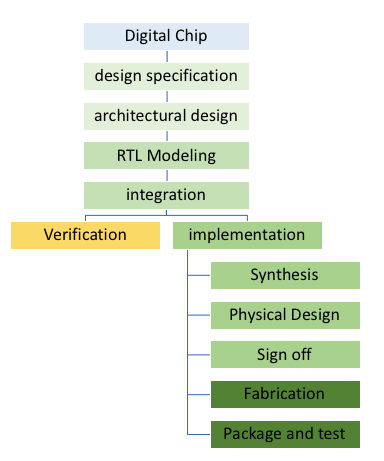

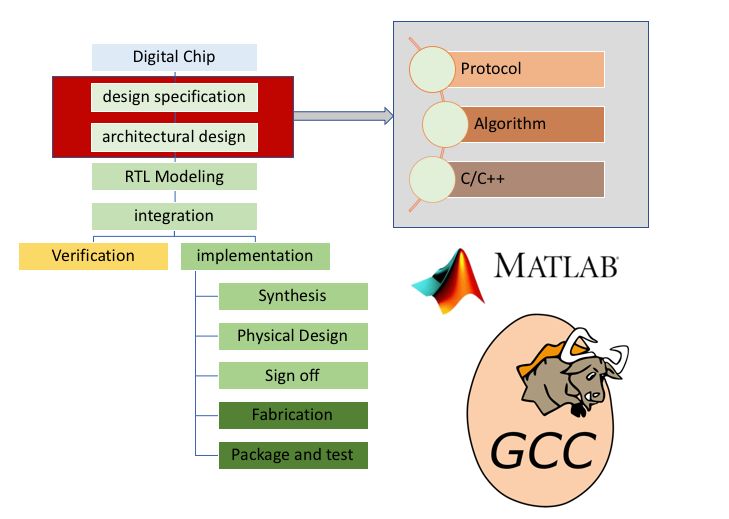

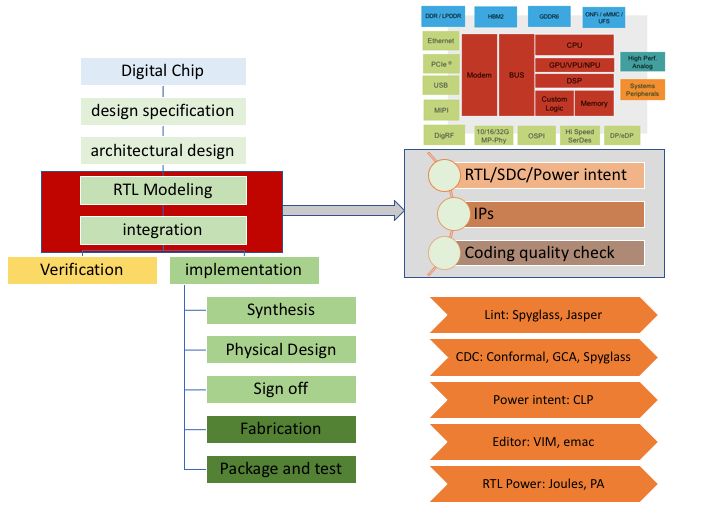

數字集成電路設計實現流程是個相當漫長的過程,拿手機基帶芯片為例,對于3G, 4G, 5G, 工程師最初見到的是無數頁的協議文檔。架構師要根據協議來確定:協議的哪些部分可以用軟件實現,哪些部分需要用硬件實現;算法工程師要深入研讀協議的每一部分,并選定實現所用算法;芯片設計工程師,需要將算法工程師選定的算法,描述成RTL; 芯片驗證工程師,需要根據算法工程師選定的算法設計測試向量,對RTL 做功能、效能驗證;數字實現工程師,需要根據算法工程師和設計工程師設定的目標PPA 將RTL 揉搓成GDS; 芯片生產由于太過復雜,完全交由代工廠完成,封裝亦是;對于測試,大部分公司都是租借第三方測試基臺由自己的測試工程師完成,只有少部分土豪公司才會有自己的測試基臺。

一顆芯片,性能的60% 取決于架構師,在國內好的架構師不超過三位數,極好的架構師不超過兩位數,架構師是芯片靈魂的締造者,是食物鏈的最頂端,是牛逼閃閃的存在,就驢淺顯認知,除了office 似乎沒有EDA 工具用于架構設計;架構敲定了之后,大量的算法工程師跟上,對于協議規定的每個點,都要選擇適當的算法,用C/C++ 做精確模擬仿真,要確保功能、精度、效率、吞吐量等指標,Matlab 跟GCC 應該是他們使用最多的工具。

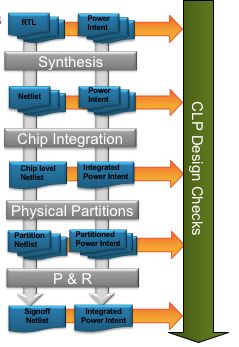

設計工程師根據算法工程師經過反復模擬仿真選擇的算法,將抽象描述或定點C 轉換成RTL, 在設計過程中需要反復仿真、綜合,以確定設計功能的正確性,跟設計能達到的PPA. 除了RTL, 設計工程師還需要根據設計目標編寫SDC 和power intent, 并做對應的質量檢查。設計工程師需要使用大量EDA 工具:

編輯器:VIM, emac;

Lint : RTL 質量檢查,Spyglass, Jasper;

CDC: SDC 質量檢查,Spyglass, Conformal, GCA;

CPF/1801: power intent 質量檢查,CLP;

Power: RTL 級功耗分析,Joules, PA;

仿真器:C, S, M 三家都有各自的仿真工具;

綜合:Genus, DC;

老驢以為,從集成開始,由腦力勞作進入體力勞作,對比蓋房子,就是從設計師到泥瓦工。集成工程師,要把芯片所用的所有模塊相互連接起來,指導思想是架構工程師確定的,各個IP 如何連接是各IP 的owner 確定的,集成工程師只要保證不多連、不少連、不亂連即可,據說當前也沒有什么有效的集成工具,常用到的是emac。

驗證

接著捋,實際項目中驗證跟綜合從RTL coding 開始就會交叉進行,反復迭代。

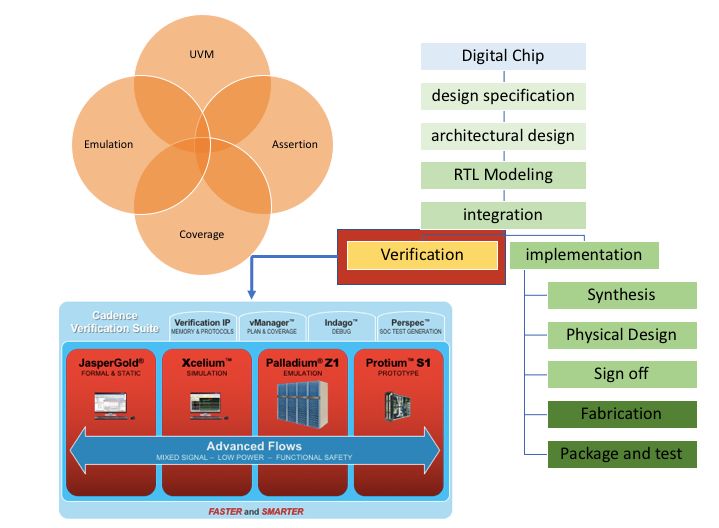

驗證在數字芯片設計中占很大比例,近些年在設計復雜度的推動下驗證方法學跟驗證手段在不斷更新,從OVM 到UVM, 從Dynamic verification 到Static verification, 從FPGA 到Emulator, 所有革新目的可概括為:快速、完備、易調試。驗證涉及到許多方面,驗證工程師一方面要對相關協議算法有足夠了解,根據架構、算法工程師設定的目標設計仿真向量;另一方面要對設計本身足夠了解,以提高驗證效率,縮短驗證時間。驗證工程師需要掌握許多技術,需要使用許多工具。

語言:各種腳本語言之外,C/C++, SystemVerilog, Verilog;

協議:各種接口協議,各種通信協議,各種總線協議;

工具:動態仿真工具,靜態仿真工具,FPGA, Emulator;

數字驗證領域,依舊是C, S, M 三家幾乎全霸,老驢已不做驗證多年,對S, M 兩家驗證相關工具除了VCS, Verdi, Modelsim 其他幾乎無知,此處拿C 家驗證全套為例。

Static Verification: Jasper Gold 是C 家新近推出的靜態驗證工具,驢所理解的靜態驗證是基于斷言的驗證方法學,所謂靜態即不需要輸入測試激勵,驗證過程是純數學行為。

Dynamic Verification: Xcelium 是C 家的動態驗證工具,驢所理解的動態驗證是基于UVM 的驗證方法學,通過輸入測試激勵,監控仿真結果,分析覆蓋率完成功能驗證。

Emulator: 硬件仿真加速器,粗暴理解:有debug 功能的集成了豐富接口的巨型可編程陣列;特點:超高速驗證、支持系統軟件調試。帕拉丁是C 家在驗證領域的明星產品,是行業翹楚,據說常有欽差蒞臨硅廠在帕拉丁前駐足良久,賞其外形之美,贊其功能之強。

Verification IP: 驗證需要各種驗證模型,各種IP, 各種總線,各種高速接口。

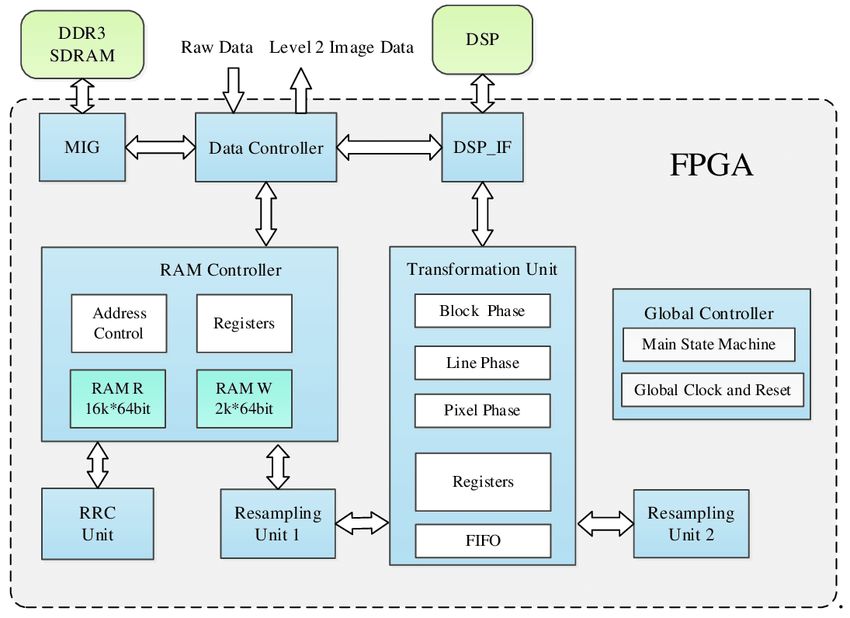

FPGA 的一大應用是驗證,故提一嘴。在世上曾經有兩家牛逼閃閃的FPGA 公司,一家是Altera 另一家是Xilinx, 后來Altera 像Mentor 一樣找了個大爺把自己賣了。FPGA 內除了可編程邏輯之外,通常還會集成各種IP, 如CPU, DSP, DDR controller 等。每家FPGA 都有各種配置,根據集成的IP, 可編程邏輯的規模,可達到的速度,價格相差極大。相對于ASIC, FPGA 也有一套對應的EDA 工具,用于綜合、布局布線、燒錄、調試。如:Synplify, Quartus。

國內現狀:Static Verification, Dynamic Verification, Emulator 幾乎空白;國內有一些FPGA 公司,在中低端領域已經做得非常不錯,但是高端領域幾乎空白。任重而道遠,不矯飾,腳踏實地干!

實現

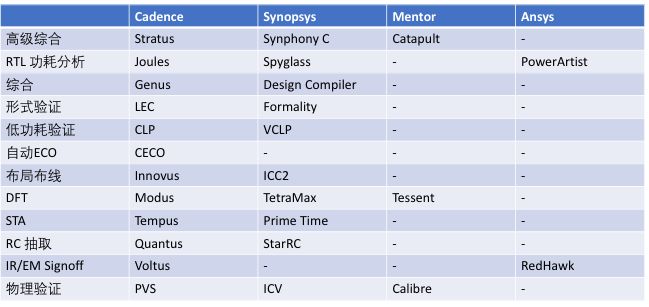

接著上面說的我們繼續捋數字芯片設計實現流程,今天進入實現階段,對于這一段驢只熟悉其中的綜合、形式驗證、低功耗驗證、RTL 功耗分析、STA, 其他部分都是一知半解,故無深究,只捋流程。

整個實現階段,可以概括成玩EDA 工具及基于EDA 工具的方法學,EDA 工具無疑是實現階段的主導,一顆芯片做得好不好,在實現階段之前基本取決于工程師的能力強不強,而在實現階段之后基本取決于EDA 工具玩得好不好。整個設計實現流程,涉及到許多工具,此處列出四家主要參與者,空白部分不代表沒有,只代表驢不知。

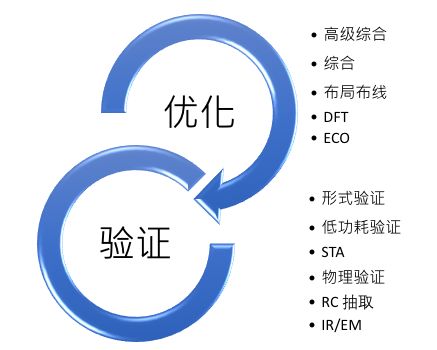

數字電路實現流程,從大方向上可以分成兩部分:優化跟驗證。優化,會更改邏輯描述方式,會更改邏輯結構,會插入新邏輯,這所有的動作都存在引入錯誤的風險,故需要驗證工具予以監控;驗證,要確保邏輯優化過程不改變邏輯功能,要確保時序滿足既定目標需求,要確保無物理規則違規,要確保信號完整性,這所有的驗證都有一套對應的通過規則,但凡有某一項不達標,就不能拿去生產制造。

高級綜合:所謂的高級綜合就是將C/ C++/ System C描述的設計意圖,“翻譯”成用Verilog/ System Verilog 描述的RTL, 多應用于運算邏輯主導的設計,除了三巨頭,市面上有許多小公司在這一個點上也做得不錯。

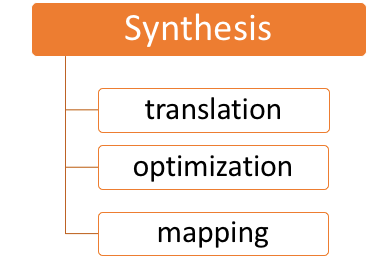

綜合:在實現流程中,就背后算法而言,綜合一定是最難最復雜的。綜合首先將Verilog/ System Verilog/ VHDL 描述的邏輯轉化成由Gtech 描述的邏輯,再對Gtech 邏輯做優化,優化后再將Gtech 描述映射到對應工藝庫。其中優化過程涉及到多個方面,近年來EDA 工具的發展方向基本可以概括為:容量,速度,相關性。容量:指可處理的設計規模;速度:指EDA 工具的優化速度;相關性:指跟布局布線之間的相關性。主流工具:Genus, Design Compiler. 在這一點上,幾乎再難有后起之秀,除非有朝一日,整個數字電路的設計方法學發生顛覆性的革新。

DFT: 插入壓縮解壓縮邏輯,插入scan chain, 插入Mbist, 插入Lbist, 插入Boundary Scan, 插入OCC, 插入Test Point, 生成ATPG pattern, 故障診斷,DFT 工程師像老中醫插入、觀察、診斷。當今市面上DFT 工程師緊缺,貴!主流工具:Tessenst, Modus, TetraMax.

ECO: 但凡有新的東西引入,就可能引入bug, 早期發現bug 可以重新走一遍實現流程,如果在后期發現bug 重走一遍流程的代價太大,通常的做法就是ECO. 對于簡單的bug 修復手工ECO 就可以,但是對于復雜的bug 修復,手工ECO 有心無力,故需要有EDA 工具來完成相應的工作。當前世面上最好用的自動ECO 工具非Conformal ECO 莫屬。最近也有一些startup 做對應的點工具,整個思路跟CECO 類似,但是沒有自己的綜合工具優化ECO 后的補丁,就很難得到一個好的結果。

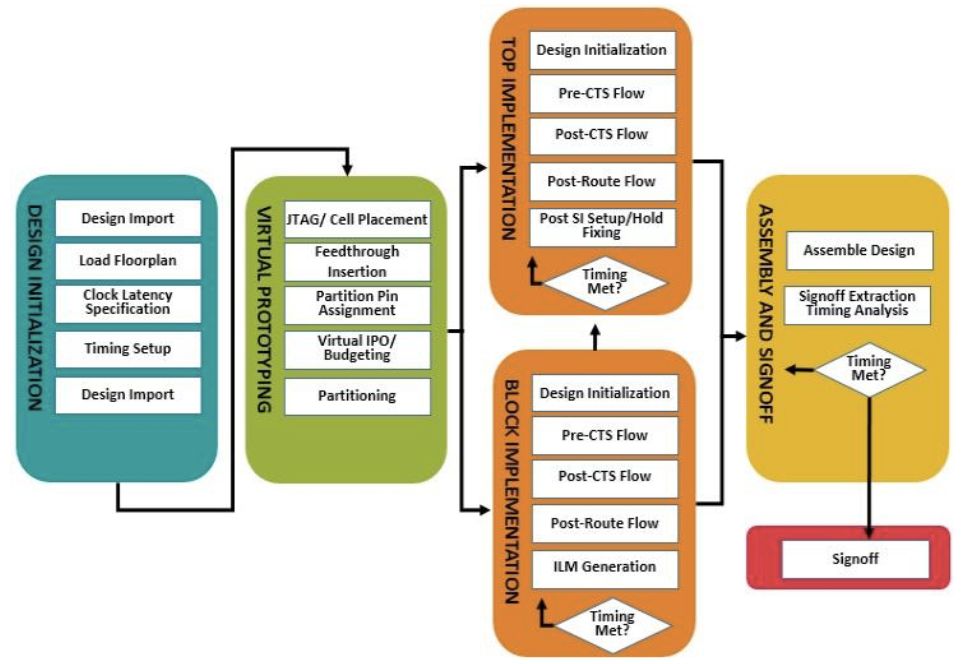

布局布線:在進入納米時代之前,布局布線并沒那么復雜,從90nm 開始到如今的3nm,布局布線的復雜度呈指數增長,從floorplan 到placement 到CTS 到Routing 每一步涉及到的算法在近年都做了顛覆性的革新,以Innovus 的問世為起點,布局布線進入到了一個新紀元。在AI 的浪潮下C 跟S 都一頭扎了進去,要做世上最智能的布局布線工具,也許有朝一日可以像跟小度對話一樣:

硅農:Innovus 請解析A 文件,按設定目標做個功耗最優的結果;

Innovus: 已讀取目標文件,根據設計數據分析,本設計大概需要250G 內存,在5小時內完成,請選擇任務完成后是否自動進入后續程序。..。..

RTL 功耗分析:這一步可以放在實現端做也可以放在實現之前做。分析過程相對簡單:讀入RTL, SDC, 仿真激勵,通過計算分析平均功耗跟瞬時功耗,找出設計中的“功耗缺陷”,指導Designer 進行功耗優化。主流工具有:Joules, Spyglass, PowerArtist.

形式驗證:在整個實現流程中,形式驗證充當邏輯功能等效性的監察官,任何一步優化結束后都需要過形式驗證這一關,以確保在優化過程中,邏輯功能未被改變。主流工具:LEC, Formality. 隨著設計規模的暴增跟優化技術的飛速發展,形式驗證的難度逐漸增加,占用的時間逐漸增多,SmartLEC 是針對復雜設計的先行者。

低功耗驗證:針對低功耗設計,低功耗驗證要驗證CPF/ UPF/ 1801 的語法語義跟描述意圖,要驗證低功耗單元未多插,未漏插,未亂插,要驗證電源跟地的鏈接符合設計意圖,要驗證電特性的完整性。主流工具:CLP。

STA: Timing signoff, STA 看似龐雜,其實并不復雜,相比于優化過程要簡單得多,拋開Timing ECO, STA 所有的動作都只是計算而不是求解,不恰當的比方:STA 就好比幼兒園的算術題,加數跟被加數都在那里,只要求個和即可;而優化過程是求最優解或近似最優解的過程,要難得多。近年來STA EDA 工具主要在幾個方向著力:如何模擬制造過程的隨機工藝偏差,如何處理超大規模設計,如何模擬新工藝結點電特性對時序的影響。

Power Signoff: 驗證設計的電源網絡是否足夠強悍,分析,發現,修正:IR-drop 跟EM. 主流工具:Voltus, RedHawk.

物理驗證: 驗證所有的管子、過孔、走線是否滿足Foundry 制定的規則,是個體力活,有點像蓋好房子之后的垃圾清理,主流工具:Calibre, PVS, ICV.

整個數字實現流程中涉及到諸多工具,三巨頭在領跑,后面基本沒有跟隨者,偶爾有某個點工具做得好的后起之秀,大多都會被三巨頭吃了,這也算是行業套路。就市值看,三巨頭加起來來也不及互聯網公司一條腿粗,然而在整個芯片設計實現過程中卻不可或缺,吾國要強大芯片產業,必須要在EDA 這一塊加大投入,方能離脫離被掐著脖子走更進一步。

-

集成電路

+關注

關注

5381文章

11381瀏覽量

360850 -

芯片設計

+關注

關注

15文章

1001瀏覽量

54811

原文標題:漲知識了,芯片設計流程最全講解!

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

據說是最全的LED封裝原材料芯片和支架知識

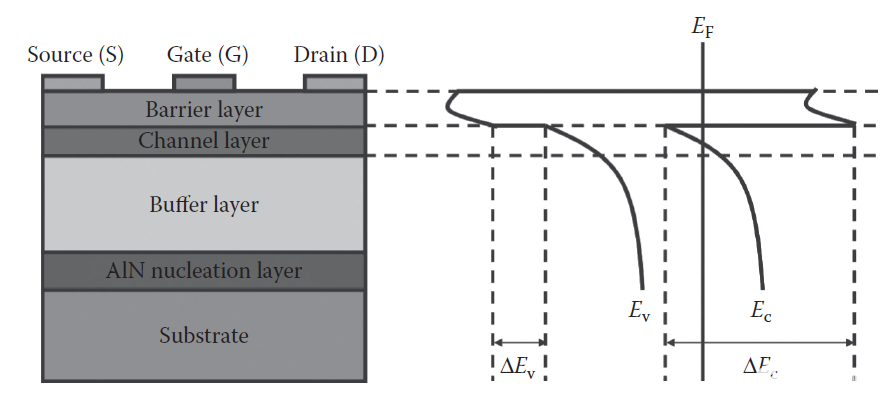

《漲知識啦19》之HEMT 的電流崩塌效應的講解

漲知識了,芯片設計流程最全講解!

漲知識了,芯片設計流程最全講解!

評論