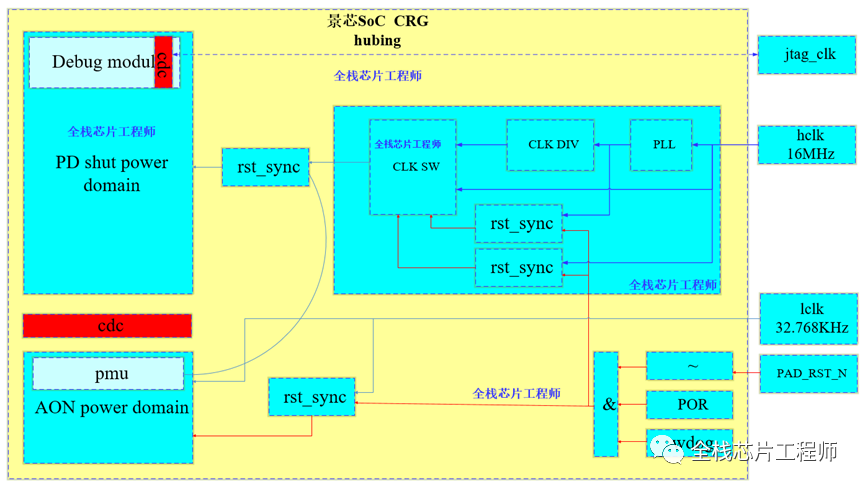

本章節講解數字前中后端都不得不熟練的clock switch設計。

芯片運行過程中需要時鐘切換時,要考慮到是否會產生glitch,小小的glitch有可能導致電路運行的錯誤。所以時鐘切換時需要特別的處理。

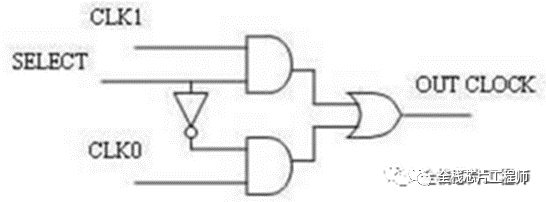

直接使用MUX進行時鐘切換或者采用如下電路結構進行時鐘切換:

assignoutclock=select?clk1:clk0;assignoutclock= (clk1 & select) | (~select & clk0);

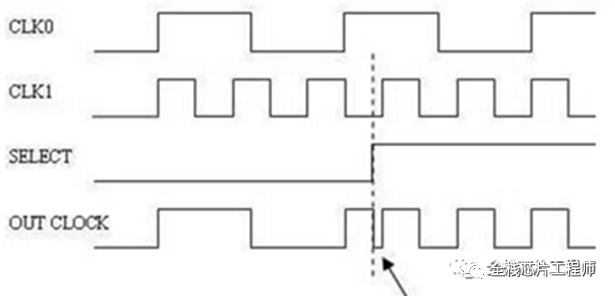

兩種做法都會產生時鐘切換毛刺的,芯片系統很容易進入亞穩態的情況。

為了解決時鐘切換的毛刺問題,對于時鐘源分為同步和異步的情況,分為如下兩種解決方案:

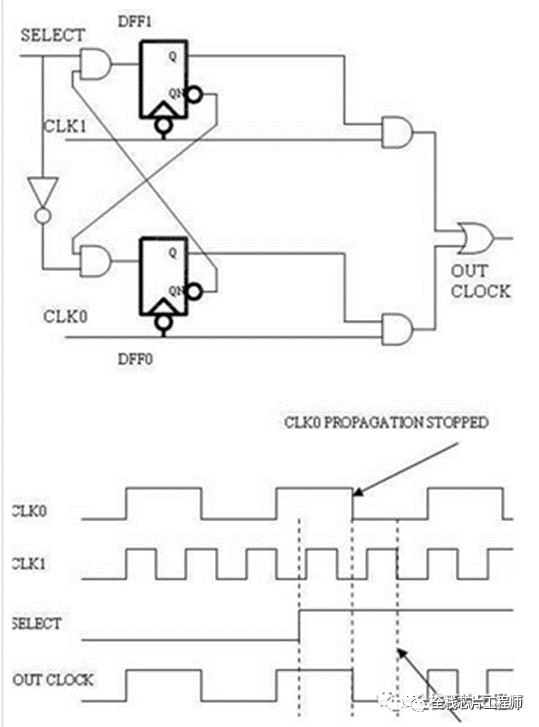

CLK0與CLK1為同步時鐘源,即CLK0與CLK1成整數倍關系

插入下降沿觸發的D觸發器,當前已打開的時鐘路徑上的時鐘會在其下降沿之后先關閉,然后待打開時鐘路徑上的時鐘在其下降沿之后即打開。

如下所示:從下圖第二個箭頭開始,實際發生時鐘切換。

那么,請問CLK0與CLK1為異步時鐘時,電路如何設計?

審核編輯:劉清

-

D觸發器

+關注

關注

3文章

164瀏覽量

47865 -

Mux

+關注

關注

0文章

38瀏覽量

23354 -

CLK

+關注

關注

0文章

127瀏覽量

17128 -

時鐘切換電路

+關注

關注

0文章

7瀏覽量

5768

原文標題:不得不熟練的clock switch?設計

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字前中后端都不得不熟練的clock switch設計

數字前中后端都不得不熟練的clock switch設計

評論