1、模塊整體布局時(shí),WIFI模組要盡量遠(yuǎn)離DDR、HDMI、USB、LCD電路以及喇叭等易干擾模塊或連接座;

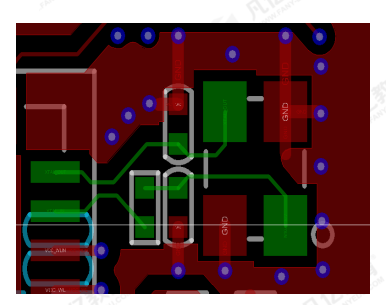

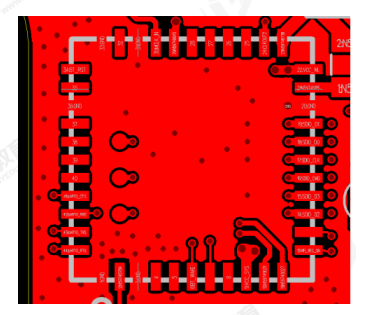

2、晶體電路布局需要優(yōu)先考慮,布局時(shí)應(yīng)與芯片在同一層并盡量靠近放置以避免打過孔,晶體走線盡可能的短,遠(yuǎn)離干擾源,盡量天線區(qū)域;晶體以及時(shí)鐘信號需要全程包地處理,包地線每隔100mil至少添加一個(gè)GND過孔,并且必須保證鄰層的地參考面完整,如圖1所示。

3、32.768k單獨(dú)走線,并做包地處理,并且包地線每隔400mil,至少添加一個(gè)GND 過孔;

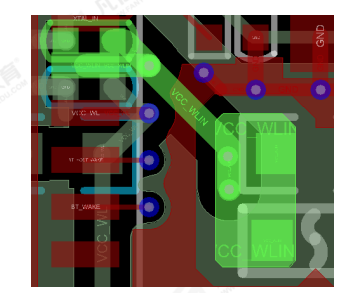

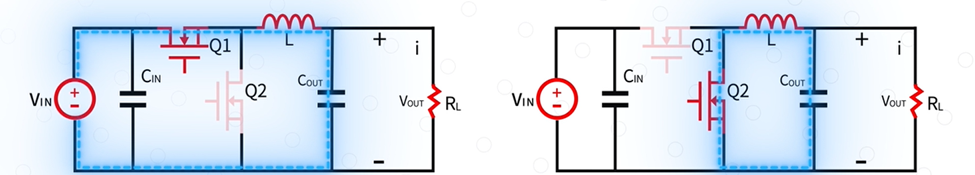

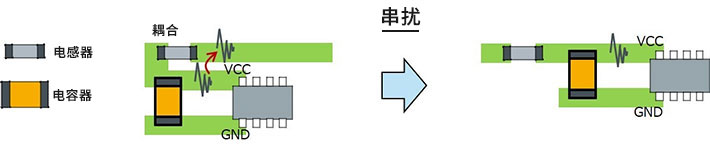

4、VBAT電源工作時(shí)電路較大,單天線模組600mA以上,整個(gè)供電主回路須20mil以上,接入管腳的走線跨度與PIN腳同寬,如需打孔至少兩個(gè)過孔;VBAT的電源去耦電容必須靠近模組電源管腳,與旁邊的晶體時(shí)鐘走線用10mil左右的地線隔離,如圖2所示。

圖1 晶體的布局與布線

圖2 VBAT去耦電容的放置

5、天線匹配電路必須靠近天線座,天線走線50歐姆(根據(jù)實(shí)際疊層情況可以做隔層參考),保證參考地的完整,下方不允許有其他信號線或電源;

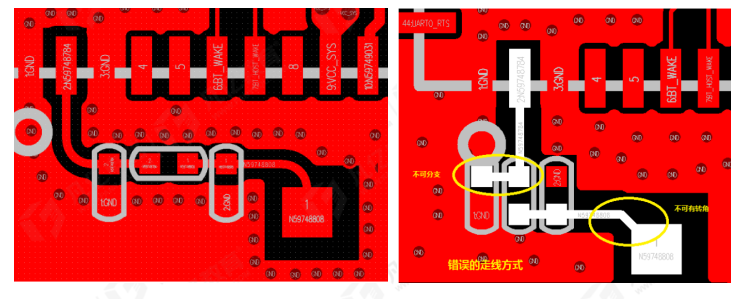

6、天線布線越長,能量損耗越大,因此在設(shè)計(jì)時(shí),天線路徑越短越好,不能有分支出現(xiàn),盡量不換層;天線周圍需要多打地過孔,天線走線有遇到需轉(zhuǎn)向時(shí),不可以用轉(zhuǎn)角的方式,需用弧形走線。如圖3所示。

圖3 天線走線示意圖

7、如果是2X2 MIMO天線接口,兩個(gè)天線口之間的出線方向需要考慮兩個(gè)天線的位置,兩個(gè)天線的位置需要盡量遠(yuǎn)離避免干擾,并考慮垂直放置以避免互相干擾。

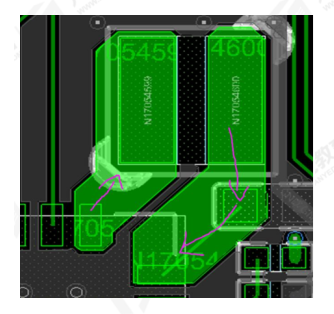

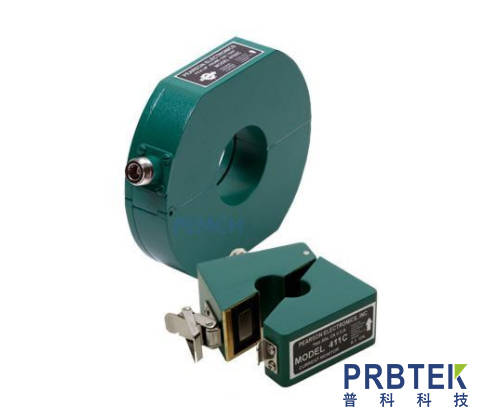

8、模組的電感布局時(shí),請注意走線經(jīng)電感出來后,先經(jīng)過電容,再進(jìn)入模組電源管腳,如圖4所示。模組下方第一層保持完整的地,不要有其他信號走線,如圖5。

圖4 功率電感走線示意圖

圖5 功率電感走線示意圖

9、SDIO_D0-D3、SDIO- CMD和SDIO_CLK 6根走線盡量要平行等長,走線長度相差控制在±25mil以內(nèi), 并且相鄰層要遠(yuǎn)離其他電源和時(shí)鐘走線,SDIO_CLK需要全程包地處理

聲明: 本文凡億教育原創(chuàng)文章,轉(zhuǎn)載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396299

原文標(biāo)題:WIFI與BT的PCB布局布線注意事項(xiàng)

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

電源PCB布局布線注意事項(xiàng)

CC13xx/CC26xx硬件配置和PCB設(shè)計(jì)注意事項(xiàng)

Buck電路中PCB layout布局設(shè)計(jì)和注意事項(xiàng)

ESP32C3連接國外WIFI有哪些注意事項(xiàng)?

PCB設(shè)計(jì)的EMC有哪些注意事項(xiàng)

FPGA的高速接口應(yīng)用注意事項(xiàng)

FMD LINK 使用注意事項(xiàng)

高頻高密度PCB布局設(shè)計(jì)注意事項(xiàng)

PCB板布局相關(guān)的注意事項(xiàng)

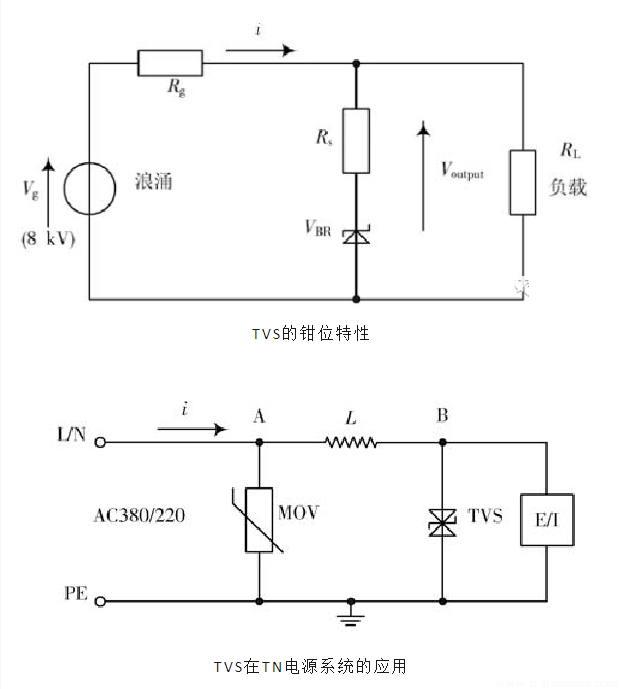

瞬態(tài)抑制二極管(TVS)的注意事項(xiàng)與布局布線?|深圳比創(chuàng)達(dá)電子a

關(guān)于PCB布局布線技巧的104的問題

霍爾元件使用的注意事項(xiàng)

電流互感器的使用注意事項(xiàng)

WIFI與BT的PCB布局布線注意事項(xiàng)

WIFI與BT的PCB布局布線注意事項(xiàng)

評論