在ASIC設計中,我們使用FIFO或者RAM的時候經常會用到校驗位,例如奇偶校驗或者ECC(海明碼)校驗,當然,也有可能不使用任何校驗位。那么我們需要一個深度為32,數據位寬為119bit的ram(cfg_32x119_ram_wrapper),那么實際底層的ram尺寸到底是多少呢?就是32x119 嗎?大概率不是。

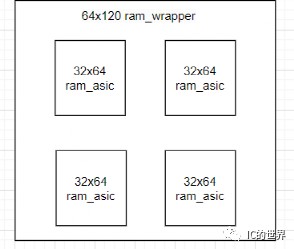

1.一個ram wrapper可能是拼接而成的

RAM的位寬和深度不是任意的,是根據設計人員的需求,然后由工具產生相應的ram。我們需要的是32x119的ram,實際分配給設計人員的可能是兩個32x64的ram,深度和寬度都可能存在冗余。Ram的產生通常有兩種方式,由設計人員或者中端人員提供ram信息列表。至少包含如下信息:Memory生成工具會根據實際需要的位寬,深度,讀寫時鐘頻率才進行決策,產生相應的Memory。

| RAM_NAME | RAM_TYPE | DEPTH | WIDTH | ECC/PARITY | Wclk_freq | Rdclk_req |

| afifo_16x72_wrapper | 1r1w | 16 | 72 | 1 | 1200 | 1000 |

一顆大的ram可能是有多個小的ram拼接起來的。在布局布線時,多個小的方形的ram大概率會比長條形狀的ram更容易擺放(不絕對)。

2.ram/fifo 校驗位需要額外的數據位寬

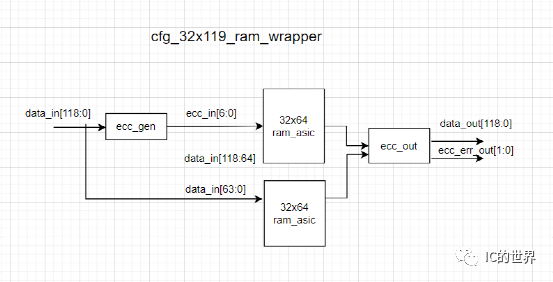

如圖所示為1r1w的ram為例,cfg_32x119_ram_wrapper為verilog代碼直接調用層次的ram_wrapper,表示了一個深度為32,數據位寬為119bit的ram。ram_asic.v為真實的ram IP。其中119bit的數據位寬緊張ECC計算需要7bit的校驗位,因此物理IP最少需要126bit的ram IP。通常memory產生工具會更具時鐘頻率,深度位寬等因素對ram進行切分,因此本例中,使用了2個32x64的ram ip。

在data_in寫入ram_asic模塊之前,會經過ecc_gen模塊,產生7bit的ecc校驗位,隨著數據一同寫入ram_asic,其中data_in[63:0]寫入第一個ram_asic,{2’b0,ecc_in[6:0],data_in[118:64]}寫入第二個ram_asic。從ram_asic讀出的數據會經過ecc_out模塊經過ecc校驗,輸出校驗后的data_out[118:0]和2bit的ecc_err_out告警。

審核編輯:劉清

-

RAM

+關注

關注

8文章

1367瀏覽量

114545 -

ASIC設計

+關注

關注

0文章

33瀏覽量

10649 -

ECC

+關注

關注

0文章

97瀏覽量

20536 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

5965

原文標題:RAM:位寬與深度是這樣確定的

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

實際底層的RAM尺寸到底是多少呢?就是32x119嗎?

實際底層的RAM尺寸到底是多少呢?就是32x119嗎?

評論