Testbench編寫指南(1)基本組成與示例

文章目錄

Testbench編寫指南(1)基本組成與示例

生成測試激勵

顯示結果

簡單示例

設計規則

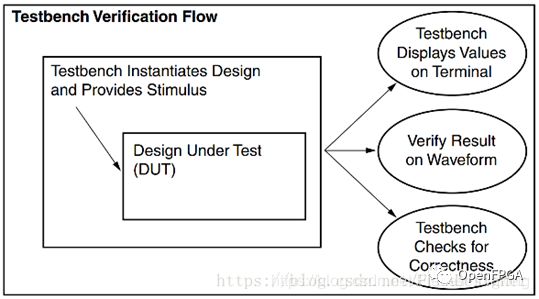

??對于小型設計來說,最好的測試方式便是使用TestBench和HDL仿真器來驗證其正確性。一般TestBench需要包含這些部分:實例化待測試設計、使用測試向量激勵設計、將結果輸出到終端或波形窗口便于可視化觀察、比較實際結果和預期結果。下面是一個標準的HDL驗證流程:

?TestBench可以用VHDL或Verilog、SystemVerilog編寫,本文以Verilog HDL為例。FPGA設計必須采用Verilog中可綜合的部分子集,但TestBench沒有限制,任何行為級語法都可以使用。本文將先介紹TestBench中基本的組成部分。

生成時鐘信號

??使用系統時鐘的設計在TestBench中必須要生成時鐘信號,該功能實現起來也非常簡單,示例代碼如下:

parameter ClockPeriod = 10;

//方法1 initial begin forever clock = #(ClockPeriod/2) ~ Clock; end //方法2 initial begin always #(ClockPeriod/2) Clock = ~Clock; end

生成測試激勵

??只有給設計激勵數據,才能得到驗證結果。提供激勵的方法有兩種,絕對時間激勵以仿真時刻0為基準,給信號賦值,示例如下:

initial begin reset = 1; load = 0; count = 0; #100 reset = 0; #20 load = 1; #20 count = 1; end ‘#’用于指定等待的延遲時間,之后才會執行下一個激勵。相對時間激勵給信號一個初始值,直到某一事件發生后才觸發激勵賦值,示例如下: always @ (posedge clk) tb_cnt <= tb_cnt + 1; initial begin ? ?if (tb_cnt <= 5) begin ? ? ? ?reset = 1; ? ? ? ?load = 0; ? ? ? ?count = 0; ? ?end ? ?else begin ? ? ? ?reset = 0; ? ? ? ?load = 1; ? ? ? ?count = 1; ? ?end end

??根據需要,可以同時使用兩種方法。每一個initial塊、always塊之間都是并行工作的關系,但在initial塊內部是順序地處理事件。因此復雜的激勵序列應該分散到多個initial或always塊中,以提高代碼可讀性和可維護性。

顯示結果

??Verilog中可以使用display和display和display和monitor系統任務來顯示仿真結果,示例代碼如下:

initial begin

$timeformat(-9, 1, "ns", 12);

$display(" Time clk rst ld sftRg data sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

??$display會將雙引號之間的文本輸出到終端窗口。$monitor的輸出為事件驅動型,如上例中$realtime變量用于觸發信號列表的顯示,%t表示$realtime以時間格式輸出,%b表示其余值以二進制格式輸出。其余還有%d、%h、%o等與慣例相同。

簡單示例

??下面是一個簡單的移位寄存器Verilog設計示例:

module shift_reg (clock, reset, load, sel, data, shiftreg);

input clock;

input reset;

input load;

input [1:0] sel;

input [4:0] data;

output [4:0] shiftreg;

reg [4:0] shiftreg;

always @ (posedge clock)

begin

if (reset)

shiftreg = 0;

else if (load)

shiftreg = data;

else

case (sel)

2'b00 : shiftreg = shiftreg;

2'b01 : shiftreg = shiftreg << 1;

? ? ? ? ? ?2'b10 : shiftreg = shiftreg >> 1;

default : shiftreg = shiftreg;

endcase

end

endmodule

??下面給出上述設計的TestBench示例:

module testbench; // 申明TestBench名稱

reg clock;

reg load;

reg reset; // 申明信號

wire [4:0] shiftreg;

reg [4:0] data;

reg [1:0] sel;

// 申明移位寄存器設計單元

shift_reg dut(.clock (clock),

.load (load),

.reset (reset),

.shiftreg (shiftreg),

.data (data),

.sel (sel));

initial begin // 建立時鐘

clock = 0;

forever #50 clock = ~clock;

end

initial begin // 提供激勵

reset = 1;

data = 5'b00000;

load = 0;

sel = 2'b00;

#200

reset = 0;

load = 1;

#200

data = 5'b00001;

#100

sel = 2'b01;

load = 0;

#200

sel = 2'b10;

#1000 $stop;

end

initial begin // 打印結果到終端

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

endmodule

??TestBench中包括實例化設計、建立時鐘、提供激勵、終端顯示幾個部分。每個initial塊之間都從0時刻開始并行執行。$stop用來指示仿真器停止TestBench仿真(建議每個TestBench中都有至少一個$stop)。$monitor會在終端以ASCII格式打印監測結果。

設計規則

??下面給出一些編寫TestBench的基本設計規則:

了解仿真器特性:不同的仿真器由不同的特性、能力和性能差異,可能會產生不同的仿真結果。仿真器可分為兩類:(1).基于事件,當輸入、信號或門的值改變時調度仿真器事件,有最佳的時序仿真表現;(2).基于周期,在每個時鐘周期優化組合邏輯和分析結果,比前者更快且內存利用效率高,但時序仿真結果不準確。即使是基于事件的仿真器,在調度事件時采用不同的算法也會影響到仿真性能(比如同一仿真時刻發生了多個事件,仿真器需要按一定的序列依次調度每個事件)。了解仿真器特性有一定必要,但目前最常用的ModelSim、Vivado Simulator等仿真器也已經非常強大。

避免使用無限循環:仿真器調度事件時,會增加CPU和內存的使用率,仿真進程也會變慢。因此除非迫不得已(比如利用forever生成時鐘信號),盡量不要使用無限循環。

將激勵分散到多個邏輯塊中:Verilog中的每個initial塊都是并行的,相對于仿真時刻0開始運行。將不相關的激勵分散到獨立的塊中,在編寫、維護和更新testbench代碼時會更有效率。

避免顯示不重要的數據:對于大型設計來說,會有超過10萬個事件和大量的信號,顯示大量數據會極度拖慢仿真速度。因此最好的做法是每隔N個時鐘周期顯示重要信號的數據,以保證足夠的仿真速度。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602022 -

仿真器

+關注

關注

14文章

1016瀏覽量

83647 -

Verilog

+關注

關注

28文章

1345瀏覽量

109996 -

HDL

+關注

關注

8文章

327瀏覽量

47344 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28512

原文標題:Testbench編寫指南(1)基本組成與示例

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

貼片機的基本組成

計算機的基本組成及工作原理

計算機的分類及基本組成

雷達發射機的任務和基本組成

計算機硬件的基本組成

單片機的基本組成

數控機床的基本組成、組成部分

Testbench基本組成與示例

Testbench的基本組成和設計規則

Testbench的基本組成和設計規則

評論