在芯片內部,信號一般都是通過并行傳輸?shù)模驗榇袀鬏攲嵲谑翘恕H欢酒腎O都是串行傳輸?shù)模⑿袀鬏攲τ?a target="_blank">硬件布局實在要求太高了,硬件工程師表示很頭大。而且芯片IO是芯片的重要資源,怎么能讓一組信號占用那么多呢!

芯片之間的串行數(shù)據傳輸對頻率很敏感,因為高頻會帶來更大的噪聲干擾、碼間干擾、電磁干擾等,進而導致信號失真。

一般在芯片的低速串行IO,采用不同的沿來發(fā)送和接收來避免信號干擾對采樣信號的影響,但是clk頻率都在100M以內,比如SPI協(xié)議,I2C協(xié)議。

但是當信號頻率到達幾百M或者G以上,通過不同的沿來發(fā)送和接收信號,已經不能避免信號干擾的問題了,高頻時鐘受噪聲干擾更為嚴重,到達采樣端已經完全失真了。而且clk與data之間的skew約束更為嚴格,幾乎不可能實現(xiàn)。

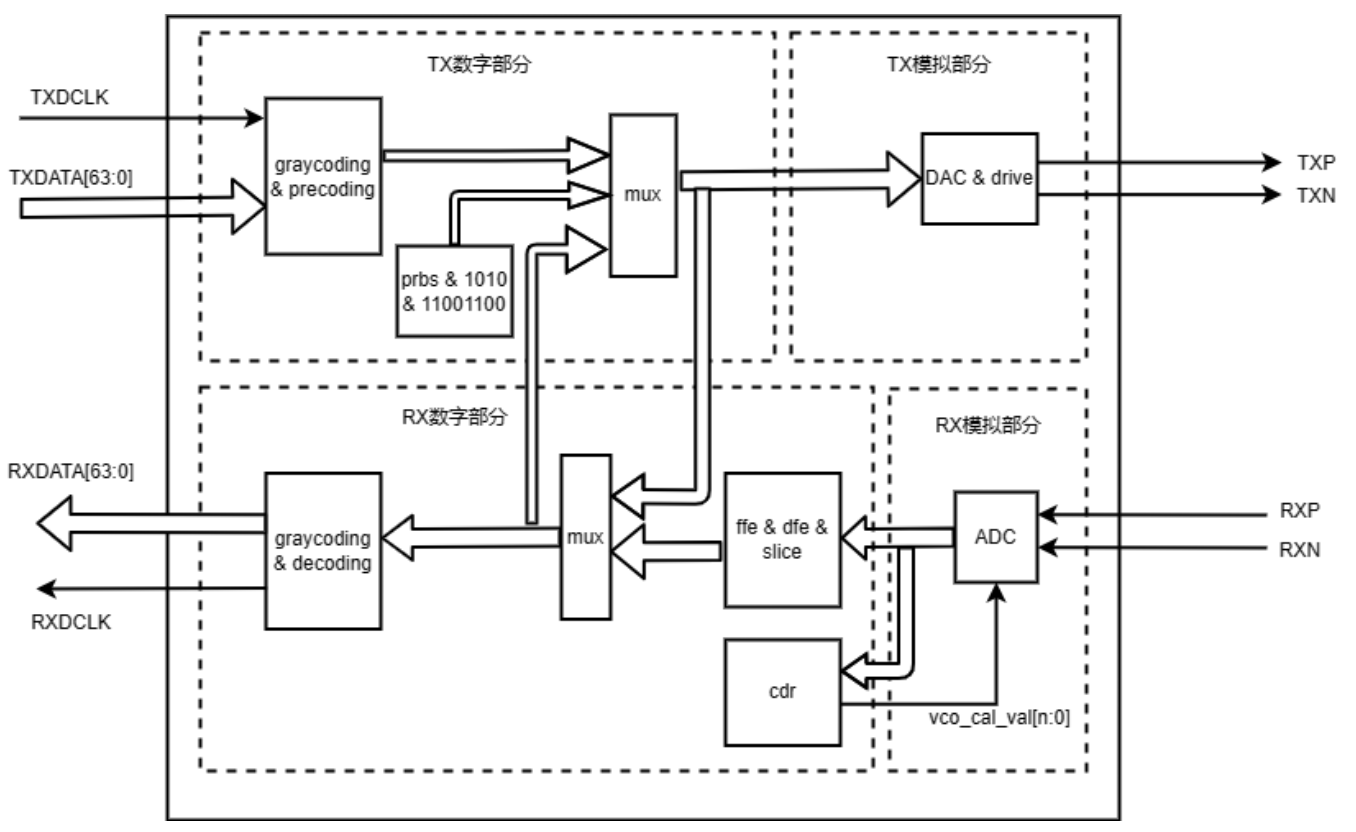

圖1:Serdes 結構圖

這個時候就需要應用serdes了,serdes包含了模擬和數(shù)字均衡來切實消除噪聲干擾、碼間干擾等。如下圖所示,serdes的RX模擬部分在ADC采樣之前有CTLE(線性均衡)來進行高頻濾波,然后通過ADC采樣模擬電平到數(shù)字域,然后通過CDR恢復數(shù)字時鐘,通過FFE/DFE進行數(shù)字信號均衡,然后進行數(shù)據判決,最終將判決后的data輸出給上層。

TX方向將輸入的信號進行FFE均衡,然后輸出給TX模擬部分發(fā)出給對端。通過發(fā)送端和接收端的一致均衡,來消除信道上未知的干擾。而且serdes可以從接收data里面恢復出采樣時鐘,避免了clk與data之間skew導致采樣時序以及時鐘失真的問題。

-

CLK

+關注

關注

0文章

127瀏覽量

17126 -

I2C協(xié)議

+關注

關注

0文章

26瀏覽量

8457 -

ADC采樣

+關注

關注

0文章

134瀏覽量

12831 -

串行數(shù)據傳輸

+關注

關注

0文章

4瀏覽量

6818 -

SERDES接口

+關注

關注

0文章

28瀏覽量

2964

發(fā)布評論請先 登錄

相關推薦

GMII、SGMII和SerDes的差異總結

申請TI Keystone DSP PCIe SerDes IBIS-AMI Models。

請問6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

SerDes是怎么工作的

參考時鐘對SERDES性能的影響

SERDES的優(yōu)勢 SERDES演變的看法

關于高速串行收發(fā)器的重要概念和注意事項

SerDes是怎么設計的?(一)

為什么我們需要SERDES?SERDES的優(yōu)點有哪些?

為什么要用Serdes?

為什么要用Serdes?

評論