引言:在異步邏輯器件中,信號不與時鐘信號同步,或者說該信號壓根就沒有對位的時鐘信號。本節簡述基本的異步邏輯--->1位拓撲和多位拓撲的緩沖器、反相器、驅動器和收發器。

1.反相器

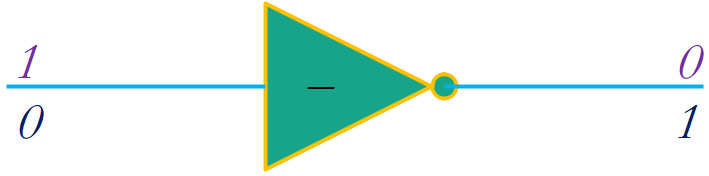

反相器實質就是一個非門,單反相器就是一個單非門,正邏輯中執行布爾函數

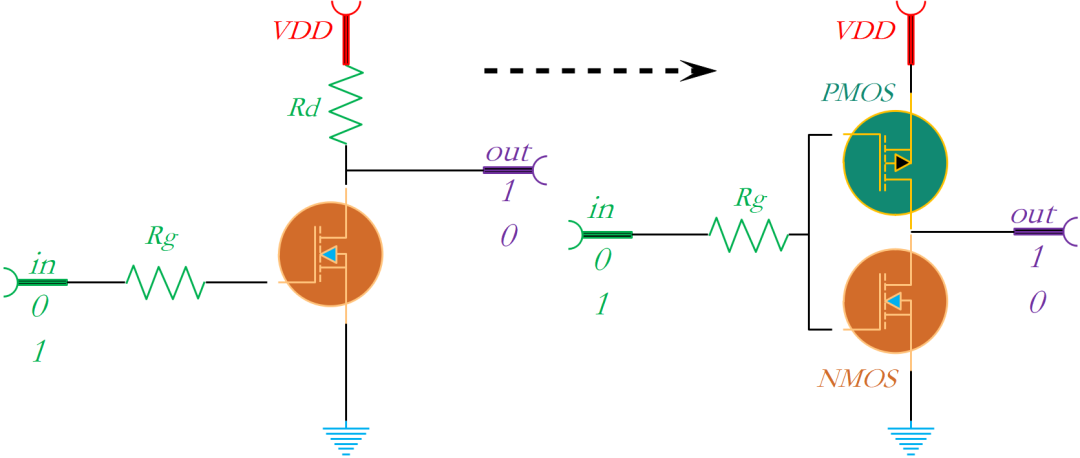

Y=A。如圖2-1右所示是CMOS結構的非門,芯片里面的最原始的構成就是如此。

圖2-1:CMOS結構的非門

圖2-2:非門圖例

圖2-3:反相器輸入輸出波形

對于反相器的關鍵參數,一個是時延,即輸入和輸出之間的延遲,一個是上升/下降時間,這兩個體現出反相器的性能

2.緩沖器(驅動器)

圖2-4:緩沖器圖例

如圖2-4是緩沖器的圖例,注意這里是緩沖而不是緩存Buffer,緩沖器在結構上是由兩個及以上反相器組成,如圖2-5是偶數的同相緩沖器示例,圖2-6是奇數反相緩沖器示例,圖2-7是帶控制的單通道同相緩沖器。

圖2-5:同相緩沖器

圖2-6:反相緩沖器

圖2-7:帶控制單通道同相緩沖器

從圖2-1的結構可以看出緩沖器將開關變化映射到VDD的切換,所以緩沖器可以用于刷新微弱的數字信號,這些信號通常是由連接到相當大的電容性負載或許多并聯輸入端的低強度驅動輸出產生的。緩沖器的輸出能重建一個適當形狀的數字波形并改善信號完整性,提供同相和反相兩種功能,圖2-8顯示緩沖器的刷新效果。

圖2-8:同相緩沖器改善波形

3.收發器

如 圖2-9

,收發器是一個雙向緩沖器,用于從數據總線接收和/或向數據總線發送數據,使用方向控制引腳選擇數據流的方向。數字信號的本質就是0和1,電氣層面就是高低電平不斷切換,芯片接收端接收到信號后傳遞給ADC或者電平比較器作閾值判斷以此來識別接收的信號是0還是1。

獨立的收發器元器件,從其緩沖器構成來看,也是做一個信號中繼和增強,重建一個適當形狀的數字波形并改善信號完整性。

圖2-9:收發器結構

簡單的收發器由兩個緩沖器和方向控制電路組成,其他類型的收發器還包括鎖存器或寄存器,可以存儲輸入值并在需要時將其釋放到輸出端。收發器具有多種拓撲,例如與總線連接要求有關的1、2、4、8、16或18位版本,收發器可提供多種相關功能:

1:開漏輸出

2:輸入總線保持功能可在輸入端未獲有效驅動時保持輸入值

3:施密特觸發器和施密特動作輸入提供輸入遲滯

-

收發器

+關注

關注

10文章

3397瀏覽量

105864 -

驅動器

+關注

關注

52文章

8156瀏覽量

146010 -

緩沖器

+關注

關注

6文章

1917瀏覽量

45450 -

反相器

+關注

關注

6文章

310瀏覽量

43244 -

邏輯器件

+關注

關注

0文章

88瀏覽量

20089

發布評論請先 登錄

相關推薦

緩沖器/線路驅動器,非反相(IC)74HC244D,65374HC244D

具有開漏輸出的十六進制反相器緩沖器/驅動器SN74AUC06 數據表

漏極開路輸出的十六進制反相器緩沖器/驅動器SN74LVC06A數據表

異步邏輯器件之反相器、緩沖器(驅動器)和收發器

異步邏輯器件之反相器、緩沖器(驅動器)和收發器

評論