本文介紹如何搭建一個通用的圖像處理平臺,采用HDMI接口進行輸入、輸出,可用于測試基于HLS的FPGA圖像處理項目。

01硬件平臺

Zynq-700 ARM/FPGA SoC開發板套件。

02操作步驟

概述

本文演示如何搭建一個簡單的基于Xilinx FPGA的圖像處理平臺,可用于后續基于HLS(高層次綜合)的項目,并且可以采用標準的OpenCV庫輔助開發。

該項目采用Zybo Z7型號FPGA進行開發,該開發板上集成了HDMI輸入輸出接口,以及可以連接MIPI相機的CSI-2接口,便于后續開發使用。除了FPGA板卡外,還需要:1. HDMI相機;2. HDMI輸入輸出相關線纜;3. HDMI接口顯示屏。

軟件開發方面,采用:1. Vivado 2017.4;2. Xilinx SDK 2017.4;3. Digilent Vivado庫。

創建該項目,需要準備以下工作:1. 下載并解壓Digilent Vivado庫;2. 配置Digilent 板卡參數;3. 新建Zybo-Z7型號Vivado block 工程。

創建工程

在Vivado block design中添加以下IP核:

- ZY NQ處理系統 (用于圖像處理系統的配置核控制),PL時鐘0設為200MHZ,PL時鐘1設為100MHZ,啟用HP0總線(用于和PS端DDR傳輸圖像數據),啟用GP0總線(用于系統參數配置)。

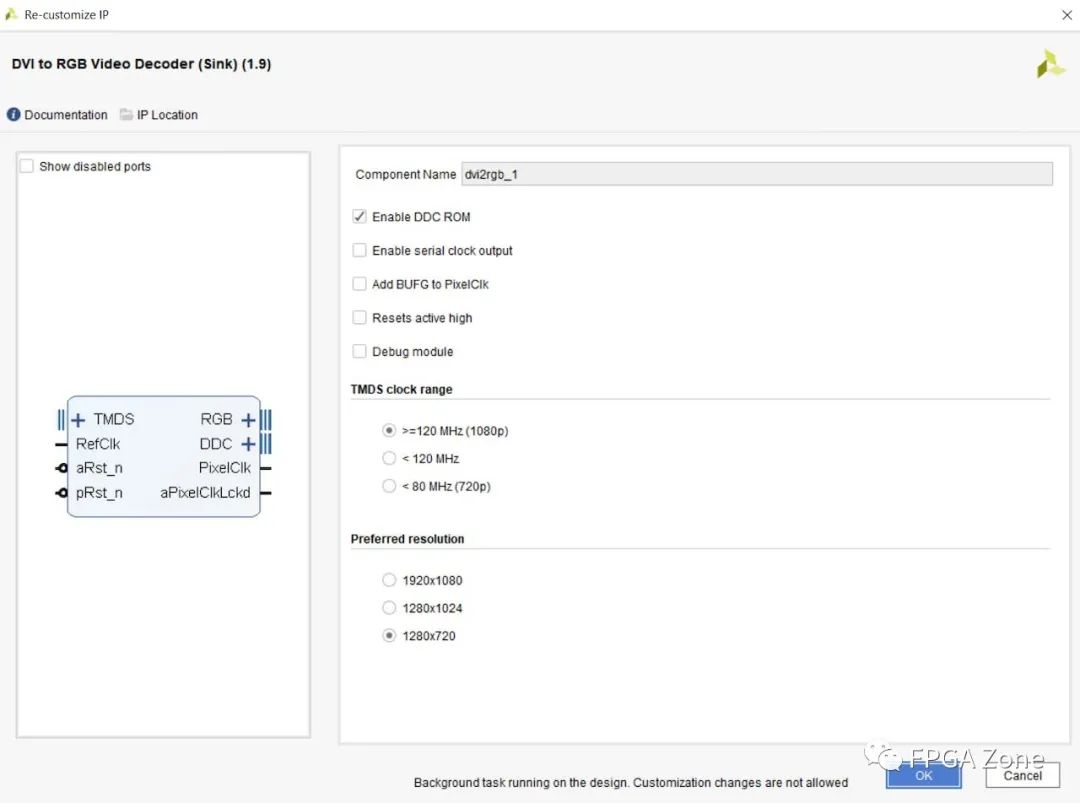

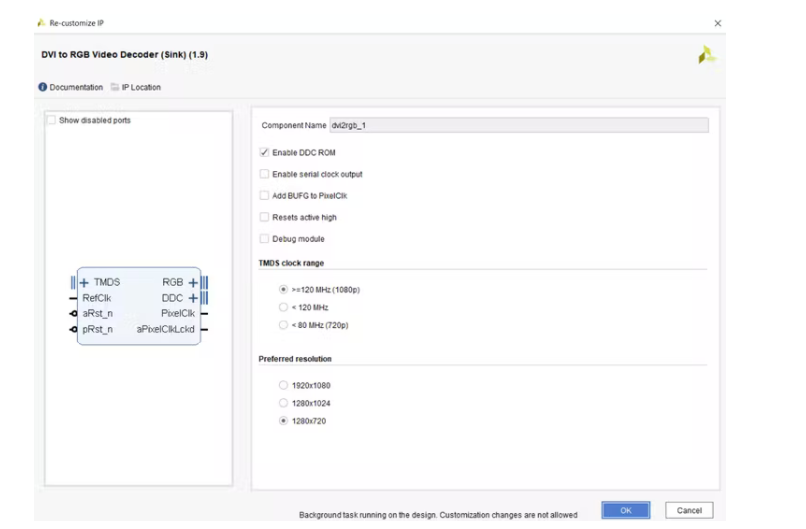

- DV I2RGB,將HDMI視頻流轉化為24位寬的RGB數據流。

圖2 配置DVI2RGB IP核

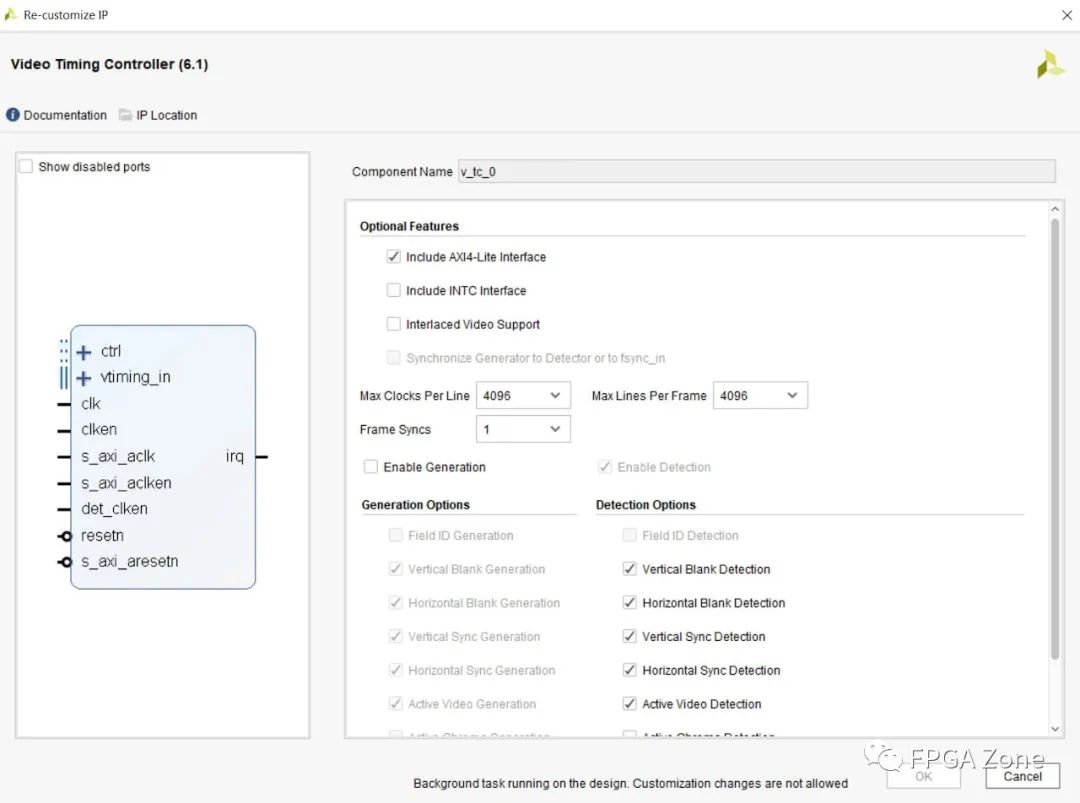

圖3 配置VTC IP核

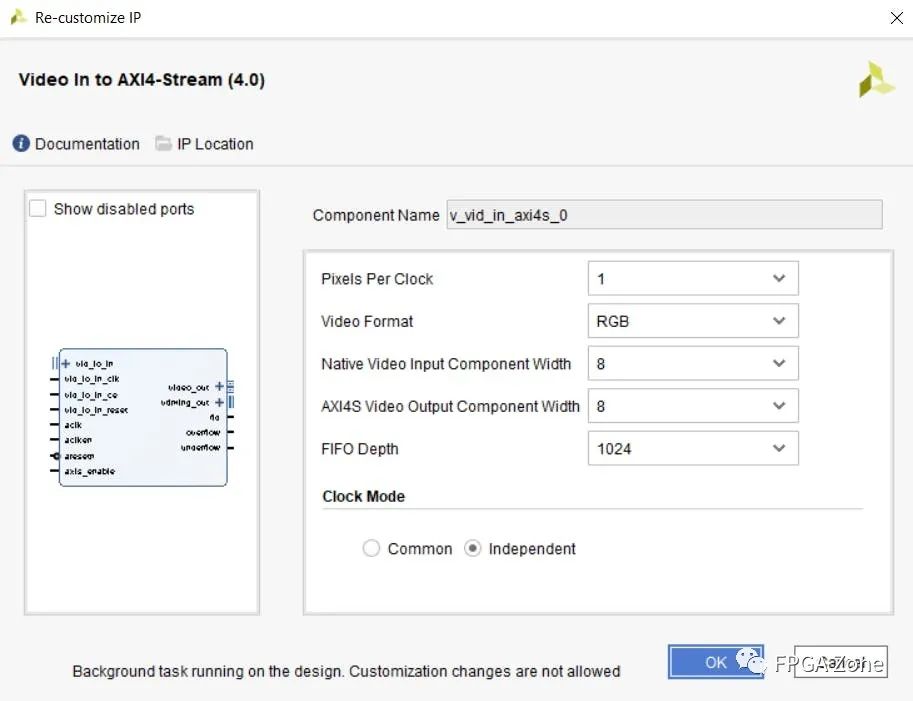

- Video In to AXI4-Stream,將視頻數據轉換為AXI數據流。

圖4 配置VIA IP核

圖5 配置AXI4-Stream Subset Converter IP

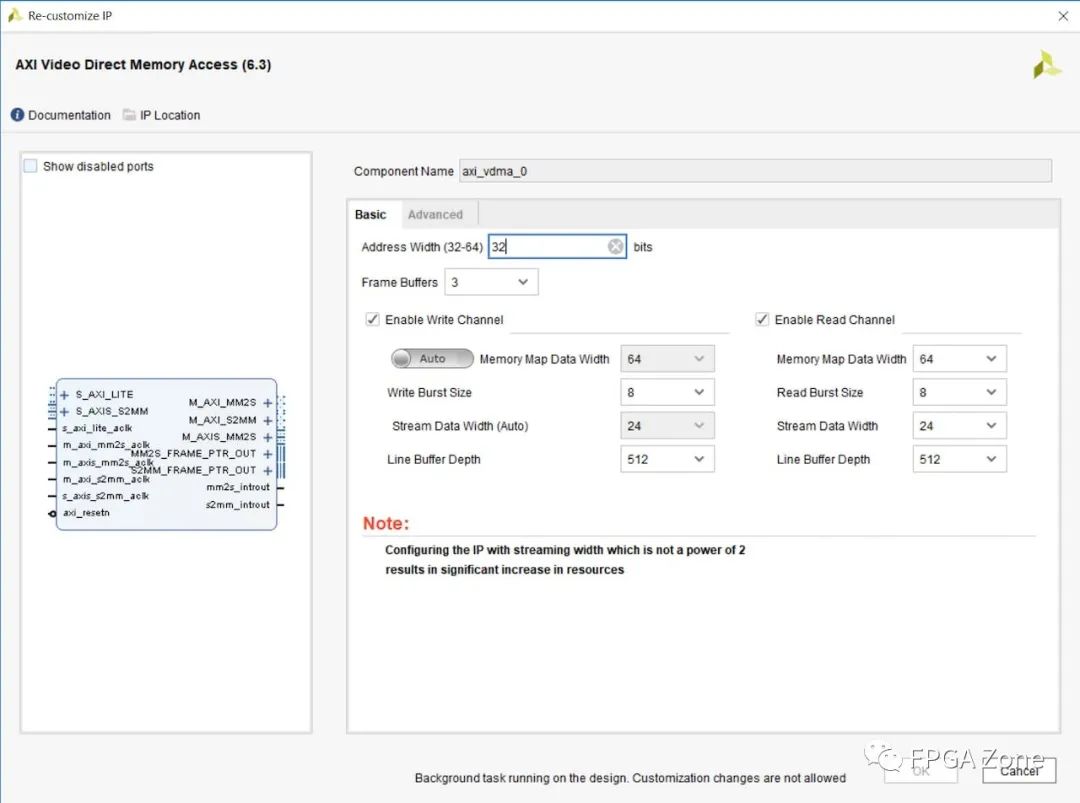

- VDMA ,配置如下:

圖6 配置VDMA IP

- VTC,視頻時序控制器配置如下:

圖7 配置VTC IP

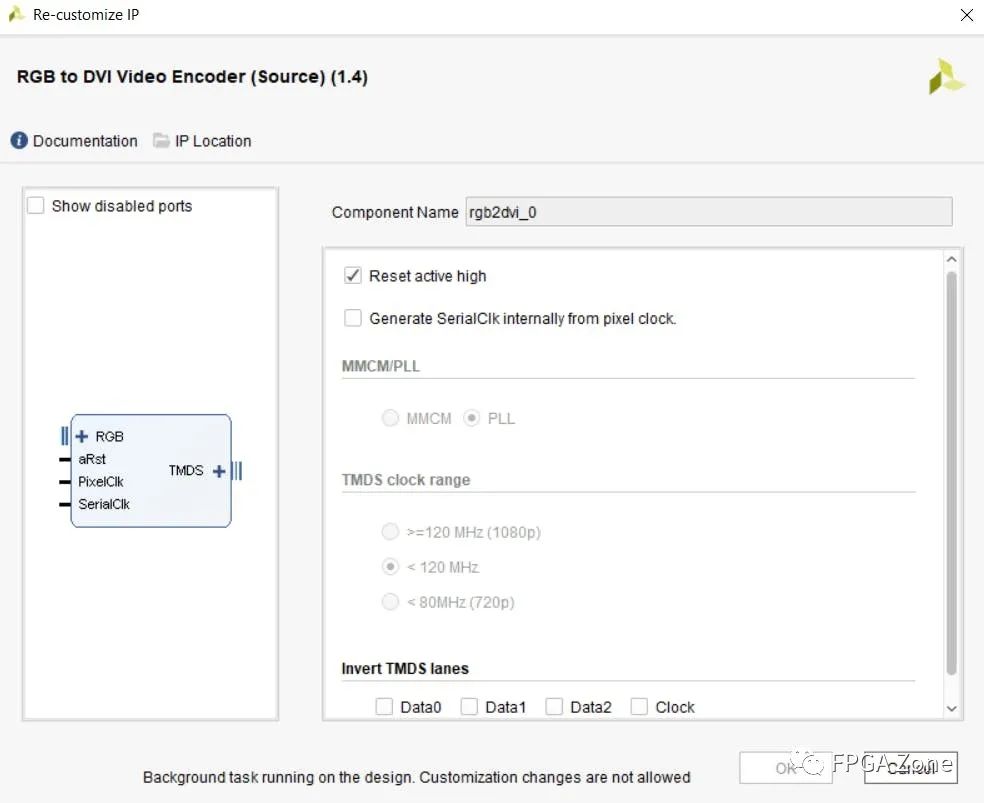

- RGB2DVI,用于將視頻流轉換為HDMI數據:

圖8 配置RGB2DVI IP

完整Vivado工程

將上述IP組合在一起,完整Vivado工程如下圖所示:

圖9 完整工程框圖

然后將上述工程導入Xilinx SDK中,以創建應用軟件。軟件里編寫以下程序:1. 檢測HDMI視頻信號,2. 配置視頻時序控制器,3. 配置VDMA從PS DDR讀出和寫入視頻數據。

最后,運行上述寫好的軟件,可以看到相機采集的視頻。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

HDMI

+關注

關注

32文章

1662瀏覽量

151653 -

圖像處理

+關注

關注

27文章

1281瀏覽量

56638 -

soc

+關注

關注

38文章

4120瀏覽量

217932 -

開發板

+關注

關注

25文章

4943瀏覽量

97191

發布評論請先 登錄

相關推薦

一文詳解FPGA的圖像處理技術

基于FPGA的LCoS驅動和圖像處理系統設計

實時圖像邊緣檢測的設計及FPGA實現

采用FPGA和通用DSP相結合實現視頻圖像采集系統的設計

基于ARM與FPGA的嵌入式實時圖像處理平臺

基于FPGA搭建一個通用的圖像處理平臺

基于FPGA搭建一個通用的圖像處理平臺

評論