近日,北京大學(xué)彭練矛院士/張志勇教授團(tuán)隊(duì)造出一款基于陣列碳納米管的 90nm 碳納米管晶體管,具備可以高度集成的能力。

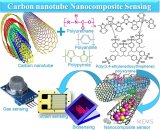

基于該90nm 碳納米管晶體管技術(shù),目前該團(tuán)隊(duì)研發(fā)的高靈敏碳納米管晶體管氫氣傳感器產(chǎn)品已經(jīng)上市,其探測限可以達(dá)到 0.5ppm,屬于最高端的氫氣傳感器產(chǎn)品,也是世界首款碳納米管芯片產(chǎn)品。

碳基電子技術(shù)將在未來 3 年左右用于傳感器芯片領(lǐng)域,以及在未來 5-8 年左右用于射頻芯片領(lǐng)域,并將在未來 15 年內(nèi)用于高端數(shù)字芯片領(lǐng)域。

圖 | 張志勇(來源:張志勇)

在 90nm 及以下技術(shù)節(jié)點(diǎn)的數(shù)字集成電路中,碳納米管半導(dǎo)體具備一定的應(yīng)用潛力,同時(shí)這也為進(jìn)一步探索全碳基集成電路提供了深入見解。

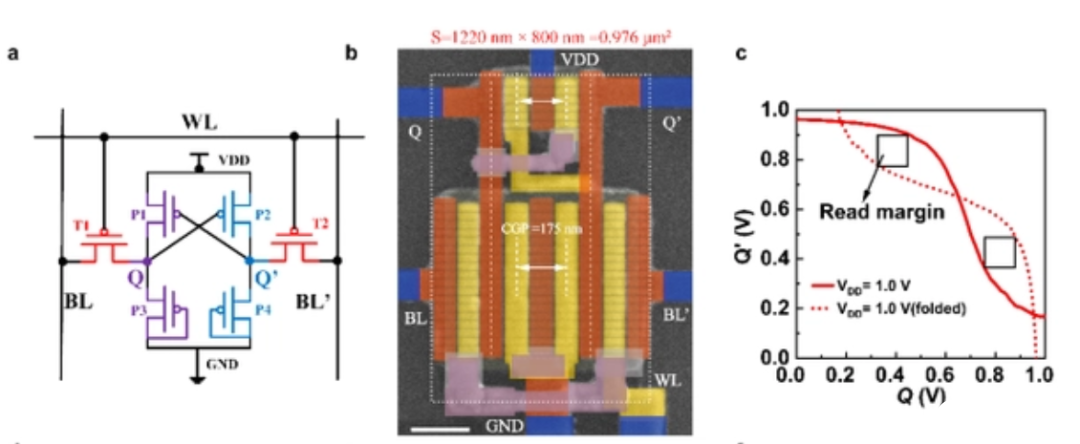

對(duì)于相關(guān)論文審稿人評(píng)價(jià)稱:“研究人員展示了面積小于 1 平方微米的 6 管 SRAM 單元,是新型集成電路技術(shù)的里程碑。”

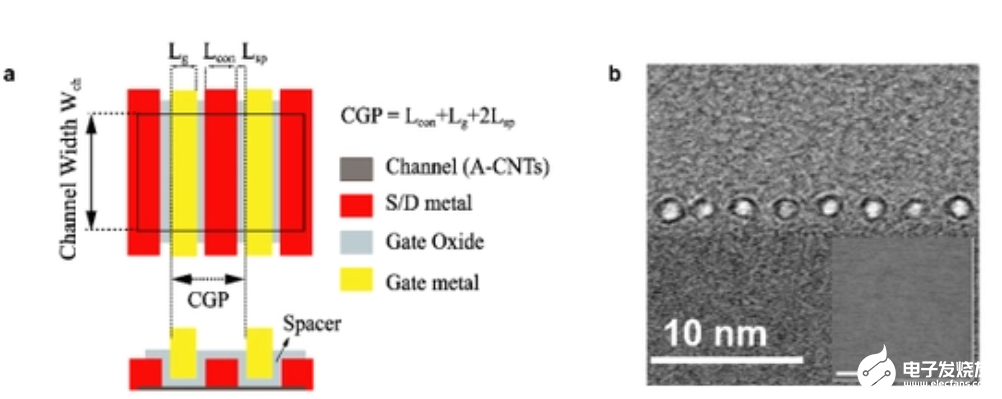

研究中,通過利用該團(tuán)隊(duì)此前研發(fā)的碳納米管陣列薄膜,以及借助縮減晶體管柵長和源漏接觸長度的手段,課題組制備出柵間距(CGP, contacted gate pitch)為 175nm 的碳納米管晶體管,其開態(tài)電流達(dá)到 2.24mA/μm、峰值跨導(dǎo) gm 為 1.64mS/μm。相比 45nm 的硅基商用節(jié)點(diǎn)器件,該晶體管的性能更高。

(來源:Nature Electronics)

基于此,該團(tuán)隊(duì)根據(jù)業(yè)界的集成度標(biāo)準(zhǔn),制備一款靜態(tài)隨機(jī)存取存儲(chǔ)器單元(SRAM,Static Random-Access Memory),其整體面積僅有 0.976 平方微米,包含 6 個(gè)晶體管(6T)。

在主流的數(shù)字集成電路技術(shù)中,SRAM 單元面積是衡量實(shí)際集成密度的重要參數(shù)。盡管大量研究都曾演示過碳納米管或低維半導(dǎo)體材料的 6T SRAM,但是它們的單元面積遠(yuǎn)遠(yuǎn)大于硅基 90nm 節(jié)點(diǎn)的 SRAM 單元,在集成度依然有待提高。

而該課題組首次采用非硅基的半導(dǎo)體材料,造出整體面積小于 1 平方微米的 6-T SRAM 電路,這表明碳基數(shù)字集成電路完全可以滿足 90nm 技術(shù)節(jié)點(diǎn)的集成度需求。

(來源:Nature Electronics)

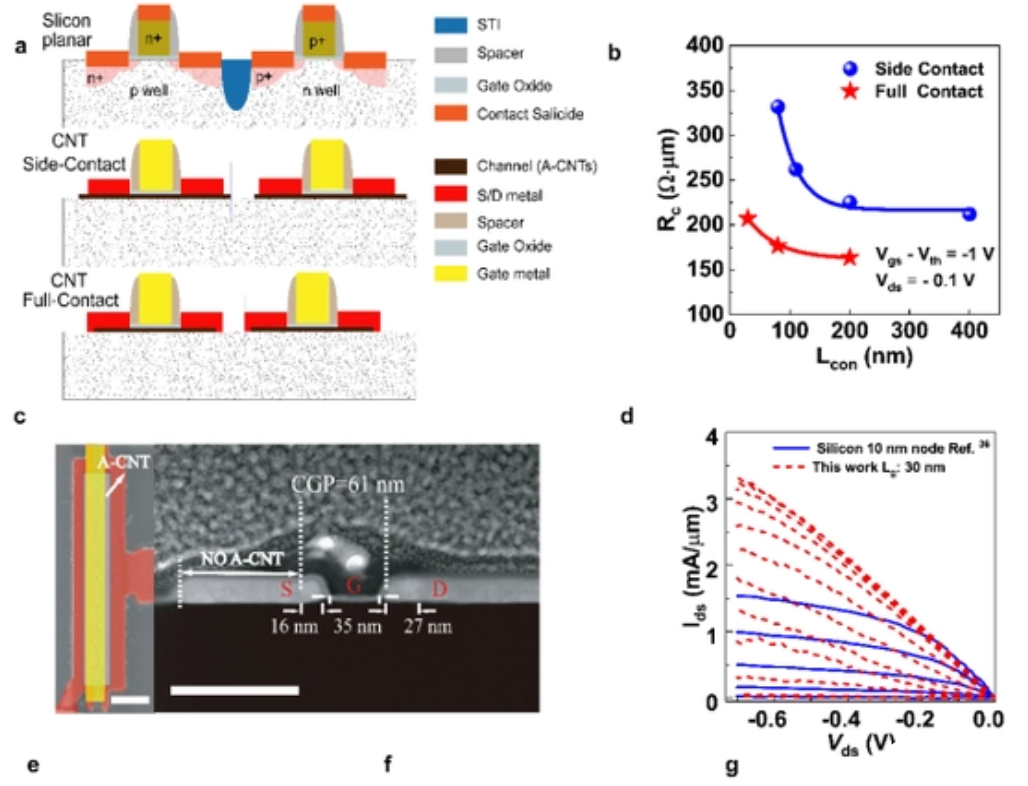

在此基礎(chǔ)之上,該團(tuán)隊(duì)進(jìn)一步探索了碳基晶體管縮減的可能性,證明按照嚴(yán)格的工業(yè)門標(biāo)準(zhǔn),完全可以將碳基晶體管縮減到亞 10nm 的技術(shù)節(jié)點(diǎn)。

考慮到低維半導(dǎo)體器件在接觸電阻的時(shí)候,會(huì)讓電阻隨著接觸長度的縮減而出現(xiàn)急劇增大,這會(huì)讓器件的整體尺寸無法縮減。

為此,課題組提出全接觸的結(jié)構(gòu),結(jié)合側(cè)面接觸和末端接觸的載流子注入機(jī)制,讓器件不僅表現(xiàn)出更低的接觸電阻,并能擁有更弱的接觸長度依賴性。

基于全接觸的結(jié)構(gòu),該團(tuán)隊(duì)嘗試將碳管晶體管 CGP 縮減至 55nm,這對(duì)應(yīng)著硅基晶體管中的 10nm 技術(shù)節(jié)點(diǎn)。與此同時(shí),這款碳管晶體管的性能卻優(yōu)于基于硅基的 10nm 節(jié)點(diǎn)的 PMOS 晶體管。

(來源:Nature Electronics)

本次成果同時(shí)展示了碳納米管晶體管在性能和集成度上的優(yōu)勢,結(jié)合其工藝簡單、低功耗以及適合單片三維集成的特點(diǎn),將讓碳納米管晶體管技術(shù)在高性能數(shù)字集成電路領(lǐng)域中發(fā)揮重大優(yōu)勢,從而成為一種通用的芯片平臺(tái)技術(shù),進(jìn)而有望用于高性能計(jì)算、人工智能、寬帶通信、智能傳感等領(lǐng)域。

據(jù)了解,集成電路的主要發(fā)展方式是通過縮減晶體管尺寸提高性能和集成度,同時(shí)降低功耗和制造成本。為了繼續(xù)推進(jìn)集成電路的發(fā)展,針對(duì)未來電子學(xué)的核心材料、器件結(jié)構(gòu)以及系統(tǒng)架構(gòu),學(xué)界和業(yè)界進(jìn)行了廣泛探索和深入研究。

其中,最受關(guān)注的方式是:采用超薄、高載流子遷移率的半導(dǎo)體,來構(gòu)建包括二維半導(dǎo)體材料、一維半導(dǎo)體納米線和碳納米管等 CMOS(Complementary Metal Oxide Semiconductor,互補(bǔ)金屬氧化物半導(dǎo)體)器件,這些器件比硅基晶體管具有更好的可縮減性和更高的性能。因此,一直以來人們使用這些器件來構(gòu)建納米晶體管。

目前,碳納米管晶體管已經(jīng)展現(xiàn)出超越商用硅基晶體管的潛力,在數(shù)字集成電路應(yīng)用中被寄予厚望。

然而,多數(shù)研究僅僅關(guān)注器件的柵長縮減,并未真正展現(xiàn)碳納米管晶體管在集成度上的潛力。而集成電路關(guān)注的主要技術(shù)指標(biāo)是多方面的,包括性能、功耗和集成度。

早在 2018 年初,張志勇就打算按照集成電路業(yè)界的技術(shù)節(jié)點(diǎn)發(fā)布標(biāo)準(zhǔn),研發(fā)基于 90nm 技術(shù)節(jié)點(diǎn)的碳納米管 CMOS 芯片工藝。

張志勇說:“為此,我先是考察了材料、設(shè)備、工藝技術(shù)的成熟度,然后物色和培養(yǎng)主攻這一方向的博士生林艷霞,耗時(shí)一年之久我培訓(xùn)了林艷霞在器件物理和工藝上的知識(shí)。”

后來,張志勇交給林艷霞一項(xiàng)目標(biāo):完成最小的晶體管和集成電路單元,并使用學(xué)校實(shí)驗(yàn)室的研究型設(shè)備,來完成使用業(yè)界頂級(jí)設(shè)備都難以完成的工藝。

這不僅要求林艷霞要對(duì)器件物理有著深入理解,還得具備精湛的實(shí)驗(yàn)技巧,最重要的是需要堅(jiān)韌的品質(zhì)。

后來,林艷霞整整做了五年。張志勇說:“中途又經(jīng)歷了新冠三年,實(shí)驗(yàn)斷斷續(xù)續(xù),她也多次瀕臨情緒奔潰。印象最深的是有兩次她哭著跟我抱怨:老師為什么把這么難的事讓我做?但她還是堅(jiān)持下來,完成了這項(xiàng)工作。”

最終,相關(guān)論文以《將對(duì)齊的碳納米管晶體管縮放到低于 10nm 節(jié)點(diǎn)》(Scaling aligned carbon nanotube transistors to a sub-10nm node)為題發(fā)在Nature Electronics[1]。

北京大學(xué)前沿交叉學(xué)科研究院博士生林艷霞和北京大學(xué)碳基電子學(xué)研究中心曹宇副研究員是共同一作,北京元芯碳基集成電路研究院、北京大學(xué)電子學(xué)院、碳基電子學(xué)研究中心彭練矛院士和張志勇教授擔(dān)任共同通訊作者。

圖丨相關(guān)論文(來源:Nature Electronics)

另據(jù)悉,目前該團(tuán)隊(duì)研發(fā)的高靈敏碳納米管晶體管氫氣傳感器產(chǎn)品已經(jīng)上市,其探測限可以達(dá)到 0.5ppm,屬于最高端的氫氣傳感器產(chǎn)品,也是世界首款碳納米管芯片產(chǎn)品。

相關(guān)的碳納米管生物傳感芯片也在研發(fā)中,預(yù)計(jì)近兩年將會(huì)推向市場,以用于食品安全、病毒檢測、慢病早篩、醫(yī)學(xué)診斷等領(lǐng)域。

不過,要想實(shí)現(xiàn)高性能的數(shù)字集成電路還需要 CMOS 晶體管的參與,而本次研究僅僅展示了 PMOS 晶體管的尺寸縮減、以及全 PMOS 的微縮電路,因此需要進(jìn)一步探索 NMOS(N-Metal-Oxide-Semiconductor,N 型金屬-氧化物-半導(dǎo)體)晶體管的縮減,借此展示 CMOS 電路的縮減能力,以及實(shí)現(xiàn) 6T CMOS 的靜態(tài)隨機(jī)存取存儲(chǔ)器。

相比 PMOS 晶體管,碳基 NMOS 晶體管的縮減面臨著更大的挑戰(zhàn)。主要原因在于 NMOS 器件的源漏接觸,采用比較活潑的金屬鈧,這很容易被氧化。

特別是縮減到比較細(xì)的線條時(shí),這會(huì)導(dǎo)致器件的接觸電阻劇增,進(jìn)而導(dǎo)致器件的性能迅速惡化,故很難在保持性能的前提下,將碳管 NMOS 晶體管的整體尺寸縮減到 200nm。

因此,課題組將通過采用特殊工藝,將碳管 NMOS 器件縮減到 10nm 及以下節(jié)點(diǎn),真正實(shí)現(xiàn)先進(jìn)技術(shù)節(jié)點(diǎn)的碳管 CMOS 工藝。

另外,目前該團(tuán)隊(duì)采用的工藝主要基于實(shí)驗(yàn)室,而非標(biāo)準(zhǔn)的工業(yè)化技術(shù)。比如,目前學(xué)界廣泛使用的剝離工藝, 根本無法滿足大規(guī)模集成電路的實(shí)際需求,因此需要換成業(yè)界標(biāo)準(zhǔn)的干法刻蝕工藝。

所以,課題組打算發(fā)展基于碳納米管 CMOS 晶體管的標(biāo)準(zhǔn)化工藝,推進(jìn)碳基芯片的工程化發(fā)展。

那么,目前碳納米管芯片處于怎樣的發(fā)展現(xiàn)狀?是否已經(jīng)或者預(yù)計(jì)何時(shí)可以投入商用?

張志勇表示:“我們?cè)谔蓟牧虾推骷苽漕I(lǐng)域掌握了核心技術(shù),并已初步打通材料、器件和芯片展示的主要環(huán)節(jié),具備面向未來的技術(shù)推進(jìn)能力和設(shè)備升級(jí)能力。”

結(jié)合傳統(tǒng)集成電路的加工、設(shè)計(jì)平臺(tái)和技術(shù),以及組織管理經(jīng)驗(yàn),該團(tuán)隊(duì)完全有可能在全球領(lǐng)域內(nèi)率先取得突破。

而隨著碳基電子技術(shù)的發(fā)展,也有望產(chǎn)生全新的芯片技術(shù)和新的產(chǎn)業(yè)鏈。從目前的技術(shù)發(fā)展趨勢來看,碳納米管芯片正處于工程化的迭代過程,未來即將形成完整的技術(shù)鏈條。

不過,要想造出能用于高端數(shù)字集成電路還需要一定的時(shí)間,因此可以采取“沿途下蛋”的方法。

具體來說,碳基電子技術(shù)將在未來 3 年左右用于傳感器芯片領(lǐng)域,以及在未來 5-8 年左右用于射頻芯片領(lǐng)域,并將在未來 15 年內(nèi)用于高端數(shù)字芯片領(lǐng)域。

到 2037 年,有望實(shí)現(xiàn)碳基 7nm 工藝(相當(dāng)于硅基 2/1nm 工藝),屆時(shí)將形成完整的碳基電子產(chǎn)業(yè)生態(tài),碳基芯片也將被真正用于主流高性能邏輯芯片領(lǐng)域,從而讓碳基電子技術(shù)全面超越傳統(tǒng)半導(dǎo)體技術(shù)。

最后,張志勇表示:“未來已來,碳納米管芯片即將走出學(xué)術(shù)期刊,走進(jìn)我們的生活。”

來源:DeepTech深科技

-

傳感器

+關(guān)注

關(guān)注

2548文章

50740瀏覽量

752148 -

碳納米管

+關(guān)注

關(guān)注

1文章

144瀏覽量

17258 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

氫氣傳感器

+關(guān)注

關(guān)注

1文章

25瀏覽量

9051 -

90nm

+關(guān)注

關(guān)注

0文章

4瀏覽量

10905

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶體管溫度傳感器有什么特點(diǎn)

晶體管反相器的原理及應(yīng)用

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

LMT90 小外形尺寸晶體管封裝(SOT)-23 單電源攝氏溫度傳感器數(shù)據(jù)表

金銀納米顆粒對(duì)單壁碳納米管實(shí)現(xiàn)近紅外熒光增強(qiáng)

如何提高晶體管的開關(guān)速度,讓晶體管快如閃電

什么是達(dá)林頓晶體管?達(dá)林頓晶體管的基本電路

碳納米管納米復(fù)合傳感器的研究進(jìn)展綜述

有什么方法可以提高晶體管的開關(guān)速度呢?

碳納米管晶體管兼容已有半導(dǎo)體制程工藝,解決碳納米管均勻可控?fù)诫s難題

可性能翻倍的新型納米片晶體管

晶體管是怎么做得越來越小的?

北大團(tuán)隊(duì)打造世界首款90nm碳納米管晶體管氫氣傳感器

北大團(tuán)隊(duì)打造世界首款90nm碳納米管晶體管氫氣傳感器

評(píng)論