1、引言

隨著技術的發展,移動電子設備已成為我們生活和文化的重要組成部分。平板電腦和智能手機觸摸技術的應用,讓我們能夠與這些設備進行更多的互動。它構成了一個完整的靜電放電 (ESD) 危險環境,即人體皮膚對設備產生的靜電放電。

例如,在使用消費類電子設備時,在用戶手指和平板電腦 USB 或者 HDMI 接口之間會發生 ESD,從而對平板電腦產生不可逆的損壞,例如:峰值待機電流或者永久性系統失效。

本文將為您解釋系統級 ESD 現象和器件級 ESD 現象之間的差異,并向您介紹一些提供 ESD 事件保護的系統級設計方法。

2、系統級ESD保護與器件級ESD保護的對比

IC 的 ESD 損壞可發生在任何時候,從裝配到板級焊接,再到終端用戶人機互動。ESD 相關損壞最早可追溯到半導體發展之初,但在 20 世紀 70 年代微芯片和薄柵氧化 FET 應用于高集成 IC 以后,它才成為一個普遍的問題。

所有 IC 都有一些嵌入式器件級 ESD 結構,用于在制造階段保護 IC 免受 ESD 事件的損壞。

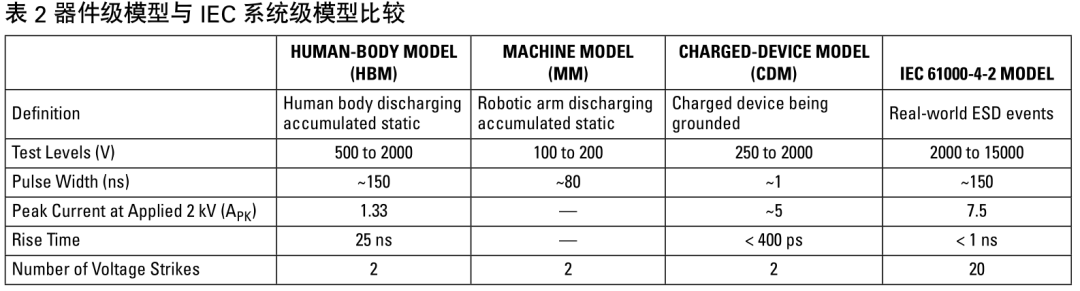

這些事件可由三個不同的器件級模型進行模擬:人體模型 (HBM)、機器模型 (MM) 和帶電器件模型(CDM)。

HBM 用于模擬用戶操作引起的 ESD 事件,MM 用于模擬自動操作引起的 ESD 事件,而 CDM則模擬產品充電/放電所引起的 ESD 事件。這些模型都用于制造環境下的測試。在這種環境下,裝配、最終測試和板級焊接工作均在受控 ESD 環境下完成,從而減小暴露器件所承受的 ESD 應力。在制造環境下,IC 一般僅能承受** 2-kV** HBM 的 ESD 電擊,而最近出臺的小型器件靜電規定更是低至 500V。

盡管在廠房受控 ESD 環境下器件級模型通常已足夠,但在系統級測試中它們卻差得很遠。在終端用戶環境下,電壓和電流的ESD電擊強度要高得多。

因此,工業環境使用另一種方法進行系統級 ESD 測試,其由IEC 61000-4-2 標準定義。器件級 HBM、MM和CDM 測試的目的都是保證 IC 在制造過程中不受損壞;IEC 61000-4-2規定的系統級測試用于模擬現實世界中的終端用戶ESD事件。

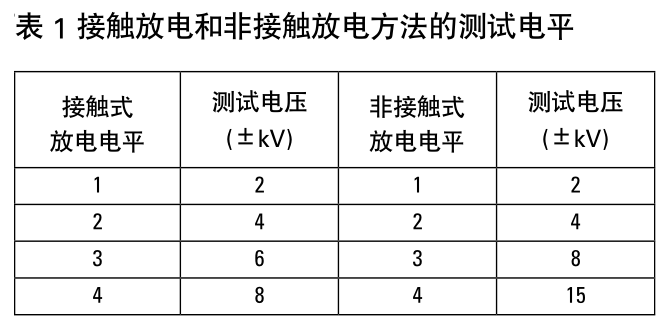

IEC 規定了兩種系統級測試:接觸放電和非接觸放電。使用接觸放電方法時,測試模擬器電極與受測器件(DUT) 保持接觸。非接觸放電時,模擬器的帶電電極靠近 DUT,同 DUT 之間產生的火花促使放電。

表 1 列出了 IEC 61000-4-2 標準規定的每種方法的測試級別范圍。請注意,兩種方法的每種測試級別的放電強度并不相同。我們通常在4級(每種方法的最高官方標稱級別)以上對應力水平進行逐級測試,直到發生故障點為止。

器件級模型和系統級模型有一些明顯的區別,表 2 列出了這些區別。

表 2 中最后三個參數(電流、上升時間和電擊次數)需特別注意:

a、電流差對于 ESD 敏感型器件是否能夠承受一次 ESD 事件至關重要。由于強電流可引起結點損壞和柵氧化損壞,8-kV HBM 保護芯片(峰值電流5.33A)可能會因 2-kV IEC 模型電擊(峰值電流7.5A)而損壞。因此,系統設計人員不能把 HBM 額定值同 IEC 模型額定值混淆,這一點極為重要。

b、另一個差異存在于電壓尖峰上升時間。HBM 的規定上升時間為 25ns。IEC 模型脈沖上升時間小于1ns,其在最初 3ns 消耗掉大部分能量。如果 HBM 額定的器件需 25ns 來做出響應,則在其保護電路激活以前器件就已被損壞。

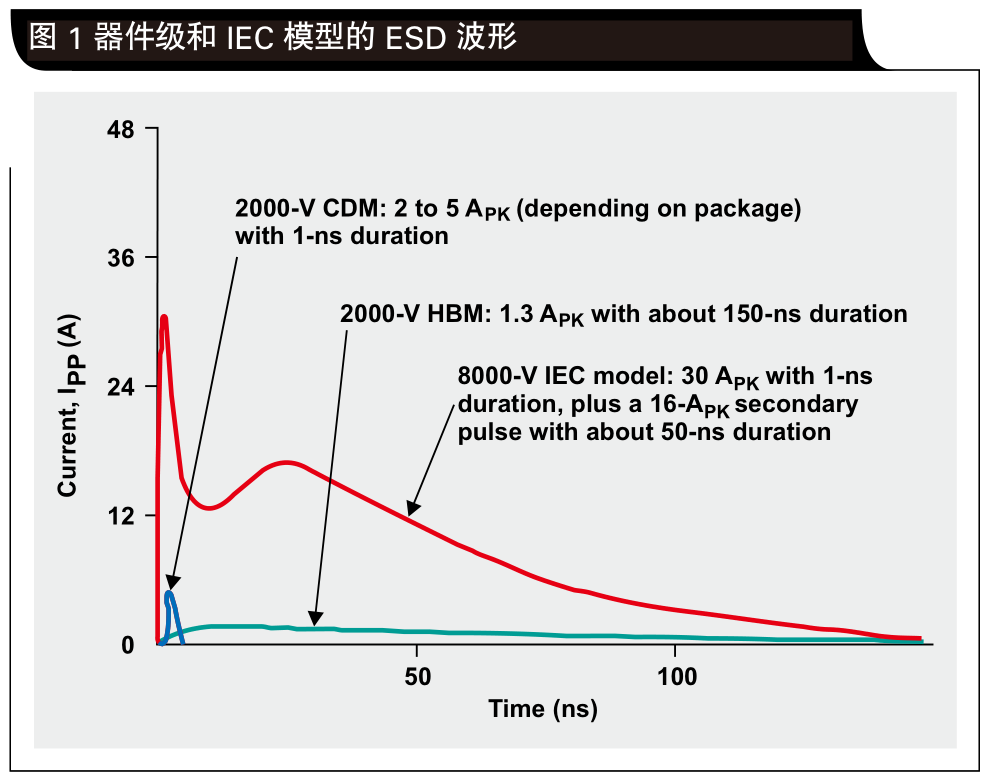

c、兩種模型在測試期間所用的電擊次數不同。HBM僅要求測試一次正電擊和一次負電擊,而 IEC 模型卻要求 10 次正電擊和 10 次負電擊。可能出現的情況是,器件能夠承受第一次電擊,但由于初次電擊帶來的損壞仍然存在,其會在后續電擊中失效。圖 1 顯示了 CDM、HBM 和 IEC 模型的 ESD 波形舉例。很明顯,相比所有器件級模型的脈沖,IEC 模型的脈沖攜帶了更多的能量。

3、TVS 如何保護系統免受 ESD 事件的損害

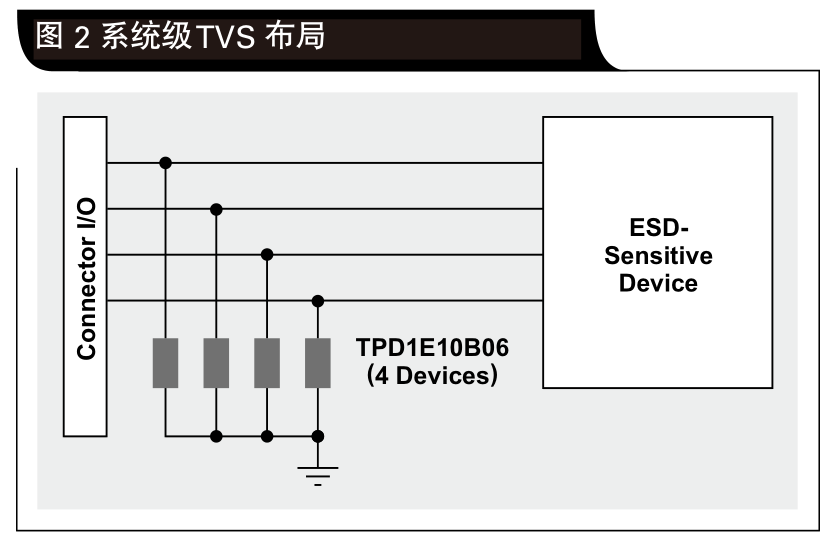

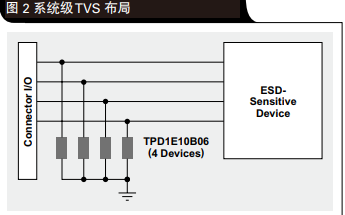

與 ESD 保護集成結構不同,IEC 61000-4-2 標準規定的模型通常會使用離散式獨立瞬態電壓抑制二極管,也即瞬態電壓抑制器 (TVS)。相比電源管理或者微控制器單元中集成的 ESD 保護結構,獨立 TVS 成本更低,并且可以靠近系統 I/O 連接器放置,如圖 2 所示。

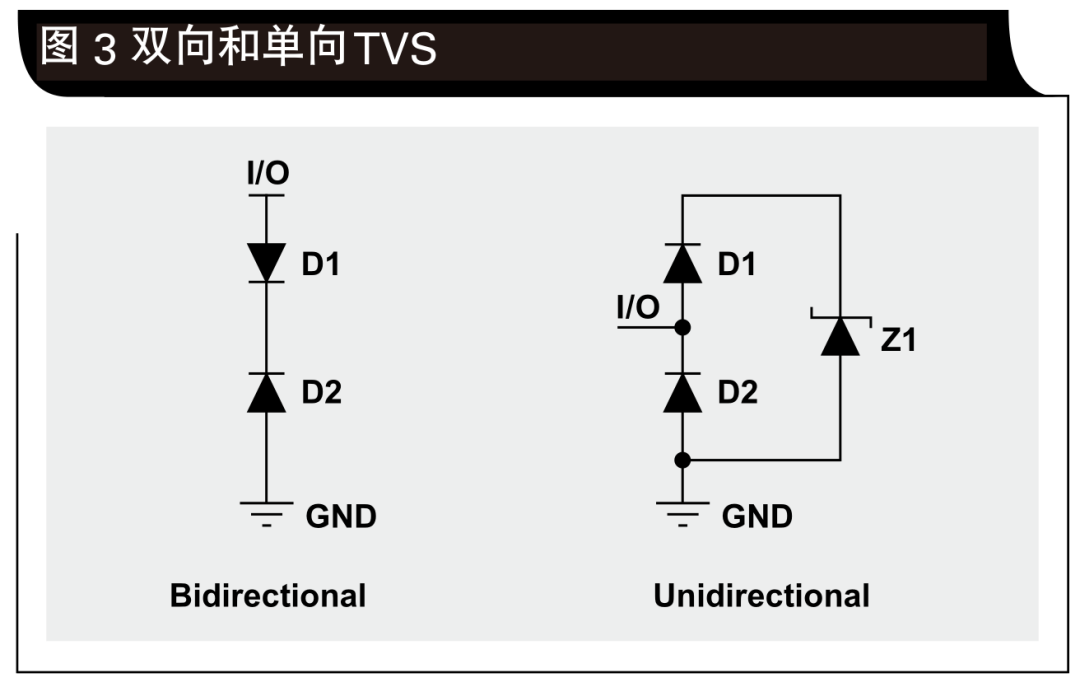

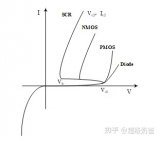

共有兩種 TVS:雙向和單向(參見圖 3)。TI TPD1E10B06 便是一個雙向 TVS例子,它可以放置在一條通用數據線路上,用于系統級 ESD 保護。

正常工作狀態下,雙向和單向 TVS 都為一個開路,并在 ESD 事件發生時接地。在雙向 TVS 情況下,只要 D1 和 D2 都不進入其擊穿區域,I/O 線路電壓信號會在接地電壓上下擺動。

當 ESD 電擊(正或者負)擊中 I/O 線路時,一個二極管變為正向偏置,而另一個擊穿,從而形成一條通路,ESD 能量立即沿這條通路接地。在單向 TVS 情況下,只要 D2 和 Z1 都不進入其擊穿區域,則電壓信號會在接地電壓以上擺動。

當正ESD電擊擊中I/O線路時,D1變為正向偏置,而Z1 先于 D2進入其擊穿區域;通過 D1 和 Z1 形成一條接地通路,從而讓 ESD 能量得到耗散。

當發生負 ESD 事件時,D2 變為正向偏置,ESD能量通過 D2接地通路得到耗散。由于 D1 和 D2 尺寸可以更小、寄生電容更少,單向二極管可用于許多高速應用;D1 和 D2 可以“隱藏”更大的齊納二極管 Z1(大尺寸的原因是處理擊穿區域更多的電流)。

4、系統級 ESD 保護的關鍵器件參數

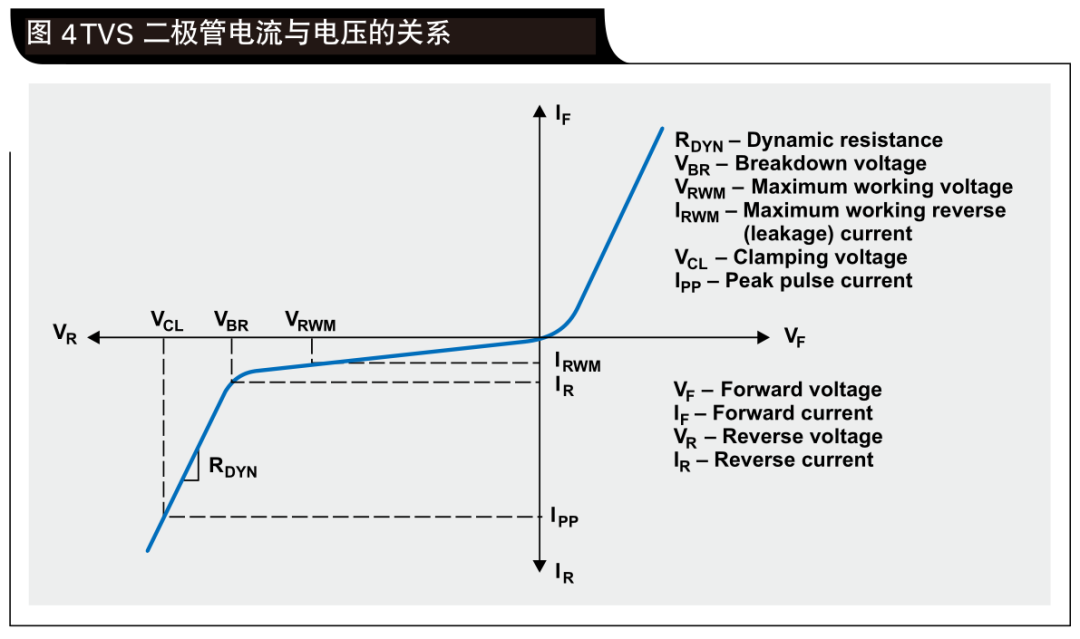

圖 4 顯示了 TVS 二極管電流與電壓特性的對比情況。盡管 TVS 是一種簡單的結構,但是在系統級 ESD 保護設計過程中仍然需要注意幾個重要的參數。

這些參數包括擊穿電壓 VBR、動態電阻 RDYN、鉗位電壓VCL 和電容。

4.1、擊穿電壓VBR

正確選擇 TVS 的第一步是研究擊穿電壓 (VBR)。

例如,如果受保護 I/O 線路的最大工作電壓 VRWM 為5V,則在達到該最大電壓以前 TVS 不應進入其擊穿區域。通常,TVS 產品說明書會包括具體漏電流的VRWM,它讓我們能夠更加容易地選擇正確的 TVS。否則,我們可以選擇一個 VBR(min) 大于受保護I/O 線路 VRWM 幾伏的 TVS。

4.2、動態電阻

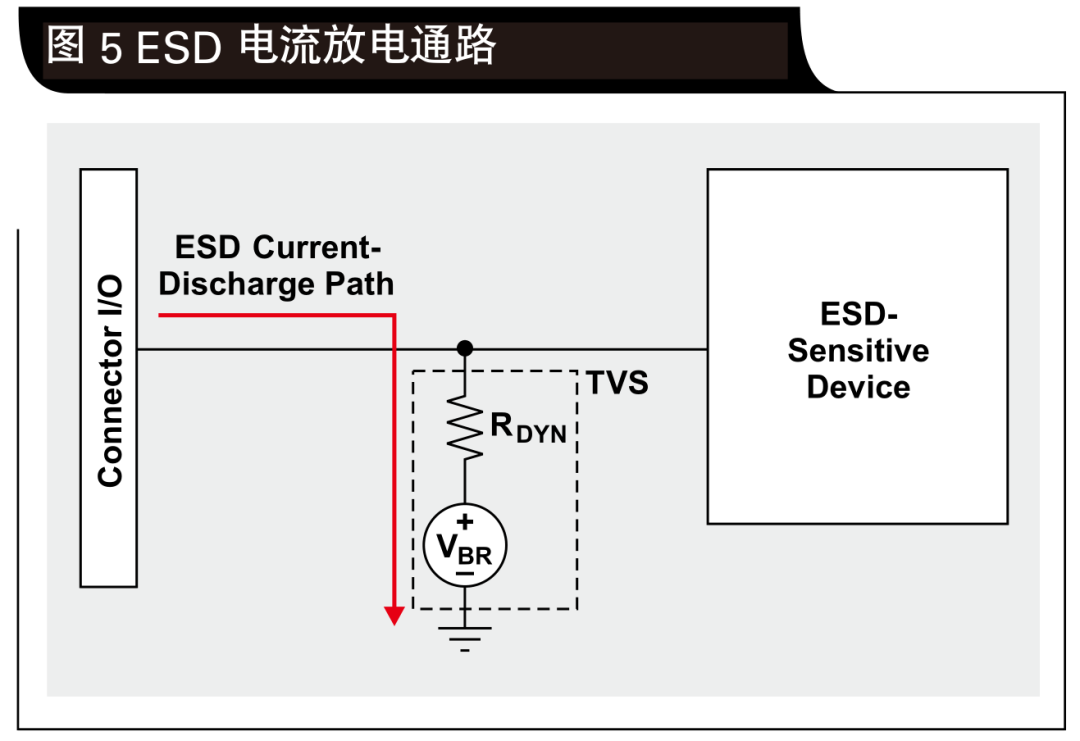

ESD 是一種極速事件,也就是幾納秒的事情。在如此短的時間內,TVS 傳導接地通路不會立即建立起來,并且在通路中存在一定的電阻。這種電阻被稱作動態電阻 (RDYN),如圖 5 所示。

理想情況下,RDYN 應為零,這樣 I/O 線路電壓才能盡可能地接近 VBR;但是,這是不可能的事情。

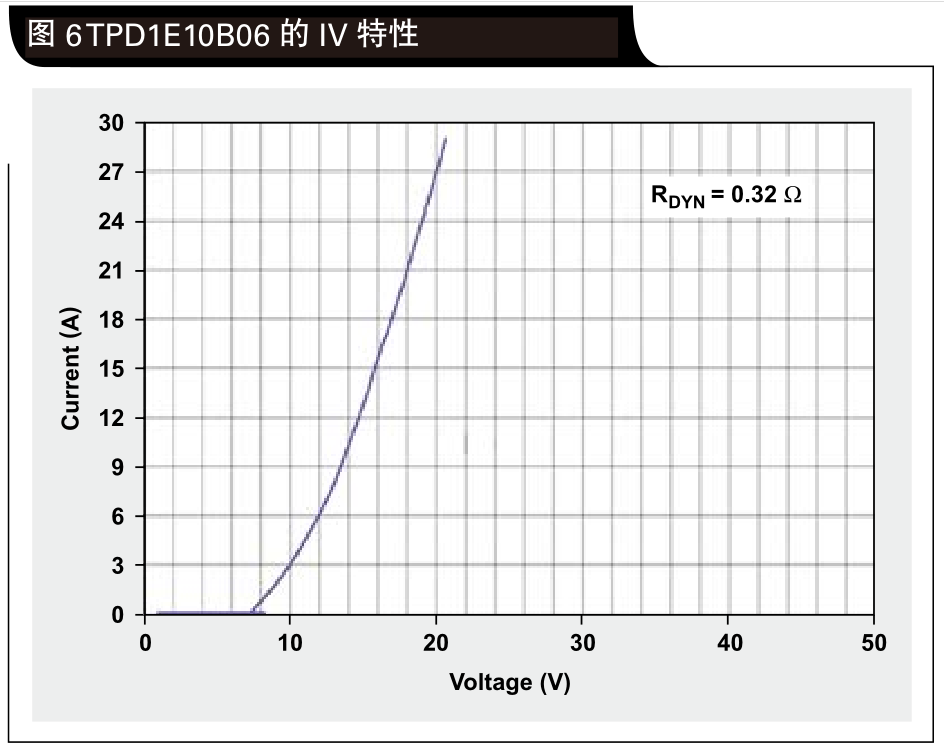

RDYN 的最新工業標準值為 1 ? 或者 1 ? 以下。利用傳輸線路脈沖測量技術可以得到 RDYN。使用這種技術時,通過 TVS 釋放電壓,然后測量相應的電流。在得到不同電壓的許多數據點以后,便可以繪制出如圖6一樣的 IV 曲線,而斜線便為 RDYN。圖 6 顯示了 TPD1E10B06 的 RDYN,其典型值為 ~0.3 ?。

4.3、鉗位電壓

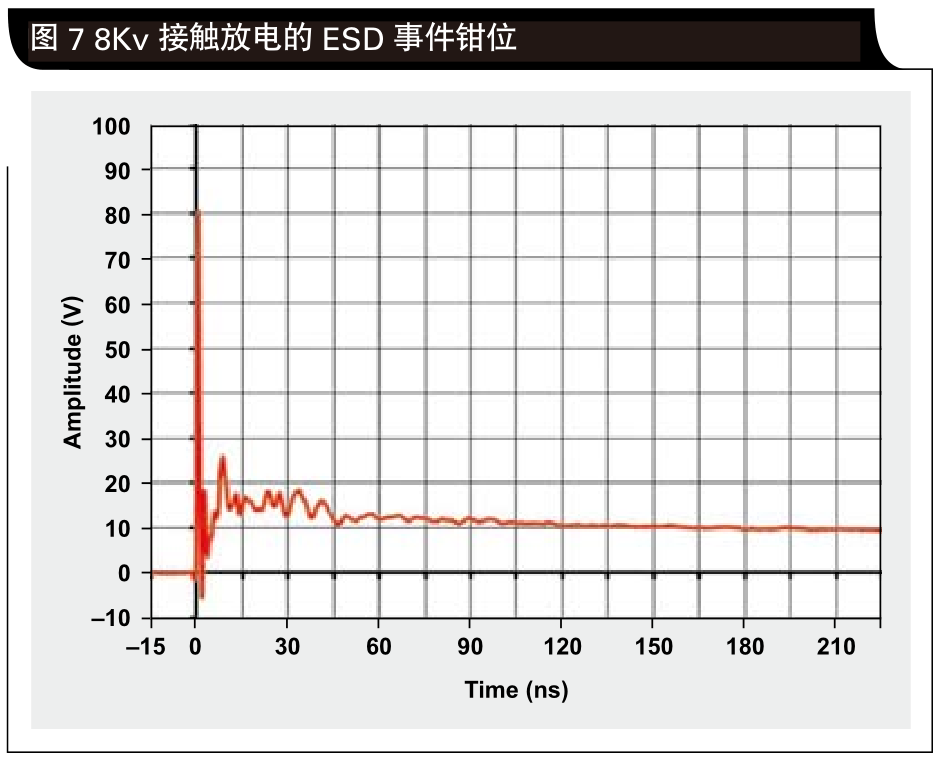

由于ESD是一種極速瞬態事件,I/O 線路的電壓不能立即得到箝制。如圖 7 所示,根據 IEC 61000-4-2 標準,數千伏電壓被箝制為數十伏。

如方程式 1 所示,RDYN 越小,鉗位性能也就越好:

其中,IPP 為 ESD 事件期間的峰值脈沖電流,而 Iparasitic 為通過 TVS 接地來自連接器的線路寄生電感。

把鉗位電壓波形下面的區域想像成能量。鉗位性能越好,受保護ESD敏感型器件在ESD事件中受到損壞的機率也就越小。由于鉗位電壓很小,一些TVS可承受IEC模型的8kV接觸式放電,但是“受保護”器件卻被損壞了。

電容

在正常工作狀態下,TVS為一個開路,并具有寄生電容分流接地。設計人員應在信號鏈帶寬預算中考慮到這種電容。

結論

由于 IC 工藝技術節點變得越來越小,它也越來越容易受到 ESD 損壞的影響,不管是在制造過程還是在終端用戶使用環境下。器件級 ESD 保護并不足以在系統層面為 IC 提供保護。我們應在系統級設計中使用獨立 TVS。在選擇某個 TVS 時,設計人員應注意一些重要參數,例如:VBR、RDYN、VCL 和電容等。

審核編輯:湯梓紅

-

ESD

+關注

關注

48文章

2012瀏覽量

172790 -

嵌入式

+關注

關注

5070文章

19024瀏覽量

303468 -

TVS

+關注

關注

8文章

775瀏覽量

60516 -

靜電放電

+關注

關注

3文章

284瀏覽量

44620

原文標題:系統級ESD設計考慮[20230905]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

系統級ESD保護與器件級ESD保護的對比 系統級ESD保護的關鍵器件參數

系統級ESD保護與器件級ESD保護的對比 系統級ESD保護的關鍵器件參數

評論