PCB布局設(shè)計檢視要素

布局的DFM要求

1 已確定優(yōu)選工藝路線,所有器件已放置板面。

2 坐標(biāo)原點為板框左、下延伸線交點,或者左下邊插座的左下焊盤。

3 PCB實際尺寸、定位器件位置等與工藝結(jié)構(gòu)要素圖吻合,有限制器件高度要求的區(qū)域的器件布局滿足結(jié)構(gòu)要素圖要求。

4 撥碼開關(guān)、復(fù)位器件,指示燈等位置合適,拉手條與其周圍器件不產(chǎn)生位置干涉。

5 板外框平滑弧度197mil,或者按結(jié)構(gòu)尺寸圖設(shè)計。

6 普通板有200mil工藝邊;背板左右兩邊留有工藝邊大于400mil,上下兩邊留有工藝邊大于680mil。器件擺放與開窗位置不沖突。

7 各種需加的附加孔(ICT定位孔125mil、拉手條孔、橢圓孔及光纖支架孔)無遺漏,且設(shè)置正確。

8 過波峰焊加工的器件pin間距、器件方向、器件間距、器件庫等考慮到波峰焊加工的要求。

9 器件布局間距符合裝配要求:表面貼裝器件大于20mil、IC大于80mil、BGA大于200mil。

10 壓接件在元件面距高于它的器件大于120mil,焊接面壓接件貫通區(qū)域無任何器件。

11 高器件之間無矮小器件,且高度大于10mm的器件之間5mm內(nèi)未放置貼片器件和矮、小的插裝器件。

12 極性器件有極性絲印標(biāo)識。同類型有極性插裝元器件X、Y向各自方向相同。

13 所有器件有明確標(biāo)識,沒有P*,REF等不明確標(biāo)識。

14 含貼片器件的面有3個定位光標(biāo),呈"L"狀放置。定位光標(biāo)中心離板邊緣距離大于240mil。

15 如需做拼板處理,布局考慮到便于拼版,便于PCB加工與裝配。

16 有缺口的板邊(異形邊)應(yīng)使用銑槽和郵票孔的方式補齊。郵票孔為非金屬化空,一般為直徑40mil,邊緣距16mil。

17 用于調(diào)試的測試點在原理圖中已增加,布局中位置擺放合適。

布局的熱設(shè)計要求

18 發(fā)熱元件及外殼裸露器件不緊鄰導(dǎo)線和熱敏元件,其他器件也應(yīng)適當(dāng)遠離。

19 散熱器放置考慮到對流問題,散熱器投影區(qū)域內(nèi)無高器件干涉,并用絲印在安裝面做了范圍標(biāo)示。

20 布局考慮到散熱通道的合理順暢。

21 電解電容適當(dāng)離開高熱器件。

22 考慮到大功率器件和扣板下器件的散熱問題。

布局的信號完整性要求

23 始端匹配靠近發(fā)端器件,終端匹配靠近接收端器件。

24 退耦電容靠近相關(guān)器件放置

25 晶體、晶振及時鐘驅(qū)動芯片等靠近相關(guān)器件放置。

26 高速與低速,數(shù)字與模擬按模塊分開布局。

27 根據(jù)分析仿真結(jié)果或已有經(jīng)驗確定總線的拓?fù)浣Y(jié)構(gòu),確保滿足系統(tǒng)要求。

28 若為改板設(shè)計,結(jié)合測試報告中反映的信號完整性問題進行仿真并給出解決方案。

29 對同步時鐘總線系統(tǒng)的布局滿足時序要求。

EMC要求

30 電感、繼電器和變壓器等易發(fā)生磁場耦合的感性器件不相互靠近放置。有多個電感線圈時,方向垂直,不耦合。

31 為避免單板焊接面器件與相鄰單板間發(fā)生電磁干擾,單板焊接面不放置敏感器件和強輻射器件。

32 接口器件靠近板邊放置,已采取適當(dāng)?shù)腅MC防護措施(如帶屏蔽殼、電源地挖空等措施),提高設(shè)計的EMC能力。

33 保護電路放在接口電路附近,遵循先防護后濾波原則。麥斯艾姆(massembly)貼片知識課堂,用通俗的文字介紹專業(yè)貼片知識。麥斯艾姆科技,全國首家PCB(麥斯艾姆知識課堂)樣板打板,元器件代采購,及貼片的一站式服務(wù)提供者!

34 發(fā)射功率很大或特別敏感的器件(例如晶振、晶體等)距屏蔽體、屏蔽罩外殼500mil以上。

35 復(fù)位開關(guān)的復(fù)位線附近放置了一個0.1uF電容,復(fù)位器件、復(fù)位信號遠離其他強*件、信號。

層設(shè)置與電源地分割要求

37 兩信號層直接相鄰時須定義垂直布線規(guī)則。

38 主電源層盡可能與其對應(yīng)地層相鄰,電源層滿足20H規(guī)則。

39 每個布線層有一個完整的參考平面。

40 多層板層疊、芯材(CORE)對稱,防止銅皮密度分布不均勻、介質(zhì)厚度不對稱產(chǎn)生翹曲。

41 板厚不超過4.5mm,對于板厚大于2.5mm(背板大于3mm)的應(yīng)已經(jīng)工藝人員確認(rèn)PCB加工、裝配、裝備無問題,PC卡板厚為1.6mm。

42 過孔的厚徑比大于10:1時得到PCB廠家確認(rèn)。

43 光模塊的電源、地與其它電源、地分開,以減少干擾。

44 關(guān)鍵器件的電源、地處理滿足要求。

45 有阻抗控制要求時,層設(shè)置參數(shù)滿足要求。

電源模塊要求

46 電源部分的布局保證輸入輸出線的順暢、不交叉。

47 單板向扣板供電時,已在單板的電源出口及扣板的電源入口處,就近放置相應(yīng)的濾波電路。

其他方面的要求

48 布局考慮到總體走線的順暢,主要數(shù)據(jù)流向合理。

49 根據(jù)布局結(jié)果調(diào)整排阻、FPGA、EPLD、總線驅(qū)動等器件的管腳分配以使布線最優(yōu)化。

50 布局考慮到適當(dāng)增大密集走線處的空間,以避免不能布通的情況。

51 如采取特殊材料、特殊器件(如0.5mmBGA等)、特殊工藝,已經(jīng)充分考慮到到貨期限、可加工性,且得到PCB廠家、工藝人員的確認(rèn)。

52 扣板連接器的管腳對應(yīng)關(guān)系已得到確認(rèn),以防止扣板連接器方向、方位搞反。

53 如有ICT測試要求,布局時考慮到ICT測試點添加的可行性,以免布線階段添加測試點困難。

54 含有高速光模塊時,布局優(yōu)先考慮光口收發(fā)電路。

55 布局完成后已提供1:1裝配圖供項目人對照器件實體核對器件封裝選擇是否正確。

56 開窗處已考慮內(nèi)層平面成內(nèi)縮,并已設(shè)置合適的禁止布線區(qū)。

PCB LAYOUT三種特殊走線技巧

今天小編從直角走線,差分走線,蛇形線三個方面闡述PCB LAYOUT的走線技巧:

一、直角走線 (三個方面)

直角走線的對信號的影響就是主要體現(xiàn)在三個方面:一是拐角可以等效為傳輸線上的容性負(fù)載,減緩上升時間;二是阻抗不連續(xù)會造成信號的反射;三是直角尖端產(chǎn)生的EMI,到10GHz以上的RF設(shè)計領(lǐng)域,這些小小的直角都可能成為高速問題的重點對象。

二、差分走線 (“等長、等距、參考平面”)

何為差分信號(Differential Signal)?通俗地說就是驅(qū)動端發(fā)送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態(tài)“0”還是“1”。而承載差分信號的那一對走線就稱為差分走線。差分信號和普通的單端信號走線相比,最明顯的優(yōu)勢體現(xiàn)在以下三方面:

1、抗干擾能力強,因為兩根差分走線之間的耦合很好,當(dāng)外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關(guān)心的只是兩信號的差值,所以外界的共模噪聲可被完全抵消。

2、能有效抑制EMI,同樣的道理,由于兩根信號的極性相反,他們對外輻射的電磁場可以相互抵消,耦合的越緊密,泄放到外界的電磁能量越少。

3、時序定位精確,由于差分信號的開關(guān)變化是位于兩個信號的交點,而不像普通單端信號依靠高低兩個閾值電壓判斷,因而受工藝,溫度的影響小,能降低時序上的誤差,同時也更適合于低幅度信號的電路。目前流行的LVDS(low voltage differential signaling)就是指這種小振幅差分信號技術(shù)。

三、蛇形線 (調(diào)節(jié)延時)

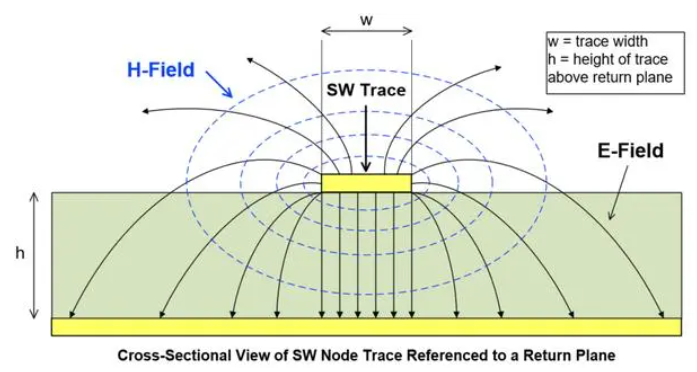

蛇形線是Layout中經(jīng)常使用的一類走線方式。其主要目的就是為了調(diào)節(jié)延時,滿足系統(tǒng)時序設(shè)計要求。其中最關(guān)鍵的兩個參數(shù)就是平行耦合長度(Lp)和耦合距離(S),很明顯,信號在蛇形走線上傳輸時,相互平行的線段之間會發(fā)生耦合,呈差模形式,S越小,Lp越大,則耦合程度也越大。可能會導(dǎo)致傳輸延時減小,以及由于串?dāng)_而大大降低信號的質(zhì)量,其機理可以參考對共模和差模串?dāng)_的分析。下面是給Layout工程師處理蛇形線時的幾點建議:

1、盡量增加平行線段的距離(S),至少大于3H,H指信號走線到參考平面的距離。通俗的說就是繞大彎走線,只要S足夠大,就幾乎能完全避免相互的耦合效應(yīng)。

2、減小耦合長度Lp,當(dāng)兩倍的Lp延時接近或超過信號上升時間時,產(chǎn)生的串?dāng)_將達到飽和。

3、帶狀線(Strip-Line)或者埋式微帶線(Embedded Micro-strip)的蛇形線引起的信號傳輸延時小于微帶走線(Micro-strip)。理論上,帶狀線不會因為差模串?dāng)_影響傳輸速率。

4、高速以及對時序要求較為嚴(yán)格的信號線,盡量不要走蛇形線,尤其不能在小范圍內(nèi)蜿蜒走線。

5、可以經(jīng)常采用任意角度的蛇形走線,能有效的減少相互間的耦合。

6、高速PCB設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。

7、有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

PCB技術(shù)中的電磁的兼容性

電磁兼容性(EMC, Electromagnetic Compatibility)是指電子設(shè)備在各種電磁環(huán)境中仍能夠協(xié)調(diào)、有效地進行工作的能力。電磁兼容性設(shè)計的目的是使電子設(shè)備既能抑制各種外來的干擾,使電子設(shè)備在特定的電磁環(huán)境中能夠正常工作,同時又能減少電子設(shè)備本身對其它電子設(shè)備的電磁干擾。印刷電路板(PCB)設(shè)計中的電磁兼容性涉及多方面因數(shù),以下主要從三大部分加以闡述,具體選擇要綜合各方面因數(shù)。

一 印刷電路板整體布局及器件布置

1.一個產(chǎn)品的成功與否,一是要注重內(nèi)在質(zhì)量,二是兼顧整體的美觀,兩者都較完美才能認(rèn)為該產(chǎn)品是成功的;在一個PCB板上,元件的布局要求要均衡,疏密有序,不能頭重腳輕或一頭沉,過孔要盡量少;電路板的最佳形狀為矩形。長寬比為3:2或4:3;4 層板比雙面板噪聲低20dB.6層板比4層板噪聲低10dB.經(jīng)濟條件允許時盡量用多層板。

2.電路板一般分模擬電路區(qū)(怕干擾),數(shù)字電路區(qū)(怕干擾、又產(chǎn)生干擾),功率驅(qū)動區(qū)(干擾源),故步板時要合理地分成三區(qū)。

3.器件一般選擇功耗低,穩(wěn)定性好的器件,而且盡量少用高速器件。

4.線條有講究:有條件做寬的線決不做細(xì);高壓及高頻線應(yīng)園滑,不得有尖銳的倒角,拐彎也不得采用直角。地線應(yīng)盡量寬,最好使用大面積敷銅,這對接地點問題有相當(dāng)大的改善。

5.外時鐘是高頻的噪聲源,除能引起對本應(yīng)用系統(tǒng)的干擾之外,還可能產(chǎn)生對外界的干擾,使電磁兼容檢測不能達標(biāo)。在對系統(tǒng)可靠性要求很高的應(yīng)用系統(tǒng)中,選用頻率低的單片機是降低系統(tǒng)噪聲的原則之一。以8051單片機為例,最短指令周期1?s時,外時鐘是12MHz.而同樣速度的Motorola 單片機系統(tǒng)時鐘只需4MHz,更適合用于工控系統(tǒng)。近年來,一些生產(chǎn)8051兼容單片機的廠商也采用了一些新技術(shù),在不犧牲運算速度的前提下將對外時鐘的需求降至原來的1/3.而Motorola 單片機在新推出的68HC08系列以及其16/32位單片機中普遍采用了內(nèi)部鎖相環(huán)技術(shù),將外部時鐘頻率降至32KHz,而內(nèi)部總線速度卻提高到8MHz乃至更高。

6.布線要有合理的走向:如輸入/輸出,交流/直流,強/弱信號,高頻/低頻,高壓/低壓等……,它們的走向應(yīng)該是呈線形的(或分離),不得相互交融。其目的是防止相互干擾。最好的走向是按直線,但一般不易實現(xiàn),最不利的走向是環(huán)形。對于是直流,小信號,低電壓PCB設(shè)計的要求可以低些。所以“合理”是相對的。上下層之間走線的方向基本垂直。整個板子的不想要均勻,能不擠的不要擠在一齊。

7.在器件布置方面與其它邏輯電路一樣,應(yīng)把相互有關(guān)的器件盡量放得靠近些,這樣可以獲得較好的抗噪聲效果。時鐘發(fā)生器、晶振和CPU的時鐘輸入端都易產(chǎn)生噪聲,要相互靠近些,特別是晶振下方不要走信號線。易產(chǎn)生噪聲的器件、小電流電路、大電流電路等應(yīng)盡量遠離邏輯電路,如有可能,應(yīng)另做電路板,這一點十分重要。

二 地線技術(shù)

1.模擬電路和數(shù)字電路在元件布局圖的設(shè)計和布線方法上有許多相同和不同之處。模擬電路中,由于放大器的存在,由布線產(chǎn)生的極小噪聲電壓,都會引起輸出信號的嚴(yán)重失真,在數(shù)字電路中,TTL噪聲容限為0.4V~0.6V,CMOS噪聲容限為Vcc的0.3~0.45倍,故數(shù)字電路具有較強的抗干擾的能力。良好的電源和地總線方式的合理選擇是儀器可靠工作的重要保證,相當(dāng)多的干擾源是通過電源和地總線產(chǎn)生的,其中地線引起的噪聲干擾最大。

2.數(shù)字地與模擬地分開(或一點接地),地線加寬,要根據(jù)電流決定線寬,一般來說越粗越好(100mil線經(jīng)約通過1到2A的電流)。地線>電源線>信號線是線寬的合理選擇。

3.電源線和地線盡可能靠近,整塊印刷板上的電源與地要呈“井”字形分布,以便使分布線電流達到均衡。

4.為減少線間串?dāng)_,必要時可增加印刷線條間距離,在其安插一些零伏線作為線間隔離。特別是輸入輸出信號間,

三 去耦、濾波、隔離三大技術(shù)

1.去耦、濾波、隔離是硬件抗干擾常用的三大措施。

2.電源輸入端跨接10~100uf的電解電容器。如有可能,接100uF以上的更好;原則上每個集成電路芯片都應(yīng)布置一個0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個芯片布置一個1~10pF的但電容;對于抗噪能力弱、關(guān)斷時電源變化大的器件,如RAM、ROM存儲器件,應(yīng)在芯片的電源線和地線之間直接接入退藕電容;

3.濾波指各類信號按頻率特性分類并控制它們的方向。常用的有各種低通濾波器、高通濾波器、帶通濾波器。低通濾波器用在接入的交流電源線上,旨在讓50周的交流電順利通過,將其它高頻噪聲導(dǎo)入大地。低通濾波器的配置指標(biāo)是插入損耗,選擇的低通濾波器插入損耗過低起不到抑制噪聲的作用,而過高的插入損耗會導(dǎo)致“漏電”,影響系統(tǒng)的人身安全性。高通、帶通濾波器則應(yīng)根據(jù)系統(tǒng)中對信號的處理要求選擇使用。

4.典型的信號隔離是光電隔離。使用光電隔離器件將單片機的輸入輸出隔離開,一方面使干擾信號不得進入單片機系統(tǒng),另一方面單片機系統(tǒng)本身的噪聲也不會以傳導(dǎo)的方式傳播出去。屏蔽則是用來隔離空間輻射的,對噪聲特別大的部件,如開關(guān)電源,用金屬盒罩起來,可減少噪聲源對單片機系統(tǒng)的干擾。對特別怕干擾的模擬電路,如高靈敏度的弱信號放大電路可屏蔽起來。而重要的是金屬屏蔽本身必須接真正的地。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396424 -

BGA

+關(guān)注

關(guān)注

4文章

538瀏覽量

46734 -

功率器件

+關(guān)注

關(guān)注

41文章

1732瀏覽量

90336 -

布局設(shè)計

+關(guān)注

關(guān)注

0文章

9瀏覽量

7396

原文標(biāo)題:PCB設(shè)計的布局、走線與電磁兼容(整理)

文章出處:【微信號:電子設(shè)計寶典,微信公眾號:電子設(shè)計寶典】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

電源的PCB布局要點

PCB布局設(shè)計關(guān)鍵要點

PCB布局設(shè)計關(guān)鍵要點

評論