1 后摩爾時代,先進封裝成為提升芯片性能重要解法

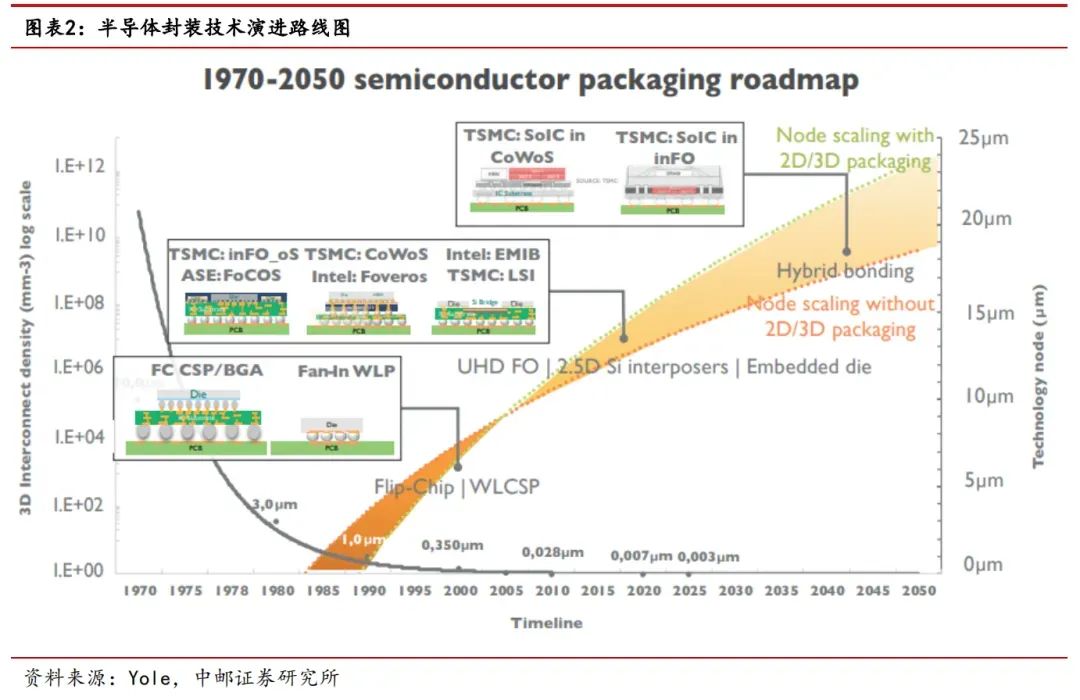

1.1 摩爾定律放緩,先進封裝日益成為提升芯片性能重要手段隨著摩爾定律放緩,芯片特征尺寸接近物理極限,先進封裝成為提升芯片性能,延續摩爾定律的重要手段。先進封裝是指處于前沿的封裝形式和技術,通過優化連接、在同一個封裝內集成不同材料、線寬的半導體集成電路和器件等方式,提升集成電路的連接密度和集成度。當前全球芯片制程工藝已進入3-5nm區間,接近物理極限,先進制程工藝芯片的設計難度、工藝復雜度和開發成本大幅增加,摩爾定律逐漸失效,半導體行業進入“后摩爾時代”。前道制程工藝發展受限,但隨著AI等新興應用場景快速發展,芯片性能要求日益提高,越來越多集成電路企業轉向后道封裝工藝尋求先進技術方案,以確保產品性能的持續提升。先進封裝技術應運而生,在“后摩爾時代”逐步發展為推動芯片性能提升的主要研發方向。

先進封裝有多種分類標準,是否有焊線或光刻工序是其中一種區分方式。傳統封裝不涉及光刻工序,切割后的晶圓通過焊線工藝實現芯片與引線框架的電性連接,從而完成芯片內外部的連通。先進封裝主要利用光刻工序實現線路重排(RDL)、凸塊制作(Bumping)及三維硅通孔(TSV)等工藝技術,涉及涂膠、曝光、顯影、電鍍、去膠、蝕刻等工序。

1.2 先進封裝份額占比提升,2.5D/3D封裝增速領先先進封裝

1.2 先進封裝份額占比提升,2.5D/3D封裝增速領先先進封裝

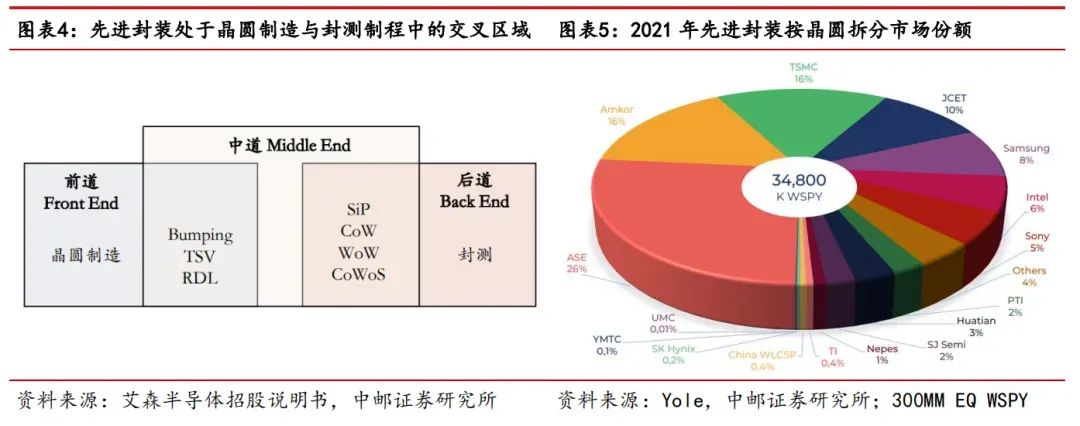

AI帶動先進封裝需求。TrendForce報告指出,聊天機器人等生成式AI應用爆發式增長,帶動2023年AI服務器開發大幅擴張。這種對高端AI服務器的依賴,需要使用高端AI芯片,這不僅將拉動2023~2024年HBM的需求,而且預計還將在2024年帶動先進封裝產能增長30~40%。先進封裝增速高于整體封裝,2.5D/3D封裝增速居先進封裝之首。根據Yole,2021年,先進封裝市場規模約375億美元,占整體封裝市場規模的44%,預計到2027年將提升至占比53%,約650億美元,CAGR21-27為9.6%,高于整體封裝市場規模CAGR21-27 6.3%。先進封裝中的2.5D/3D封裝多應用于(x)PU, ASIC, FPGA, 3D NAND, HBM, CIS等,受數據中心、高性能計算、自動駕駛等應用的驅動,2.5D/3D封裝市場收入規模CAGR21-27高達14%,在先進封裝多個細分領域中位列第一。

1.3 先進封裝處于晶圓制造與封測的交叉區域先進封裝處于晶圓制造與封測制程中的交叉區域,涉及IDM、晶圓代工、封測廠商。先進封裝要求在晶圓劃片前融入封裝工藝步驟,具體包括應用晶圓研磨薄化、重布線(RDL)、凸塊制作(Bumping)及硅通孔(TSV)等工藝技術,涉及與晶圓制造相似的光刻、顯影、刻蝕、剝離等工序步驟,從而使得晶圓制造與封測前后道制程中出現中道交叉區域,如圖表4所示。前后道大廠爭先布局先進封裝,競爭格局較為集中。后摩爾時代,先進制程成本快速提升,一些晶圓代工大廠發展重心正在從過去追求更先進納米制程,轉向封裝技術的創新。諸如臺積電、英特爾、三星、聯電等芯片制造廠商紛紛跨足封裝領域。先進封裝競爭格局較為集中,全球主要的6家廠商,包括2家IDM廠商(英特爾、三星),一家代工廠商(臺積電),以及全球排名前三的封測廠商(日月光、Amkor、JCET),共處理了超過80%的先進封裝晶圓。

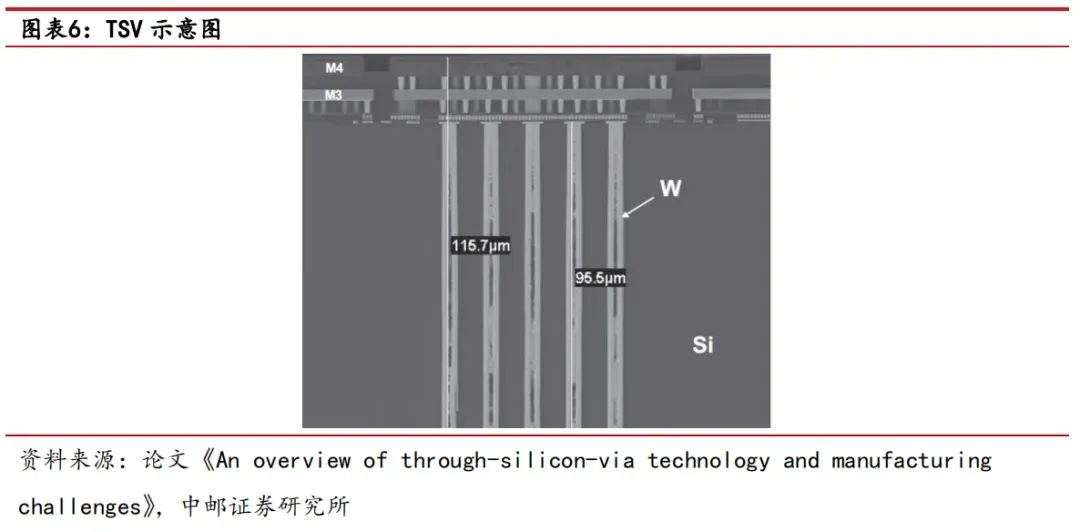

2 TSV:硅通孔,先進封裝關鍵技術2.1 TSV:硅通孔技術,芯片垂直堆疊互連的關鍵技術TSV(Through Silicon Via),硅通孔技術,是通過硅通道垂直穿過組成堆棧的不同芯片或不同層實現不同功能芯片集成的先進封裝技術。TSV主要通過銅等導電物質的填充完成硅通孔的垂直電氣互連,減小信號延遲,降低電容、電感,實現芯片的低功耗、高速通信,增加帶寬和實現器件集成的小型化需求。此前,芯片之間的大多數連接都是水平的,TSV的誕生讓垂直堆疊多個芯片成為可能。Wire bonding(引線鍵合)和Flip-Chip(倒裝焊)的Bumping(凸點)提供了芯片對外部的電互連,RDL(再布線)提供了芯片內部水平方向的電互連,TSV則提供了硅片內部垂直方向的電互連。

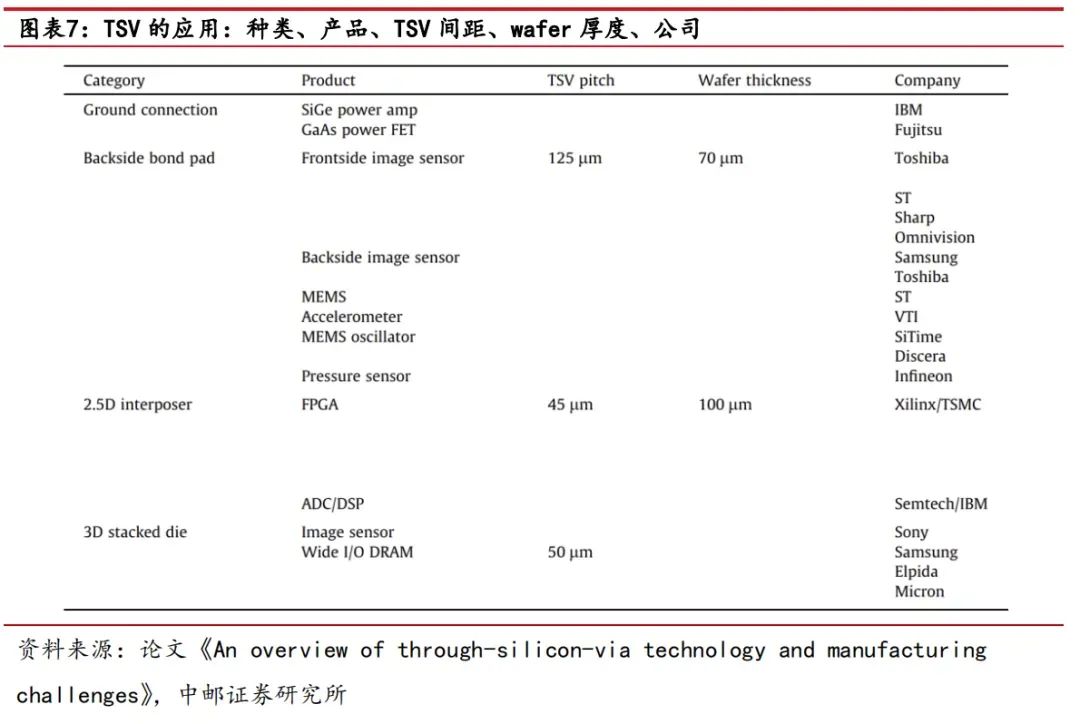

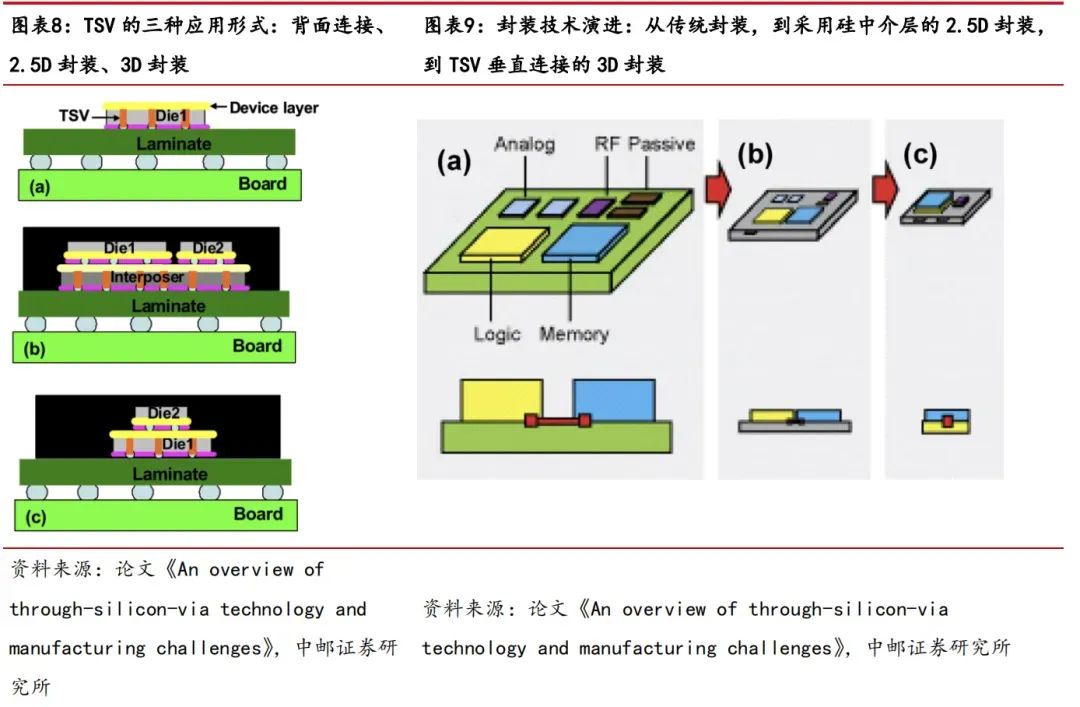

2.2 TSV三種主要應用方向:背面連接、2.5D封裝、3D封裝TSV有多種用途(如圖表7),可大致分為3種(如圖表8):(a) 垂直的背面連接,無芯片堆疊,如“簡單的背面連接”。TSV位于有源晶粒(active die)中,用于連接至晶圓背面的焊盤(bond pad);(b) 2.5D封裝。晶粒(die)連接至硅中介層(interposer),TSV在中介層中;(c) 3D封裝。TSV位于有源晶粒中,用于實現芯片堆疊。

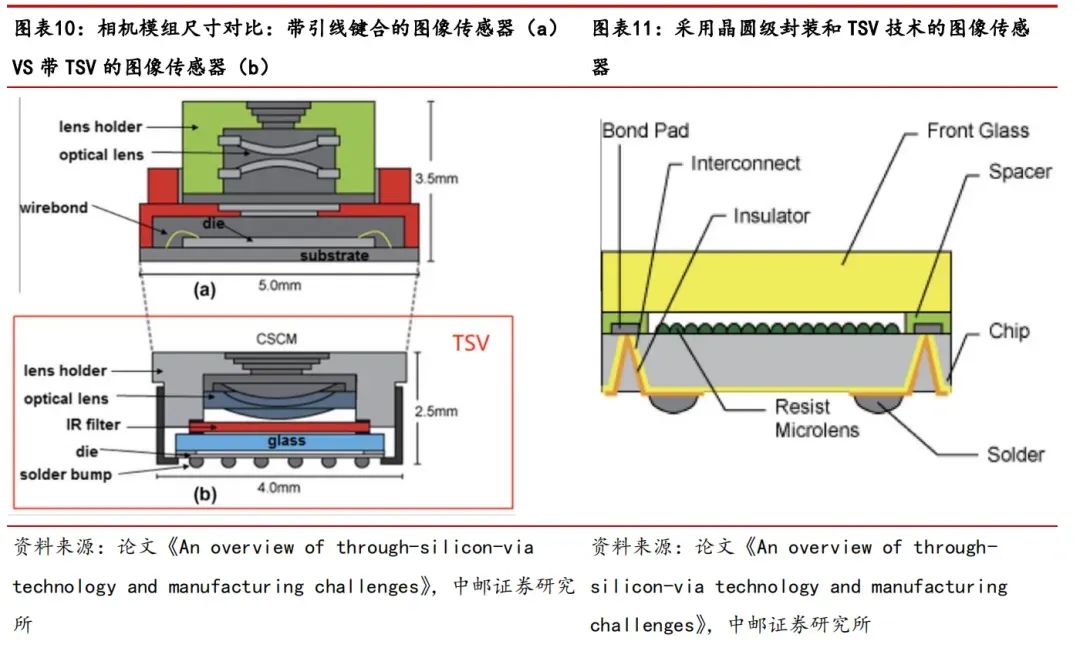

(a)TSV作為簡單背面連接:用于CIS和鍺化硅(SiGe)功率放大器TSV三種主要應用方式中,簡單的背面連接結構是技術難度最低的,也是TSV技術首次大規模投入生產時的應用方向,如CMOS圖像傳感器(CIS)、SiGe功率放大器兩個產品就應用了TSV技術。將TSV用于CMOS圖像傳感器有許多優點:1)使用TSV代替引線鍵合可以減小相機模組的尺寸(如圖表10)。2)簡化了圖像傳感器的晶圓級封裝(WLP)(如圖表11)。WLP工藝的第一步是將玻璃晶圓附著到圖像傳感器的正面,防止光刻膠(抗蝕劑)微透鏡在組裝過程中受到損壞和污染,然而安裝好玻璃晶圓后會使從晶圓正面到焊盤的連接途徑受阻,TSV通過簡化晶圓級封裝,對此問題提供了簡易的解決方法。

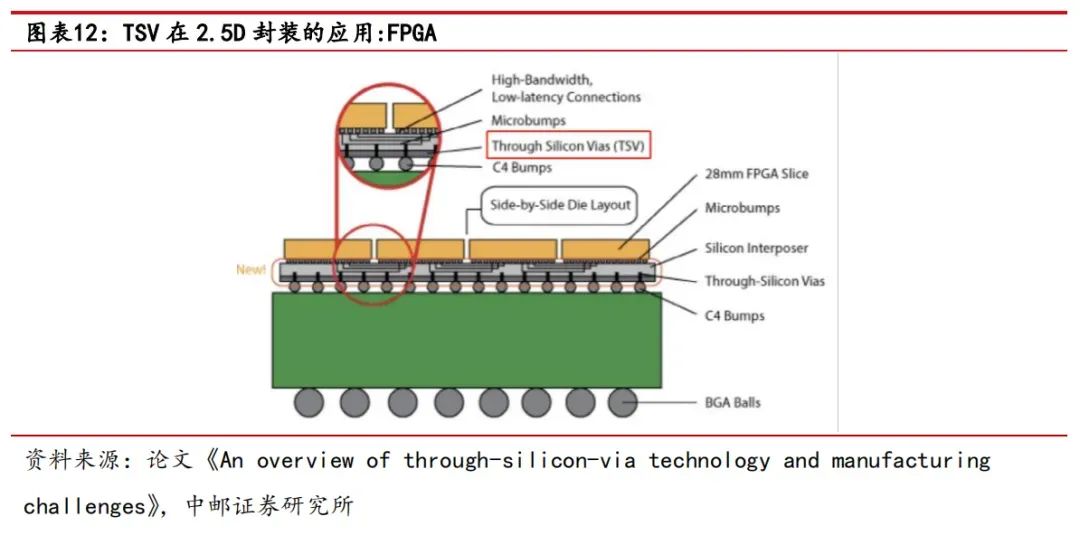

(b)TSV應用于2.5D封裝:FPGA

與簡單的背面連接相比,2.5D先進封裝的硅中介層需要更小的TSV間距(≤50 μm),因此需要更先進的TSV工藝。現場可編程門陣列(Field Programmable Gate Array,FPGA)器件是最早使用硅中介層的產品之一:硅中介層可以使芯片間密切連接,整合后的結構看起來像單個大尺寸的FPGA芯片,解決了早期直接構建單個大尺寸FPGA芯片的技術難題。

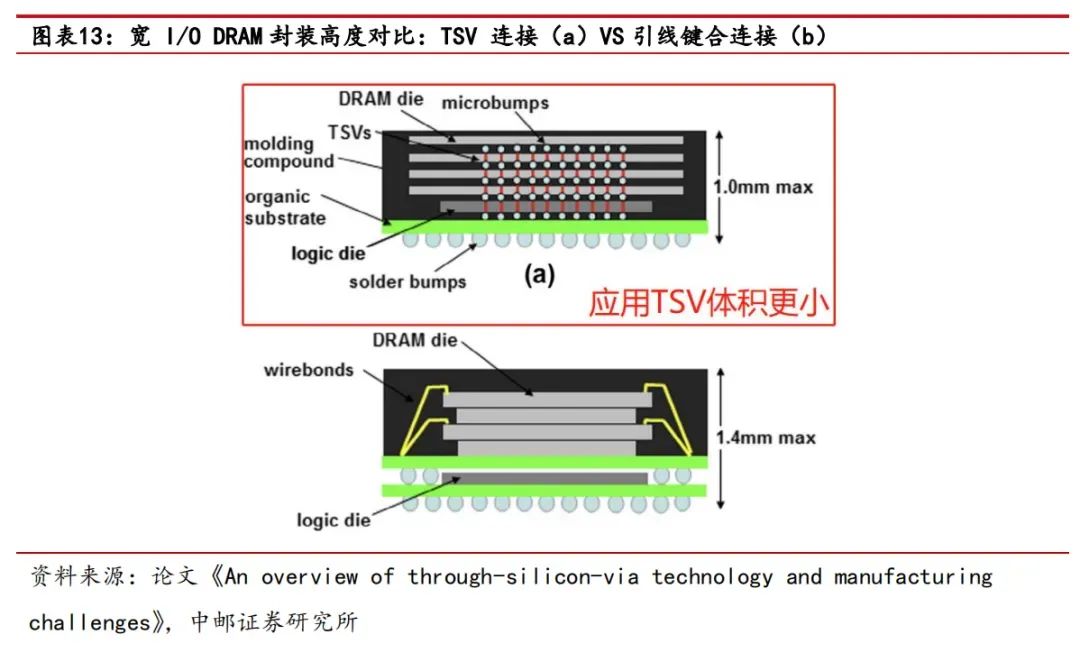

(c)TSV應用于3D封裝:存儲器堆疊存儲器堆疊是首批應用3D堆疊TSV結構的產品之一,和2.5D封裝中硅中介層對TSV間距的需求相似,但實際應用中難度更高,例如寬I/O DRAM設備。使用寬 I/O DRAM 和芯片堆疊的優勢包括封裝高度降低40%,功耗降低50%,帶寬增加6倍。

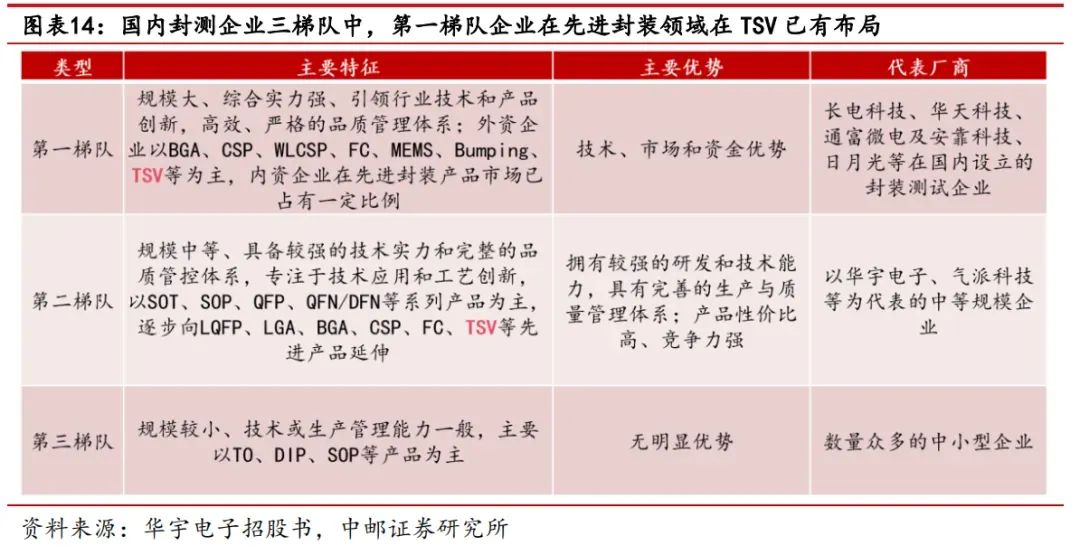

2.3 國內封測廠TSV布局情況:多家頭部廠商已有布局內資封測廠商向TSV等先進封裝領域突破。全球半導體產業經歷二次產業轉移,目前處于第三次產業轉移的進程之中,作為半導體領域壁壘相對較低的領域,封測產業目前主要轉移至亞洲區域,主要包括中國大陸、中國臺灣、東南亞等。封測是中國大陸集成電路發展最為完善的板塊,技術能力與國際先進水平比較接近,我國封測市場已形成內資企業為主的競爭格局。中國大陸封測市場目前主要以傳統封裝業務為主,經過多年的技術創新和市場積累,內資企業產品已由DIP、SOP、SOT、QFP等產品向QFN/DFN、BGA、CSP、FC、TSV、LGA、WLP等技術更先進的產品發展,并且在WLCSP、FC、BGA和TSV等技術上取得較為明顯的突破,產量與規模不斷提升,逐步縮小與外資廠商之間的技術差距,極大地帶動我國封裝測試行業的發展。 我國頭部封測企業,如長電科技、通富微電、華天科技、晶方科技已有采用TSV技術封裝的產品批量出貨。2.5D/3D封裝所需的晶圓內部的加工如TSV加工,硅轉接板加工等工序屬于晶圓廠擅長制程,而晶圓,裸芯片(Die)之間的高密度互聯和堆疊,以及和基板,接點的互聯技術屬于芯片后道成品制造環節的優勢。應用于CoWoS等2.5D/3D先進封裝中的TSV技術對深寬比等有更高要求,需要用到諸多前道設備,仍多由晶圓廠來完成。國內封測廠則在先進封裝平臺、CIS封裝等領域對TSV技術有所布局。長電科技的XDFOI技術平臺有TSV less和TSV方案。通富微電2021年在高性能計算領域建成了2.5D/3D封裝平臺(VISionS)及超大尺寸FCBGA研發平臺,并完成高層數再布線技術開發,可為客戶提供晶圓級和基板級Chiplet封測解決方案;在存儲器領域,多層堆疊NAND Flash及LPDDR封裝實現穩定量產,并在國內首家完成基于TSV技術的3DS DRAM封裝開發。華天科技工業級12吋TSV-CIS產品已實現量產。晶方科技應用晶圓級硅通孔(TSV)封裝技術,聚焦以影像傳感芯片為代表的智能傳感器市場,封裝的產品主要包括CIS芯片、TOF芯片、生物身份識別芯片、MEMS芯片等,應用于智能手機、安防監控數碼、汽車電子等市場領域。

我國頭部封測企業,如長電科技、通富微電、華天科技、晶方科技已有采用TSV技術封裝的產品批量出貨。2.5D/3D封裝所需的晶圓內部的加工如TSV加工,硅轉接板加工等工序屬于晶圓廠擅長制程,而晶圓,裸芯片(Die)之間的高密度互聯和堆疊,以及和基板,接點的互聯技術屬于芯片后道成品制造環節的優勢。應用于CoWoS等2.5D/3D先進封裝中的TSV技術對深寬比等有更高要求,需要用到諸多前道設備,仍多由晶圓廠來完成。國內封測廠則在先進封裝平臺、CIS封裝等領域對TSV技術有所布局。長電科技的XDFOI技術平臺有TSV less和TSV方案。通富微電2021年在高性能計算領域建成了2.5D/3D封裝平臺(VISionS)及超大尺寸FCBGA研發平臺,并完成高層數再布線技術開發,可為客戶提供晶圓級和基板級Chiplet封測解決方案;在存儲器領域,多層堆疊NAND Flash及LPDDR封裝實現穩定量產,并在國內首家完成基于TSV技術的3DS DRAM封裝開發。華天科技工業級12吋TSV-CIS產品已實現量產。晶方科技應用晶圓級硅通孔(TSV)封裝技術,聚焦以影像傳感芯片為代表的智能傳感器市場,封裝的產品主要包括CIS芯片、TOF芯片、生物身份識別芯片、MEMS芯片等,應用于智能手機、安防監控數碼、汽車電子等市場領域。 3TSV制造流程及所需設備

3TSV制造流程及所需設備

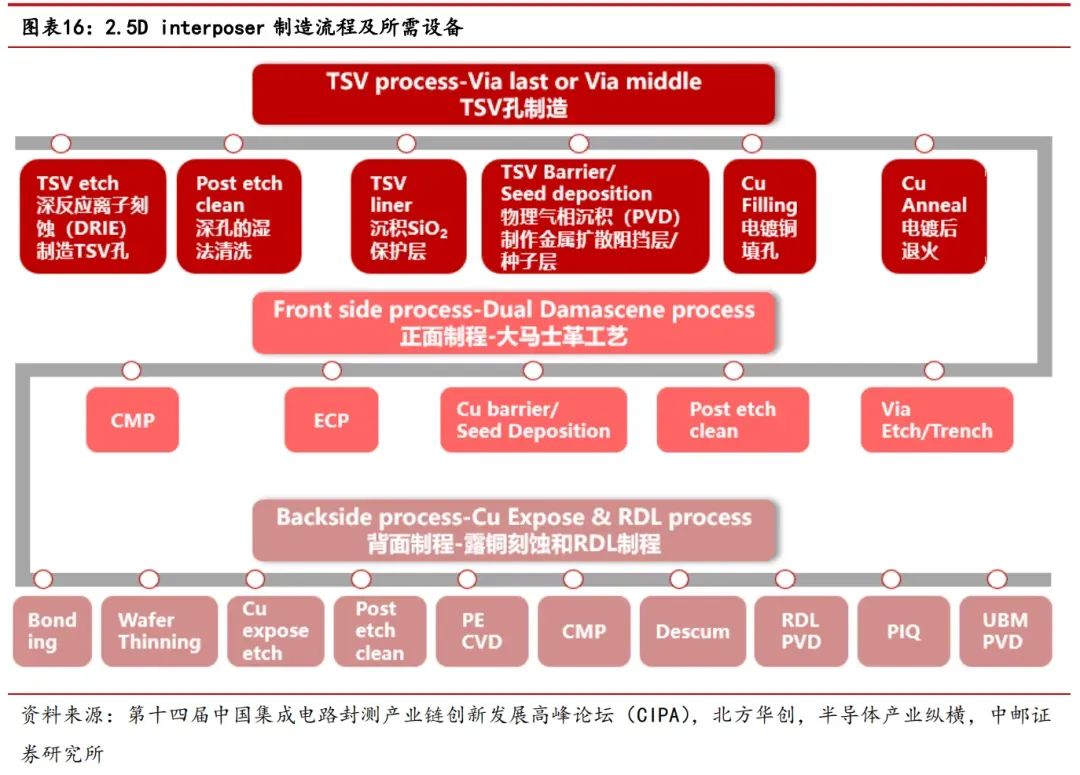

3.1 TSV制造流程以2.5D interposer為例,其制造流程可以分為三大部分:TSV process-Via last or Via middle(TSV孔的制造)、Front side process-Dual Damascene process(正面制程-大馬士革工藝)以及Backside process-Cu Expose & RDL process(背面制程-露銅刻蝕和RDL制程)。每個部分具體環節對應不同設備及不同指標。TSV process:

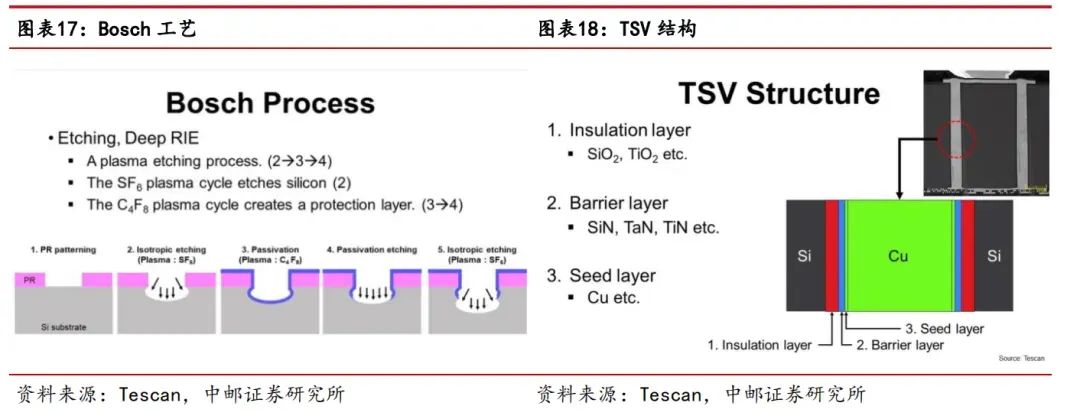

1)TSV etch:深反應離子刻蝕(DRIE)制作TSV孔,可用技術包括Non-Bosch Process與Bosch Process,其中Non-Bosch很難實現更高深寬比的刻蝕且效率有限;而Bosch工藝由于采用一步刻蝕一步沉積的方式,可以實現更高深寬比的刻蝕,另外其速率更快,可滿足業界對成本與效率的要求。因此該步驟目前首選技術是基于Bosch工藝的干法刻蝕,使用到感應耦合高密度等離子體干法刻蝕機(ICP)。

2)Post etch clean:使用濕法方式進行深孔的清洗,需用到清洗設備。

3)TSV liner:沉積二氧化硅保護層liner,可用等離子增強化學氣相沉積(PECVD)制作介電層;另外由于TSV的深寬比更高,亦用SACVD+PECVD的方式沉積,但是這種沉積方式要求深寬比要小于10:1并且開口需要大于10微米;北方華創用PEALD的方式。

4)TSV Barrier/Seed deposition:物理氣相沉積(PVD)制作金屬擴散阻擋層(業界一般使用Ti/TiN或者Ta/TaN,要求連續,需要滿足最薄厚度的要求;同時要求有優良的粘附性)/種子層(業界一般使用Cu,要求連續,需要滿足最薄厚度的要求;同時頂部不能有over hang),防止金屬擴散到硅中或者金屬擴散到氧化物中。

5)Cu Filling:用銅/鎢電鍍填孔,要求不留縫隙,同時盡量減少電鍍過程中的應力;使用ECP。

6)Cu Anneal:電鍍后的退火,因為銅在室溫下有自退火效應,若不做退火,則給后道的CMP帶來很大的不穩定性,做完退火后銅的晶粒分布更加均勻、晶界數量減少,增加銅的電遷移的可靠性,電阻率可以降低20%;業界用立式爐。Front side process-Dual Damascene process包括Via Etch/Trench(Etch Via/Trench的刻蝕)、Post etch clean(刻蝕后的清洗)、Cu barrier/Seed Deposition(阻擋層/種子層的沉積)、ECP(電鍍)以及CMP(化學機械拋光去除多余的金屬)。Backside process-Cu Expose & RDL process包括Bonding(臨時鍵合)、Wafer Thinning(減薄)、Cu expose etch(用干法刻蝕的方式把TSV的銅柱露出來(BFR、BVR工藝))、Post etch clean(濕法清洗)、PECVD(PECVD做鈍化)、CMP SiO2(磨掉銅柱上面的氮化硅,為RDL做準備)以及RDL制程(Descum、RDL PVD、PIQ、UBM PVD)。 3.2 TSV關鍵工藝設備及特點TSV生產流程涉及到深孔刻蝕、PVD、CVD、銅填充、微凸點及電鍍、清洗、減薄、鍵合等二十余種設備,其中深孔刻蝕、氣相沉積、銅填充、清洗、CMP去除多余的金屬、晶圓減薄、晶圓鍵合等工序涉及的設備最為關鍵。1)深孔刻蝕設備深孔刻蝕是TSV的關鍵工藝,目前首選技術是基于Bosch工藝的干法刻蝕。深反應等離子刻蝕設備是感應耦合高密度等離子體干法刻蝕機(Inductively Coupled Plasma Etcher),采用半導體刻蝕機的成熟技術,獨特設計的雙等離子體源實現了對腔室內等離子體密度的均勻控制,滿足硅高深寬比刻蝕工藝的要求。具有穩定可靠的工藝性能、寬闊的工藝窗口和良好的工藝兼容性,用于晶片的高深寬比刻蝕。

3.2 TSV關鍵工藝設備及特點TSV生產流程涉及到深孔刻蝕、PVD、CVD、銅填充、微凸點及電鍍、清洗、減薄、鍵合等二十余種設備,其中深孔刻蝕、氣相沉積、銅填充、清洗、CMP去除多余的金屬、晶圓減薄、晶圓鍵合等工序涉及的設備最為關鍵。1)深孔刻蝕設備深孔刻蝕是TSV的關鍵工藝,目前首選技術是基于Bosch工藝的干法刻蝕。深反應等離子刻蝕設備是感應耦合高密度等離子體干法刻蝕機(Inductively Coupled Plasma Etcher),采用半導體刻蝕機的成熟技術,獨特設計的雙等離子體源實現了對腔室內等離子體密度的均勻控制,滿足硅高深寬比刻蝕工藝的要求。具有穩定可靠的工藝性能、寬闊的工藝窗口和良好的工藝兼容性,用于晶片的高深寬比刻蝕。 2)氣相沉積設備氣相沉積設備主要用于薄膜電路表面的高低頻低應力氧化硅等薄膜淀積。設備具有低溫TEOS工藝沉積氧化硅薄膜,應力易調控,適用于薄膜電路制造中保護膜層的沉積。設備應具有預真空室、基片傳送模塊以及工藝模塊等,傳片及工藝過程自動化。絕緣層做好后,通過物理氣相沉積法(PVD)沉積金屬擴散阻擋層和種子層,為后續的銅填充做好準備。后續的電鍍銅填充要求TSV側壁和底部具有連續的阻擋層和種子層。種子層的連續性和均勻性被認為是TSV銅填充最重要的影響因素。根據硅通孔的形狀、深寬比及沉積方法不同,種子層的特點也各有不同,種子層沉積的厚度、均勻性和粘合強度是極為重要的指標。

2)氣相沉積設備氣相沉積設備主要用于薄膜電路表面的高低頻低應力氧化硅等薄膜淀積。設備具有低溫TEOS工藝沉積氧化硅薄膜,應力易調控,適用于薄膜電路制造中保護膜層的沉積。設備應具有預真空室、基片傳送模塊以及工藝模塊等,傳片及工藝過程自動化。絕緣層做好后,通過物理氣相沉積法(PVD)沉積金屬擴散阻擋層和種子層,為后續的銅填充做好準備。后續的電鍍銅填充要求TSV側壁和底部具有連續的阻擋層和種子層。種子層的連續性和均勻性被認為是TSV銅填充最重要的影響因素。根據硅通孔的形狀、深寬比及沉積方法不同,種子層的特點也各有不同,種子層沉積的厚度、均勻性和粘合強度是極為重要的指標。

3)銅填充設備深孔金屬化電鍍設備用于新一代高頻組件高深寬比通孔填孔電鍍銅工藝,解決高深寬比微孔內的金屬化問題,提高互聯孔的可靠性。TSV填孔鍍銅工序是整個TSV工藝里最核心、難度最大的工藝,對設備的要求比較高,成熟的用于TSV填孔鍍銅的設備價格昂貴。

4)減薄拋光設備一旦完成了銅填充,則需要對晶圓進行減薄拋光。TSV要求晶圓減薄至50μm甚至更薄,要使硅孔底部的銅暴露出來,為下一步的互連做準備。目前晶圓減薄可以通過機械研磨、化學機械拋光、濕法及干法化學處理等不同的加工工序來實現,但晶圓很難容忍減薄過程中的磨削對晶圓的損傷及內在應力,其剛性也難以使晶圓保持原有的平整狀態,同時后續工藝的晶圓傳遞、搬送也遇到了很大的問題。目前業界的多采用一體機的思路,將晶圓的磨削、拋光、貼片等工序集合在一臺設備內。

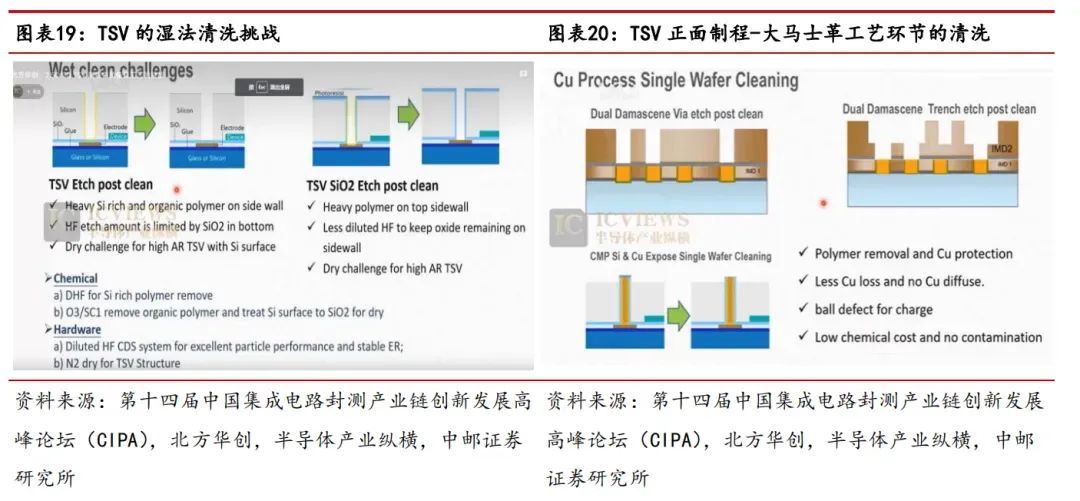

5)清洗設備TSV的濕法清洗不同于晶圓級封裝等先進封裝,其中有幾個關鍵工序需用到清洗:①TSV刻蝕后清洗:有比較重的硅的殘留、側壁的polymer比較重,清洗的時候不能破壞底部的二氧化硅;②TSV長完liner后要把底部的二氧化硅打開后清洗,清洗底部的同時不能破壞側壁長好的liner的二氧化硅;③大馬士革正面制程刻蝕后的清洗包括Via刻蝕后和Trench刻蝕后;④露銅過程前后的清洗。 6)檢測量測設備:在后段封裝工藝中,芯片倒裝(Flip-chip)、圓片級封裝(Wafer-level Packaging)和硅通孔(Through-silicon Via,TSV)等先進工藝要求對凸點(Bump)、通孔(TSV)、銅柱(Copper pillar)等的缺損/異物殘留及其形狀、間距、高度的一致性,以及重布線層(Re-distribution layer,RDL)進行無接觸定量檢查和測量,以保證集成電路芯片生產線快速進入量產階段并獲取穩定的高成品率和高經濟效益。

6)檢測量測設備:在后段封裝工藝中,芯片倒裝(Flip-chip)、圓片級封裝(Wafer-level Packaging)和硅通孔(Through-silicon Via,TSV)等先進工藝要求對凸點(Bump)、通孔(TSV)、銅柱(Copper pillar)等的缺損/異物殘留及其形狀、間距、高度的一致性,以及重布線層(Re-distribution layer,RDL)進行無接觸定量檢查和測量,以保證集成電路芯片生產線快速進入量產階段并獲取穩定的高成品率和高經濟效益。

4 風險提示下游需求不及預期;行業景氣度復蘇不及預期;公司技術與產品迭代進展不及預期等。

-

芯片

+關注

關注

453文章

50406瀏覽量

421825 -

半導體

+關注

關注

334文章

27010瀏覽量

216301 -

封裝

+關注

關注

126文章

7784瀏覽量

142724 -

后摩爾時代

+關注

關注

0文章

12瀏覽量

9172 -

TSV

+關注

關注

4文章

108瀏覽量

81443

發布評論請先 登錄

相關推薦

TSV 制程關鍵工藝設備技術及發展

大族封測創業板IPO終止

基于兩步刻蝕工藝的錐形TSV制備方法

TSV與異構集成技術的前沿進展與趨勢展望

半導體封測廠日月光投控宣布收購英飛凌2座封測廠!

大族封測IPO終止

一文詳解硅通孔技術(TSV)

封測:TSV研究框架

封測:TSV研究框架

評論