在FPGA設(shè)計中,我們通常采用的都是“自頂向下”的設(shè)計方法,即現(xiàn)有頂層設(shè)計,再有細節(jié)設(shè)計。比如先有整個項目的功能框圖、數(shù)據(jù)流程圖等,然后再細分功能到一級模塊,每個一級模塊再細分到二級、三級甚至更低級別的模塊。除了每個模塊的設(shè)計,如何把模塊連接起來?也是一個很有趣且重要的話題,這就是我們通常說的內(nèi)部模塊接口。這里先介紹幾種常見的內(nèi)部模塊接口。

AXI接口

目前xilinx或者intel提供的IP core中的接口越來越多的都支持AXI接口,這種接口是業(yè)界非常通用的接口,使用的頻率也非常的高,關(guān)于這個接口的說明,網(wǎng)上有很多資料,本文不在這里介紹該接口相關(guān)的信息。

采用這種接口有什么好處呢?顯然IP的移植性非常好,只要是使用AXI接口的設(shè)計,都可以直接調(diào)用這樣的IP,不需要做任何接口上的修改,也不會出現(xiàn)對接口理解上的差異,確實很方便。尤其是你的模塊需要和外部模塊對接的時候,這里的外部可能是外部的客戶、外部的合作伙伴等,標(biāo)準的接口也能減少對接的溝通成本。

AXI接口筆者覺得也有一些缺點,接口相對比較復(fù)雜。如果我們的FPGA設(shè)計只是公司或者部門內(nèi)使用,不需要對外,甚至都不需要重用的時候,那有沒有一些更加簡單的接口呢?這里重點介紹2種內(nèi)部模塊間通用接口,最后再說明這樣接口的好處。

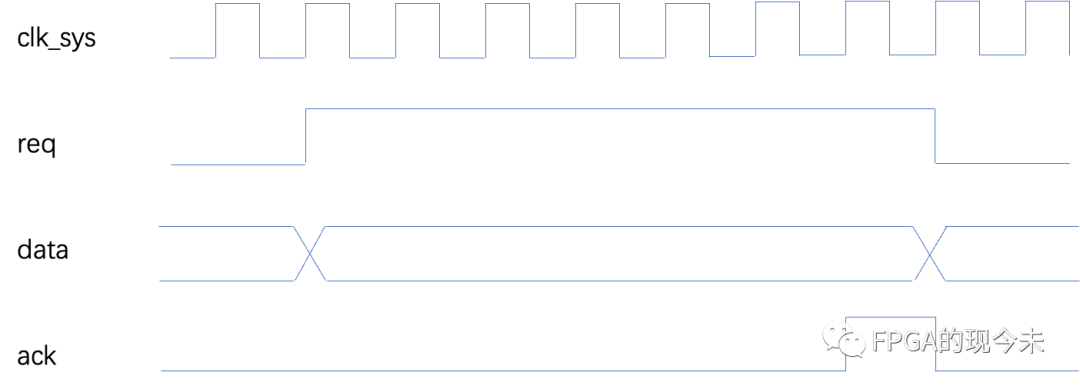

req-ack接口

先看時序圖,這種接口通常是請求方有數(shù)據(jù)要發(fā)送之前,先發(fā)送一個req請求信號,同時保持數(shù)據(jù)不變,一直等待響應(yīng)方的應(yīng)答。當(dāng)響應(yīng)方處理完數(shù)據(jù)后,給一個ack應(yīng)答信號,表示一次數(shù)據(jù)傳送完成。

這種接口的應(yīng)用場景是什么呢?它一般應(yīng)用在低速、無緩存數(shù)據(jù)傳輸場景。當(dāng)2個模塊之間的接口傳輸數(shù)據(jù)的性能較低,且有相互依賴,就可以采用這類接口。從時序圖可以看出,在req階段,整個data是不會變化,直到有ack后,再發(fā)送下一個數(shù)據(jù)。數(shù)據(jù)的傳輸依賴請求和響應(yīng)雙方的配合,彼此牽制。另外,發(fā)送發(fā)等當(dāng)前數(shù)據(jù)處理完成后,才會有一下次數(shù)據(jù)發(fā)送,所以這類場景無需數(shù)據(jù)緩存,比較節(jié)省資源,但是性能較低。

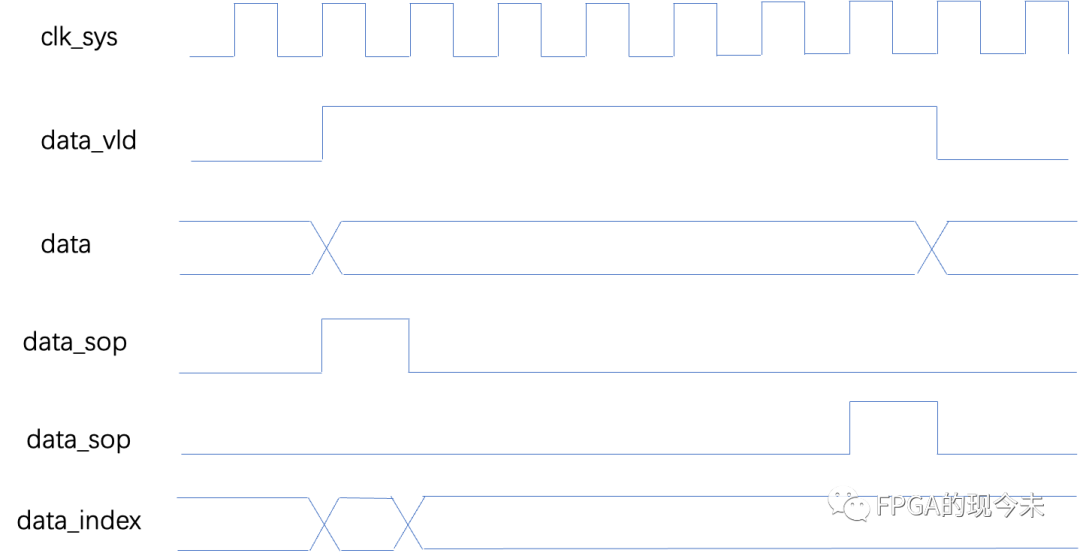

流式接口

先看時序圖,該接口共有5個信號, data_vld(數(shù)據(jù)有效信號)、 data(數(shù)據(jù)本身)、 data_sop(表示數(shù)據(jù)開始)、 data_eop(表示數(shù)據(jù)結(jié)束)、 data_index(和data相關(guān)的其他信號,位寬和格式可以用戶自定義,往往在data_sop = 1或者data_eop = 1的時候有效,或者在整個data_vld = 1期間保持不變)、 data_afull(數(shù)據(jù)反壓信號,通知對端不要再發(fā)送data)。

這種接口信號,非常的像fifo的寫接口信號,通過這種接口在發(fā)送數(shù)據(jù)的過程中,只要對端不反壓就可以不停的發(fā)送。這種接口實現(xiàn)簡單,模塊之間高度解耦,性能較好。

也有人會想,用這樣的私有接口,為什么不用標(biāo)準axi_stream接口呢?確實這2種接口已經(jīng)非常非常的相似了,唯一的不同就是反壓的處理,私有接口是不反壓的時候數(shù)據(jù)就可以無限制的發(fā)送,即發(fā)數(shù)據(jù)依賴data_afull = 0。但是axi_stream接口的vld和ready之間是沒有相關(guān)關(guān)系的,協(xié)議規(guī)定不能相互依賴,這點這內(nèi)部處理起來就稍稍麻煩點點。

另外即使afull = 1以后,一般都還可以繼續(xù)發(fā)送2-3拍數(shù)據(jù),時序處理起來也非常的簡單。而axi_stream中的vld和ready之間是嚴格的時序關(guān)系,必須同時為1,數(shù)據(jù)才能正常發(fā)送,時序處理起來相對麻煩。

總結(jié)

當(dāng)有對外的接口時,應(yīng)該還是要采用業(yè)界標(biāo)準的接口,但是模塊內(nèi)部的設(shè)計,還是要遵循設(shè)計簡單、實用可靠、無依賴,性能高的基本原則。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601886 -

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

26487 -

接口

+關(guān)注

關(guān)注

33文章

8504瀏覽量

150840 -

AXI

+關(guān)注

關(guān)注

1文章

127瀏覽量

16598

發(fā)布評論請先 登錄

相關(guān)推薦

fpga內(nèi)部主要結(jié)構(gòu)及其功能分析(Kintex-7FPGA內(nèi)部結(jié)構(gòu))

【FPGA設(shè)計實例】基于FPGA的串行接口(RS-232)

學(xué)fpga的內(nèi)部結(jié)構(gòu)和各接口實驗怎么學(xué)

通過FPGA實現(xiàn)溫控電路接口及其與DSP通信接口的設(shè)計

如何避免FPGA內(nèi)部操作和ADC數(shù)據(jù)之間的同步問題?

基于FPGA的十端口千兆以太網(wǎng)接口的設(shè)計與實現(xiàn)

基于FPGA的SPI4.2接口設(shè)計

接口、內(nèi)部類和Java API基礎(chǔ)

怎么讓FPGA內(nèi)部超高帶寬邏輯互連的方法

如何使用FPGA內(nèi)部的ROM以及程序?qū)υ揜OM的數(shù)據(jù)讀操作

FPGA內(nèi)部詳細架構(gòu)

內(nèi)部通信接口介紹

FPGA內(nèi)部接口設(shè)計

FPGA內(nèi)部接口設(shè)計

評論