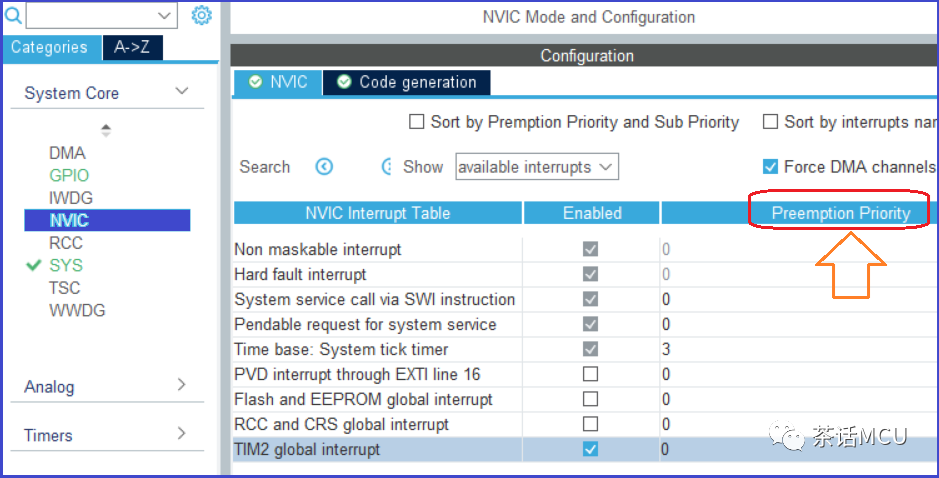

有些STM32用戶,尤其是那些用過基于ARM Cortx-M3/M4/M7內核的STM32 MCU的用戶,在使用基于M0/M0+內核的STM32系列并通過STM32CubeMx進行NVIC配置時,不難發現一個問題,那就是怎么沒有中斷子優先級【或稱響應優先級、副優先級等】的配置?!【當然,很多時候我們或許沒有關注子優先級】如下圖所示,只看到搶占優先級的配置,看不到子優先級的配置項。

上圖是我基于STM32L0系列芯片的配置,該系列芯片是基于ARM Cortex-M0+內核的。我們再看看下圖的NVIC配置頁面,顯然可以看到搶占優先級【Preemption Priority】和子優先級【Sub

Priority】的配置項及相關信息。

上圖是我基于STM32G4系列芯片的NVIC配置頁面。該系列的內核是ARM Cortex-M4。

當我們使用STM32系列芯片并通過CubeMx圖形化工具進行NVIC配置時,相應界面有無子優先級的配置,取決于該系列芯片所用的ARM Cortex內核。如果說所用STM32系列是基于ARM Cortex-M0或M0+內核的,在進行NVIC配置時是沒有子優先級可以配置的。

ARM Cortex-M0或M0+內核的中斷優先級控制寄存器實際有效位就是2位,全部用來對各個中斷/異常做搶占優先級配置,不額外劃分子優先級的配置。

也就是說,基于ARM Cortex-M0或M0+內核的STM32 MCU的NVIC配置不會有子優先級的概念和配置,對于優先級可配置的中斷而言,總共就4個可搶占優先級。下圖是基于ARM Cortex-M0或M0+內核的STM32系列展示。當然,STM32系列涉及的內核很多,遠不止下面這些,還有M4/M7/M33等。

而ARM Cortex-M3、M4、M7內核的中斷優先級配置寄存器的有效位為4位,同時還可以基于該4位做優先級的分組,進而引出搶占優先級和子優先級。

-

芯片

+關注

關注

453文章

50406瀏覽量

421833 -

mcu

+關注

關注

146文章

16992瀏覽量

350314 -

ARM

+關注

關注

134文章

9046瀏覽量

366817 -

STM32

+關注

關注

2266文章

10871瀏覽量

354812

發布評論請先 登錄

相關推薦

STM32 MCU通過STM32CubeMx配置NVIC怎么沒有中斷子優先級選項

STM32F103的寄存器NVIC_IPRx搶占優先級和子優先級是怎么設置的?

[轉] STN32搶占優先級與副優先級及中斷優先級NVIC理解

UCOS3的串口優先級配置問題如何解決

stm32配置中斷的優先級問題

NVIC中斷優先級分組

關于STM32H725 NVIC優先級和次優先級問題求解

STM32NVIC中斷優先級

為什么使用CubeMx配置NVIC時不見子優先級選項

為什么使用CubeMx配置NVIC時不見子優先級選項

評論