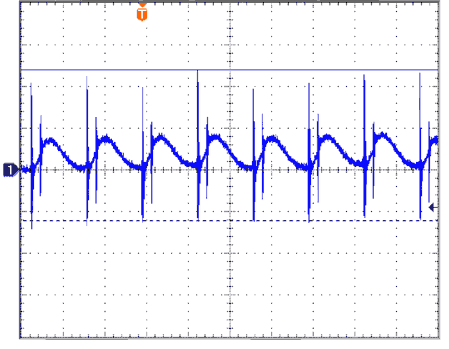

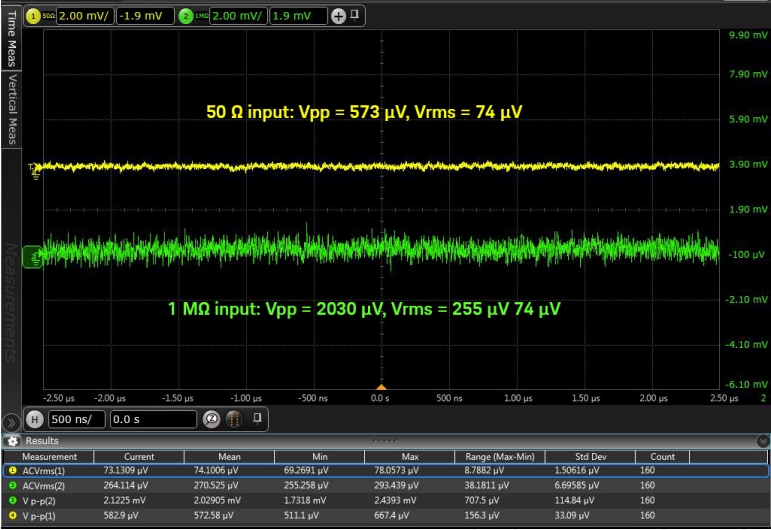

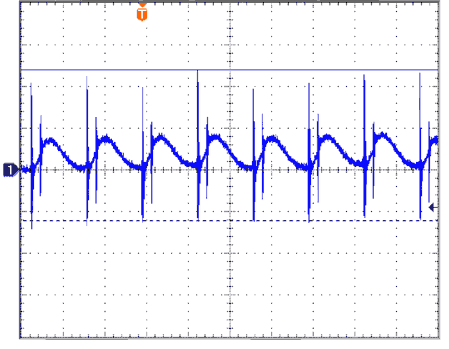

盡管看似簡單,但PCB和高級封裝中的功率傳輸仍然是設計人員面臨的最大挑戰之一,尤其是在數據中心、邊緣計算、移動設備和電信/網絡等環境中。在這些環境中,大量數據通過極高的數據速率通道傳輸,盡管我們非常關注信號完整性,但如果沒有穩定的電源,這些系統都無法工作。電源完整性發生在元件級和PCB級,正如其他人在本博客中提到的那樣,電源完整性問題會造成信號完整性問題(抖動、電源/接地反彈、EMI)。雖然大多數更簡單的電源完整性指南往往只關注PCB級別,但PCB和封裝必須協同工作才能為互連提供穩定的電源。本指南將嘗試為PCB設計人員提供電源完整性的綜合概念視圖。雖然設計人員通常無法控制其封裝,但他們可以采取措施確保其PCB和元件封裝協同工作以提供穩定的電源。我將概述一些確保這些領域的電源完整性的主要方法,涵蓋從疊層設計到最佳電容器選擇的各個方面。什么決定了PCB中的電源完整性?電源完整性在交流和直流中都是一個概念;在直流情況下,我們關心銅線的尺寸是否合適以確保低直流壓降。如果設計PCB時未考慮電源完整性,在電源軌上觀察到的電壓可能如下圖所示。在I/O切換的階段,從PCB的供電網絡(PDN)拉出的電流脈沖會激發電源總線上的瞬變。邏輯電路重復切換示例如下所示。

發生這種情況的最常見實例是開關速度非常快的高速元件;同時切換更多的I/O會導致更大的功率需求,因此電源軌上可能會有更多噪聲。放大瞬態響應時,瞬態會隨著多個時間常數衰減,其中最主要的是一個長的低頻時間常數,它在電源軌上產生的噪聲最多。通常,當給定PDN結構的信號上升時間更快時,生成的紋波可能具有更大的過沖,或者與更高頻率的欠阻尼振蕩相關的多個時間常數。這些振蕩不可取,原因有兩個:-

它們在輸出信號上顯示為噪聲(包括時序噪聲和信號電平噪聲),可能導致邏輯電平的誤讀

-

它們產生的輻射EMI可以從電路板上測量,通常是從邊緣測量

出于這兩個原因,設計人員必須采取一些措施來確保穩壓器的直流電壓輸出盡可能穩定。PDN阻抗、電感和電容PCB中PDN的阻抗將是電源完整性的主要決定因素。穩壓器也通過其反饋回路發揮作用(參見下文),但設計PDN阻抗是PCB設計人員的工作范圍。目標是盡可能降低PDN阻抗,通常低于100 mOhm水平。PDN阻抗由多個元素的存在決定,如下表所示。

|

元素

|

對電源完整性的影響

|

|

電源和接地層對

|

-

存儲可以釋放的電荷以提供高頻功率

-

確定通向封裝的擴散電感

|

|

離散電容器

|

|

|

電容器封裝和過孔電感

|

-

限制為信號提供電源的電容放電速率

-

確定上方所示的瞬態振蕩頻率

|

|

嵌入式電容

|

|

|

封裝寄生效應

|

|

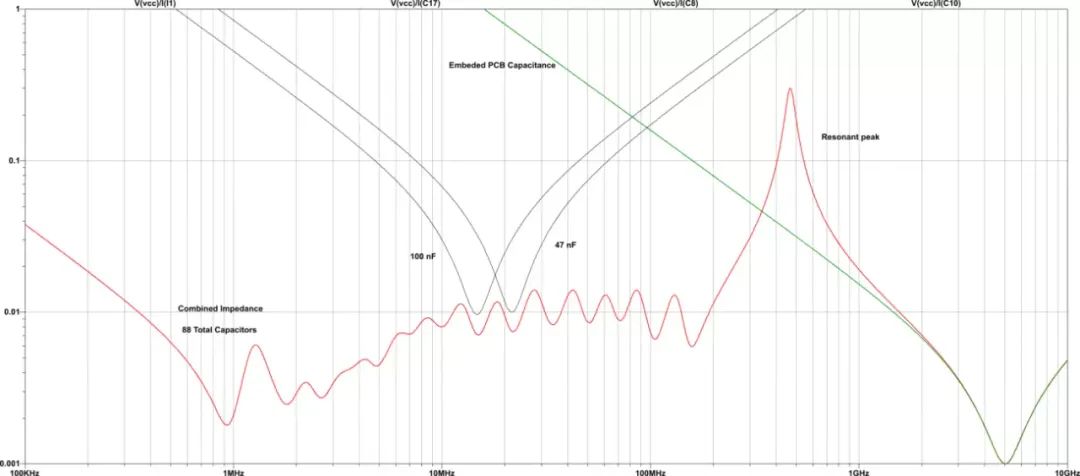

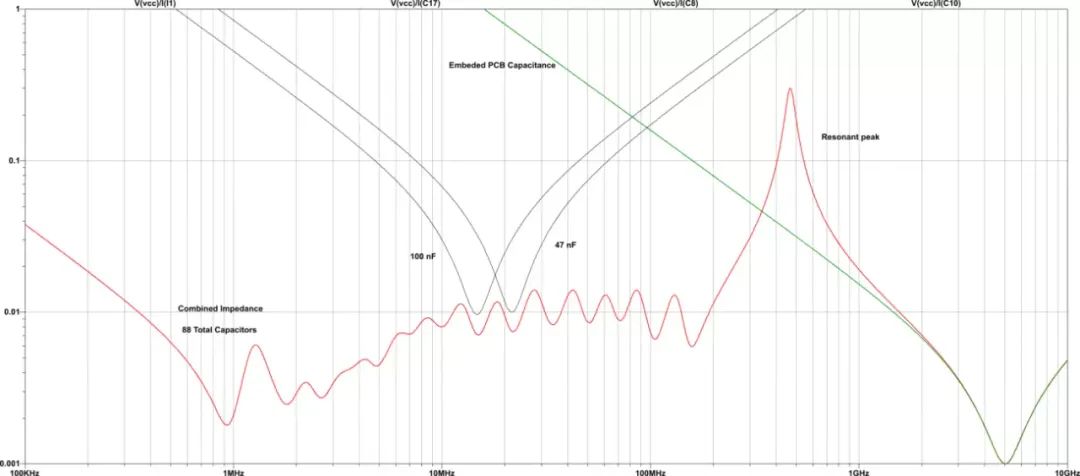

總的來說,這些元素將決定PDN的阻抗頻譜。PDN的各種貢獻因素如下圖所示,這些貢獻大致按頻率范圍劃定。此處顯示的阻抗譜由大量電容器構成,這是以快速邊沿速率運行的、具有高I/O計數的數字處理器的典型特征。

PDN拓撲

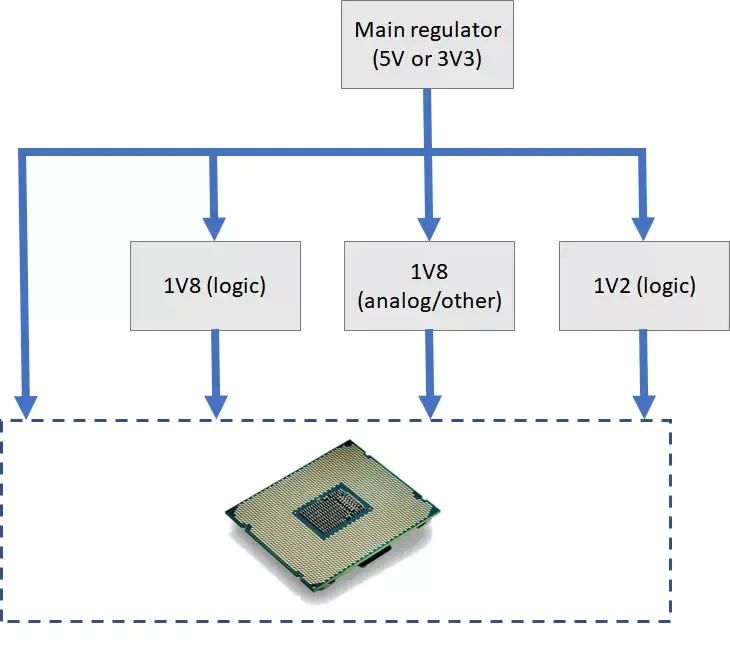

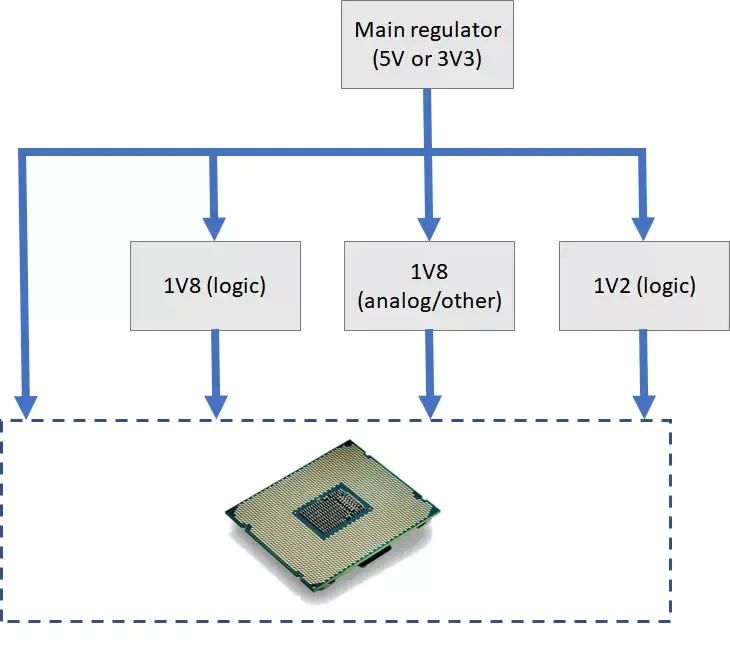

所有為高級處理器供電的PDN都是多端口網絡。它們需要多重穩定電壓,從高值到低邏輯電平。在高引腳數處理器上,電壓從較高邏輯電平(5V0或3V3)下降到低至0V8是很常見的。

定義高級處理器PDN的電源樹如下所示。該示例旨在說明如何構建不同的電源軌,這些軌道來自為整個系統供電的主電源或穩壓器。

處理器的PDN拓撲示例需要四個電壓逐漸降低的不同電源軌

處理器的PDN拓撲示例需要四個電壓逐漸降低的不同電源軌

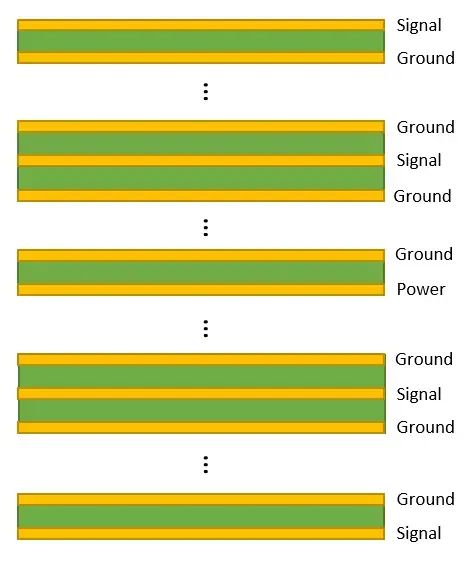

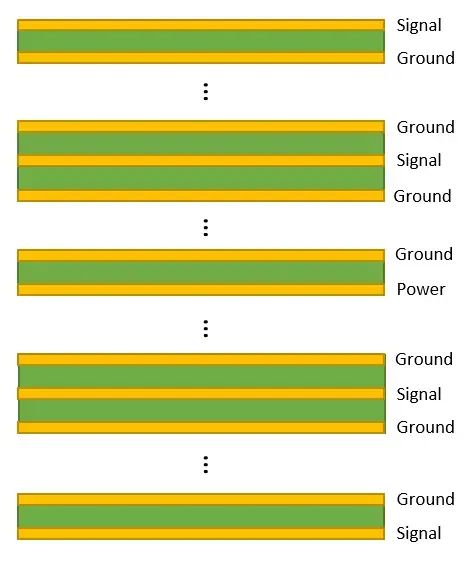

上方示例并非旨在推廣到所有數字元件,但它應該說明許多元件將具備多個電源軌。由上述電源拓撲供電的數字處理器可以是任何類型的元件,例如大型FPGA、網絡處理器、MPU、大型MCU、GPU或其他專用處理器。處理器上的I/O從電源軌獲取電源,因此這些電源軌可能會在PDN中經歷顯著的瞬態噪聲。上方拓撲應該說明了兩個設計要求的必要性:軌道之間的隔離,特別是同一穩壓器提供的兩個不同的軌道,這樣就不會在彼此之間傳遞噪聲。每條軌道還需要具備自己的低阻抗值,以確保任何噪聲激發都很低。印刷電路板疊層和材料在電源完整性方面,PCB疊層中的材料選擇在提供確保穩定供電所需的電容方面起著重要作用。此外,層布置應提供電源軌,以將其放置在薄層上與接地層相鄰的位置。這將有助于確保疊層為信號帶寬高達約1 GHz的信號提供足夠的電容。

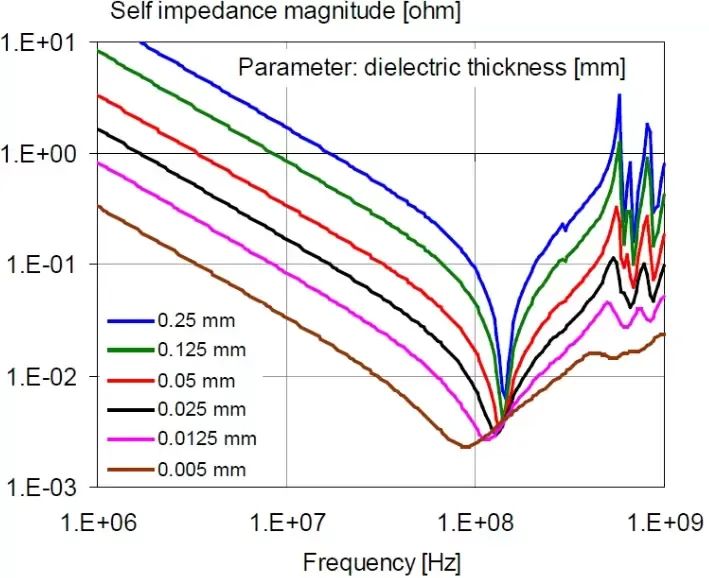

將層分組到更高層數的策略當平面層中的可用電容不足,并且離散電容器受到寄生效應的限制時,可以通過嵌入式電容材料(ECM)提供所需的電容。這些材料是非常薄的薄膜(有些厚度低于1 mil),具有高達30的高Dk值。這些材料還可能具有非常高的損耗,會吸收在PCB基板中傳播的EMI,從而減少從電路板邊緣輻射的EMI。就PDN阻抗而言,這些材料的影響分為四個部分:-

在中檔頻率下提供更高的電容,從而降低阻抗(高達1 GHz)

-

將與電源/接地層對相關的PDN諧振移至較低頻率

-

抑制與電源/接地層對相關的GHz范圍內的PDN諧振峰值

-

將與平面電容相關的PDN阻抗谷值(從0.1到1 GHz)移至較低頻率

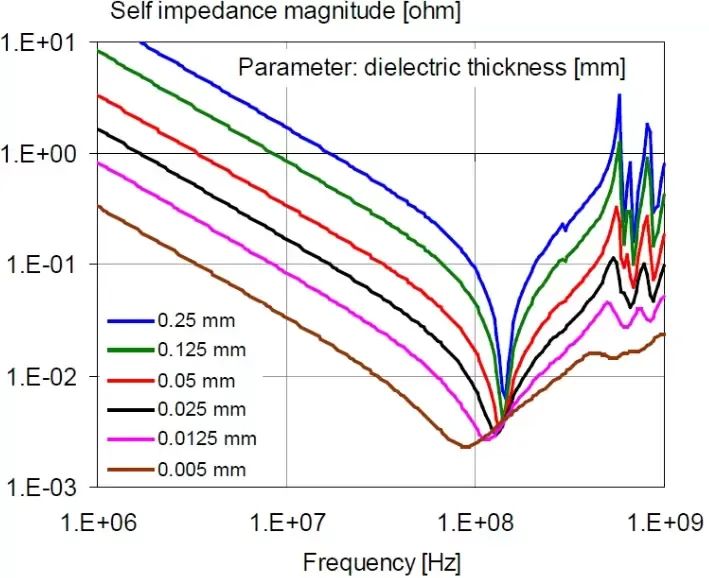

這些材料的效果如下圖所示。隨著電介質厚度的減小,我們可以看到PDN中的諧振峰值會衰減并移至較低頻率。如果我們增加材料中的介電損耗,也可以看到類似的結果。

材料數據顯示,在PCB疊層中使用更薄的ECM時,PDN阻抗會降低。我們可以非常清楚地看到,通過使用更薄的ECM材料,1 GHz附近的共振行為大大降低。[來源:DuPont]封裝寄生效應元件封裝具備與封裝結構相關的自身寄生效應,并且元件封裝具備自身的PDN阻抗。封裝阻抗與PCB阻抗相結合,它們共同決定了半導體芯片上邏輯電路中電源輸入端的噪聲量。現代處理器包括封裝內電容器,以幫助抑制瞬態激發,并將有用的信號帶寬擴展到GHz范圍。不止于PCB和封裝我們涵蓋了PCB和封裝的所有內容,包括高級封裝中一些最復雜的設計特性和模型。PCB設計人員可以控制電路板布局、疊層和布置/布線,并且還可以控制封裝。在功率調節策略方面,我們尚未涉及兩個重要主題:-

用于大型高速處理器的電壓調節器模塊(VRM)

-

原理圖和PCB布局中的模擬

VRM模塊PDN的結構以及許多高級元件需要多個電源軌的事實需要多個穩壓器模塊,它們相互為并聯分支。固定電源穩壓器的作用是補償壓降并通過反饋回路(大多數穩壓器上的FB引腳)維持目標輸出電壓。反饋回路必須作出足夠快的響應并調制輸出,以試圖穩定輸出電壓。影響穩壓器反饋環路響應的因素出現在布局級別和元件級別。VRM的主題及其布局實踐將在本網站的其他位置介紹。除了VRM設計和布局之外,設計人員還應專注于設計正確的疊層和電容器/材料選擇,以確保在其工作帶寬內具有足夠低的PDN阻抗。正如我們上面所討論的,布局和放置也會通過產生寄生效應,從而影響電源完整性。仿真仿真可以在交流或直流中進行,也可以在原理圖或已完成的PCB布局中進行。對于以高達GHz的信號帶寬運行的高速PCB,交流電源完整性仿真最為重要,因為它們可以揭示I/O開始切換時的電源總線紋波。原理圖中的交流仿真是基于SPICE的仿真,可以檢查用于去耦/旁路的電容器網絡的穩定性。這些模型允許估算電源總線響應,以及評估PDN中包含的電容是否足夠。還需要評估由同一穩壓器/VRM供電的不同電源軌之間的隔離性,這可以通過評估傳輸阻抗來確定。交流仿真也可以在PCB布局中執行,但這需要電磁場求解器在給定PCB中PDN結構的情況下預測信號在空間和時間上的行為。這些模擬要求密集的計算,需要專門的軟件。盡管交流模擬在先進產品中很重要,但直流模擬在高速PCB中仍占有一席之地。在這些PCB的主處理器中切換的大量I/O會產生數安培的電流需求。當您使用一塊為多個外圍設備提供服務的超大型高速電路板(如底板)時,您必須在整個系統中支持大約100 A的電流,包括在快速處理器上為I/O供電的電源軌。因此,識別并消除電源軌中的極端電流非常重要。Altium Designer中的CAD工具使每位用戶和工程師都能控制其電源完整性和交付策略。Altium Designer還提供與用于SI、PI和EMI/EMC仿真的前沿應用的集成。當設計完成并準備將文件遞交給制造商時,Altium 365平臺可以輕松地協作并共享您的項目。聲明:

本文轉載自Altium公眾號,如涉及作品內容、版權和其它問題,請于聯系工作人員微(prrox66),我們將在第一時間和您對接刪除處理!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:PCB電源完整性完整指南:從電路板到封裝

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

相關推薦

如今,可以認為大多數PCB存在某種類型的信號完整性問題的風險,這種問題通常與高速數字設計相關。高速PCB設計和布局專注于創建不易受信號完整性、電源

![的頭像]() 發表于

發表于 10-18 14:06

?611次閱讀

高速電路中的信號完整性和電源完整性研究

發表于 09-25 14:44

?0次下載

高速高密度PCB信號完整性與電源完整性研究

發表于 09-25 14:43

?5次下載

高速PCB信號完整性設計與分析

發表于 09-21 11:51

?0次下載

電子發燒友網站提供《高速電路PCB及其電源完整性設計.pdf》資料免費下載

發表于 09-21 11:49

?0次下載

電子發燒友網站提供《超常材料應用于電路板進行電源完整性、信號完整性、電磁兼容性研究.pdf》資料免費下載

發表于 09-20 11:40

?0次下載

電子發燒友網站提供《高速PCB的信號完整性、電源完整性和電磁兼容性研究.pdf》資料免費下載

發表于 09-19 17:37

?0次下載

電子發燒友網站提供《高速PCB電源完整性研究.pdf》資料免費下載

發表于 09-19 17:36

?0次下載

電子發燒友網站提供《高速電路電源分配網絡設計與電源完整性分析.pdf》資料免費下載

發表于 09-19 17:35

?0次下載

電子發燒友網站提供《信號完整性與電源完整性-電源完整性分析.pdf》資料免費下載

發表于 08-12 14:31

?38次下載

電子發燒友網站提供《信號完整性與電源完整性-信號的串擾.pdf》資料免費下載

發表于 08-12 14:27

?0次下載

電子發燒友網站提供《信號完整性與電源完整性 第一章 概論.pdf》資料免費下載

發表于 08-09 14:49

?1次下載

在電子設備的開發和維護過程中,電源完整性是一個至關重要的考量因素。電源完整性(Power Integrity, PI)涉及到

![的頭像]() 發表于

發表于 08-02 09:38

?265次閱讀

? 在現代電子設備的設計中,一個關鍵的因素是電源完整性。電源完整性不僅影響設備的性能,還直接關系到設備的穩定性和可靠性。作為電子設備的基礎,

![的頭像]() 發表于

發表于 06-13 18:16

?2835次閱讀

在現代電子設備的設計中,一個關鍵的因素是電源完整性。電源完整性不僅影響設備的性能,還直接關系到設備的穩定性和可靠性。作為電子設備的基礎,印

發表于 06-12 15:21

處理器的PDN拓撲示例需要四個電壓逐漸降低的不同電源軌

處理器的PDN拓撲示例需要四個電壓逐漸降低的不同電源軌

PCB電源完整性完整指南:從電路板到封裝

PCB電源完整性完整指南:從電路板到封裝

評論