Q1

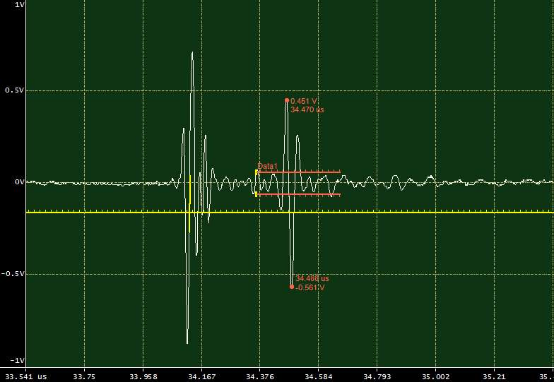

圖中這個(gè)分層是哪里導(dǎo)致的?

A1

die attach,銀漿分層,最好有個(gè)reference對(duì)比判斷,看起來(lái)die attach的波幅太大了,找根因還是需要FA看看細(xì)節(jié)。

Q2

在芯片設(shè)計(jì)階段,如何計(jì)算芯片內(nèi)部自研IP模塊的FIT的數(shù)值呢?

A2

在設(shè)計(jì)功能安全芯片的過(guò)程中計(jì)算硬件架構(gòu)度量(SPFM,LFM,PMHF)中一般是根據(jù)IEC TR62380或是SN 29500等標(biāo)準(zhǔn)計(jì)算芯片總的failure rate,然后將failure rate分配到各功能模塊,在配合各功能安全模塊的診斷覆蓋率計(jì)算芯片SPFM,LFM,PMHF。以確定芯片這幾項(xiàng)指標(biāo)是否達(dá)到對(duì)應(yīng)ASIL等級(jí)要求,如果這幾項(xiàng)指標(biāo)不達(dá)標(biāo),說(shuō)明芯片安全機(jī)制診斷覆蓋率不夠,芯片的架構(gòu)設(shè)計(jì)需要繼續(xù)優(yōu)化。IEC TR62380是根據(jù)統(tǒng)計(jì)匯總出來(lái)的Mission profiles,建立一個(gè)由關(guān)于溫度π(t),溫差ΔT,芯片材料膨脹系數(shù)π(α)等因子組成的推測(cè)產(chǎn)品failure rate 的統(tǒng)計(jì)模型。

Q3

芯片裂紋、崩邊的規(guī)定出自哪份jedec標(biāo)準(zhǔn)?

A3

JEDEC Standard No.22-B118A。

Q4

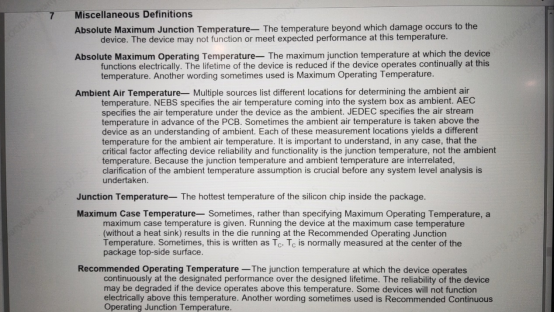

TJ-max(recommended) 和TJ-max(absolute)的區(qū)別是什么?

A4

TJ的解釋。

Q5

怎么確定這兩個(gè)溫度呢,比如常規(guī)CMOS工藝,一般我們做可靠性都是Tj>125℃的。很多datasheet上只有一個(gè)TJ max是125℃,沒(méi)有特別說(shuō)是recommended還是absolute?

A5

absolute問(wèn)fab和你們的DE;recommend要看你們?cè)趺唇o客戶規(guī)定了,也許產(chǎn)品能力有150℃,但data sheet只推薦125℃。

Q6

封裝可靠性的TCT700,F(xiàn)T回測(cè)發(fā)現(xiàn)出現(xiàn)了兩種失效,一種是內(nèi)部數(shù)字電路邏輯失效了,另一種是電源的漏電變大了很多,這種怎么分析呀?

A6

看看是否有濕氣進(jìn)去造成漏電變大,做下SAT看看是否有分層造成邏輯失效,TCT評(píng)估封裝的,主要和封裝相關(guān);可以烤一烤試試,或者清潔一下管腳,可能是接觸電阻變大了。

Q7

為什么CUP芯片打線建議要用銀合金,鍍鈀銅不建議用,是芯片pad架構(gòu)跟常規(guī)芯片不一樣嗎?有沒(méi)有知道詳細(xì)些的?

A7

CUP芯片不允許有裂紋,合金線和金線軟一點(diǎn),作業(yè)性好一點(diǎn);銅線力大,版圖不合理的話焊球下方容易出現(xiàn)裂紋;芯片打線實(shí)際上是,共金工藝,使用了高溫+超聲波,達(dá)到融焊的效果,這樣的話芯片受壓力小,不容易破裂。所以對(duì)線材有要求,銅打線一般是壓焊工藝,壓力大,對(duì)于以前一些老工藝低成本的芯片可以用,但是芯片表面的PAD處理方式和金打線是不同的。不同的打線方式用不同的線材,這些芯片設(shè)計(jì)初期就要和晶圓廠溝通好,把后期封裝打線方式都要考慮進(jìn)去。

Q8

什么樣的芯片出貨使用卷帶包裝,什么樣的該采用Tray盤出貨,有沒(méi)有什么規(guī)定的?

A8

QFP類的一般都是TRAY盤,SOP類的料管和卷帶都有,DFN/QFN這類無(wú)外放引腳的看體積,卷帶居多,5X5以上可以用TRAY盤,主要是太重,轉(zhuǎn)塔式的測(cè)編吸不住。

Q9

現(xiàn)在一般的SMT,卷帶上料和Tray盤上料是否都能支持的?Tray盤交貨是否影響SMT的上料?

A9

對(duì)于SMT來(lái)說(shuō),卷帶是效率最高的,能用卷帶肯定優(yōu)先用,實(shí)在沒(méi)有才考慮其他方式。料管和TRAY盤設(shè)備方面都能支持,但要看工廠是否會(huì)配齊硬件。

Q10

消費(fèi)類芯片工規(guī)的可靠性測(cè)試標(biāo)準(zhǔn),HAST是必做項(xiàng)嗎?

A10

HTOL、HAST目前都是必做項(xiàng)。

Q11

盛裝芯片的tray盤,其表面阻抗范圍是否有標(biāo)準(zhǔn)?

A11

10的9次方以下。

Q12

wafer超期需要做哪些驗(yàn)證?

A12

做MSL3看看有沒(méi)有分層,也可以做快速ORT IR*3+UHAST48+TC100。

Q13

通常wafer在氮?dú)夤裰斜4娑嗑煤螅瑫?huì)認(rèn)為是超期呢?

A13

general是3年的shelf life,自家產(chǎn)品可以和foundry再確認(rèn)下。

Q14

關(guān)于ESD的驗(yàn)證,HBM、CDM、MM要怎么樣去分解安排實(shí)驗(yàn)?zāi)兀?/p>

A14

JEDEC規(guī)范經(jīng)過(guò)更新,已經(jīng)明文說(shuō)明MM模式已經(jīng)能被CDM、HBM等覆蓋,不需額外測(cè)MM。MM主要是在生產(chǎn)過(guò)程中的機(jī)械靜電對(duì)芯片的直接放電傷害,中間沒(méi)有電阻限流,所以通過(guò)電壓值低于CDM、HBM。但是車規(guī)和其它特殊可靠性需求,部分客戶還是有測(cè)MM的需求。

Q15

JEDEC中HBM和Latch up的判定條件僅僅是I/V的變化率嗎?對(duì)功能測(cè)試有要求嗎?

A15

Q16

對(duì)于已經(jīng)塑封好的DFN產(chǎn)品,有什么方法可以使某一個(gè)Pin腳和中間的基島相連接么?

A16

找季豐局部開(kāi)蓋,焊線連上,然后黑膠封上。

Q17

Thermal熱點(diǎn)和OBIRCH熱點(diǎn)分別適用哪種情況?缺陷漏電大于2mA是不是兩種方式都能用?

A17

有compound用thermal,沒(méi)有compound兩種都可以。OBIRCH原理:激光束在IC表面掃描,激光束的部分能量被IC吸收轉(zhuǎn)化為熱量,造成被掃瞄區(qū)域溫度變化,若IC金屬互聯(lián)機(jī)中存在缺陷或者空洞,這些區(qū)域附近的熱量傳導(dǎo)不同于其它的完整區(qū)域,則該區(qū)引起的溫度變化會(huì)不同,從而造成金屬電阻值改變。Thermal原理:利用InSb材質(zhì)的探測(cè)器,接收失效點(diǎn)通電后產(chǎn)生的熱輻射分布,藉此定位失效點(diǎn)位置。適應(yīng)范圍:漏電,高阻抗,短路OBIRCH,Thermal都可以定位,其中帶封裝的樣品/電容漏電短路/PCB板失效的使用Thermal定位,小電壓漏電,小漏電優(yōu)先使用OBIRCH定位。

Q18

封裝銅線打線產(chǎn)品,線經(jīng)約粗50um左右,大部分是裸銅線居多還是鈀銅或者金鈀銅線多?若是裸銅,原因是什么呢,沒(méi)有Pd的話IMC不是會(huì)生長(zhǎng)過(guò)快么?

A18

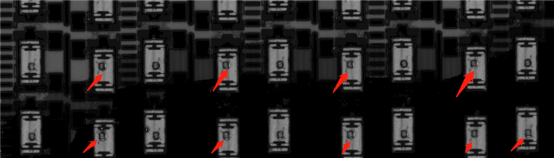

純銅線只有價(jià)格優(yōu)勢(shì)的吧,鍍金和鈀主要還是為防止FAB氧化和一致性,提高焊接強(qiáng)度和CPK。鍍鈀應(yīng)該是可以減緩IMC生長(zhǎng)的,這點(diǎn)可以參考鍍鈀金線,因?yàn)榻鸷弯X更容易共金;不過(guò)使用純銅線除了IMC還會(huì)有各種其他可靠性行問(wèn)題,潮濕酸性環(huán)境也扛不住。銅鋁imc只有在150度以上高溫才會(huì)快速生長(zhǎng),這是我們1000小時(shí)HTOL后的IMC生產(chǎn)情況,只有薄薄一層,用的是金鈀銅,參考如下:

Q19

先進(jìn)制程中,這個(gè)操作電壓下降,為何熱載流子的光波長(zhǎng)變得較長(zhǎng)?這個(gè)怎么理解呢?

A19

這個(gè)應(yīng)該這么理解,電壓下降熱載流子能量降低,光子能量(eV)*波長(zhǎng)(nm)=1240;這個(gè)是光頻率里面的,跟射頻頻率不同。

審核編輯:彭菁

-

芯片

+關(guān)注

關(guān)注

454文章

50430瀏覽量

421863 -

模塊

+關(guān)注

關(guān)注

7文章

2672瀏覽量

47342 -

射頻

+關(guān)注

關(guān)注

104文章

5551瀏覽量

167557 -

計(jì)算

+關(guān)注

關(guān)注

2文章

445瀏覽量

38737 -

Fit

+關(guān)注

關(guān)注

0文章

15瀏覽量

9302

原文標(biāo)題:季豐電子IC運(yùn)營(yíng)工程技術(shù)知乎 – 23W30

文章出處:【微信號(hào):zzz9970814,微信公眾號(hào):上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

蘋果自研5G芯片或于明年亮相

蘋果加速自研芯片進(jìn)程,iPhone SE 4將首發(fā)自研5G基帶

比亞迪最快于11月實(shí)現(xiàn)自研算法量產(chǎn),推進(jìn)智駕芯片自研進(jìn)程

蘋果自研Wi-Fi芯片或明年商用,用于部分iPad

小鵬自研智駕芯片:面向L4+AI大模型,集成40核+NPU+ISP

消息稱小鵬汽車自研智駕芯片流片成功

三星電子內(nèi)部或自研XR設(shè)備專用芯片

國(guó)產(chǎn)車企自研智駕芯片加速落地,蔚來(lái)小鵬等領(lǐng)跑賽道

大廠自研芯片背后的贏家,不只有晶圓廠

蘋果計(jì)劃搭建自研芯片驅(qū)動(dòng)的AI數(shù)據(jù)中心

車企自研功率模塊加速落地,國(guó)產(chǎn)SiC MOSFET和代工廠迎新機(jī)會(huì)

微軟正在研發(fā)新型網(wǎng)卡,旨在提升自研AI芯片性能

英偉達(dá)缺貨?OpenAI選擇自研芯片

蘋果自研Wi-Fi芯片之路充滿挑戰(zhàn)

知行科技全棧自研iDC,向著整車中央計(jì)算機(jī)發(fā)展

如何計(jì)算芯片內(nèi)部自研IP模塊的FIT的數(shù)值

如何計(jì)算芯片內(nèi)部自研IP模塊的FIT的數(shù)值

評(píng)論