NAND閃存工藝

閃存芯片是非揮發存儲芯片,廣泛用于電子產品,特別是如數碼相機、MP3播放器、手機、全球定位系統(GPS)、高端筆記本電腦和平板電腦等移動電子產品的存儲應用。與磁性硬盤存儲器相比,閃存的數據存取時間短,消耗的功率較少,而且因為沒有任何移動部件,所以可靠性更高。

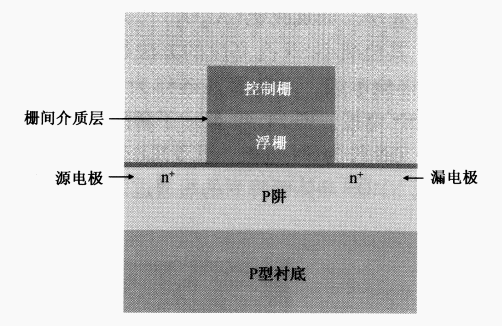

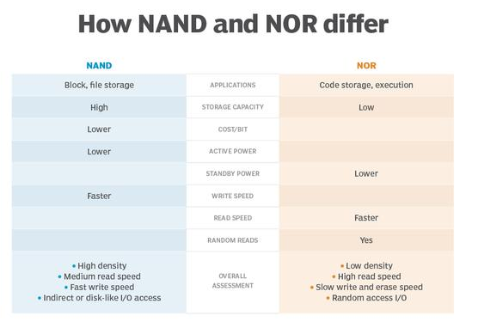

所有市場上的閃存芯片都是基于浮柵結構的電荷俘獲器件,這種結構已經在后面的部分討論過。下圖顯示了浮柵器件結構,這種結構與NMOS類似。根據不同的電路結構,有兩種類型的閃存器件——NAND和NOR(見下圖)。

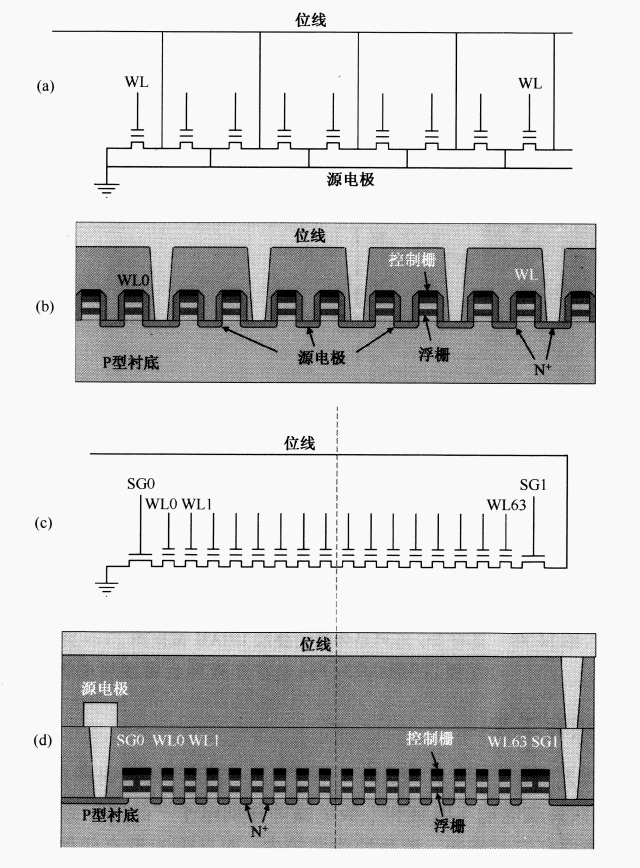

下圖(a)和(b)分別顯示了NOR閃存電路和橫截面示意圖。下圖(c)和(d)為64位NAND快閃存儲電路和相應的截面圖。可以看出,一個NOR閃存等效于1位字符NAND快閃存儲器,這種結構不需要選擇柵。雖然NOR閃存比NAND快閃存儲器的讀取時間短,然而它具有更長的寫入時間和擦除時間。由于低的封裝密度,NOR閃存比NAND快閃存儲器價格高。大多數快閃存儲器芯片是NAND芯片,本節只討論NAND快閃存儲器的工藝流程。

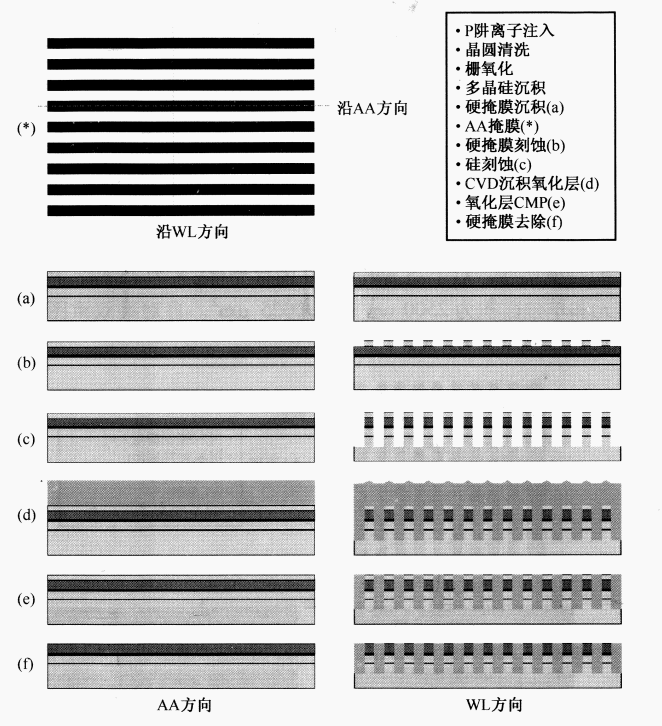

下圖顯示了自對準淺溝槽隔離(SA-STI)工藝流程。P阱離子注入后,生長柵氧化層并利用硬掩膜層沉積浮柵,使用AA版圖圖形化硬掩膜,然后刻蝕浮柵、柵氧化層和硅襯底形成AA圖形化。氮化硅或氮氧化硅是最常使用的硬掩膜材料,多晶硅是最常使用的浮柵材料。硅溝槽刻蝕后,使用高密度等離子體CVD沉積氧化層填充溝槽,利用CMP工藝去除氧化物并停止于硬掩膜層。最后通過剝離工藝去除硬掩膜后完成SA-STI過程。

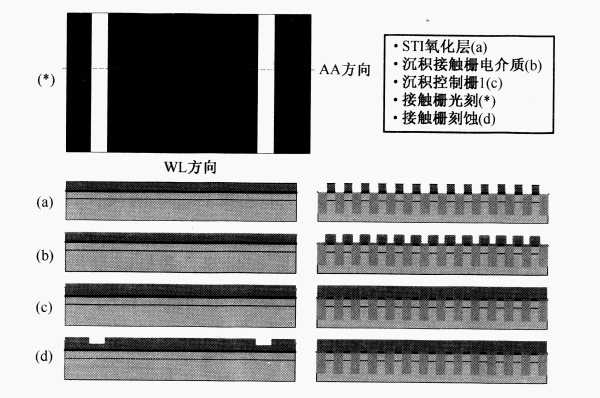

下圖顯示了內部柵接觸的工藝過程。這是浮柵NVM器件特有的工藝,因為選擇柵MOSFET及外圍區域的控制電路沒有浮柵器件,需要內部柵將浮柵層和控制柵層連接起來。一般情況下浮柵利用多晶硅制成,內部柵介質是氧化物-氮化物-氧化物(oNo)疊層結構,控制柵的第一層也是多晶硅,第二層通常是金屬,如硅化鎢或鎢等。下圖(a)所示的STI氧化物可以使得控制柵和浮柵同步增加,當特征尺寸不斷縮小時,這種情況是不可避免的。

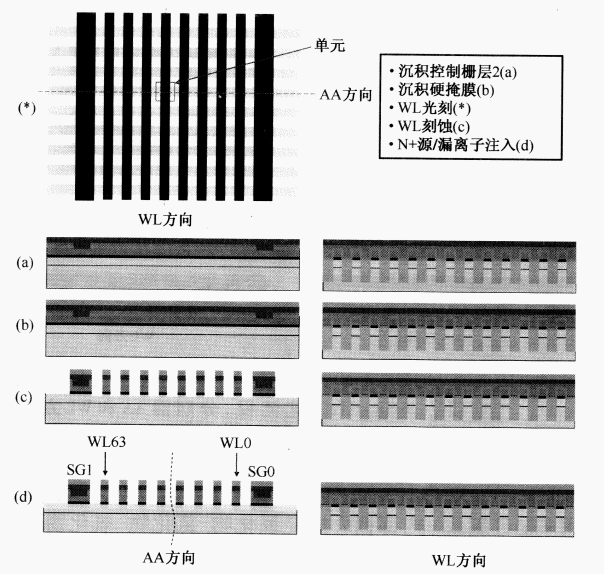

在下面的圖中非常詳細的顯示了WL工藝流程。通過連接浮柵和控制柵的內部柵接觸沉積金屬,所有的MOSFET柵極位于外圍區域。WL層的密集線/圖形間距具有IC產品最高的集成度。在下面的圖中所示AA版圖中的方塊NAND快閃存儲器單元區域可以表示為4F2,F表示結構的最小特征尺寸,4F2是可以達到的最高圖形密度。對于NAND快閃存儲器,AA和WL線/間距比為1:1,因此F是AA和WL的特征尺寸對于25nmNAND閃存器件,F為25nm,其中AA和WL的CD為25nm,存儲單元和單位面積為2500nm或0.0025um2。自對準雙重圖形技術適用于圖形化WL層,也可以應用于AA和BL層。

審核編輯:劉清

-

MOSFET

+關注

關注

146文章

7101瀏覽量

212777 -

存儲器

+關注

關注

38文章

7455瀏覽量

163623 -

閃存芯片

+關注

關注

1文章

119瀏覽量

19594 -

CMP

+關注

關注

6文章

142瀏覽量

25949 -

NAND芯片

+關注

關注

0文章

23瀏覽量

10040

原文標題:半導體行業(二百零四)之ICT技術(十四)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

3D工藝的轉型步伐較慢,NAND閃存依然處于供給吃緊的狀態

關于不同NAND閃存的種類對比淺析

你知道NAND閃存的種類和對比?

東芝推出第二代工藝技術 采用新型嵌入式NAND閃存模塊

閃迪宣布投產新工藝的NAND閃存芯片

解析NAND閃存和NOR閃存

NAND閃存芯片有哪些類型

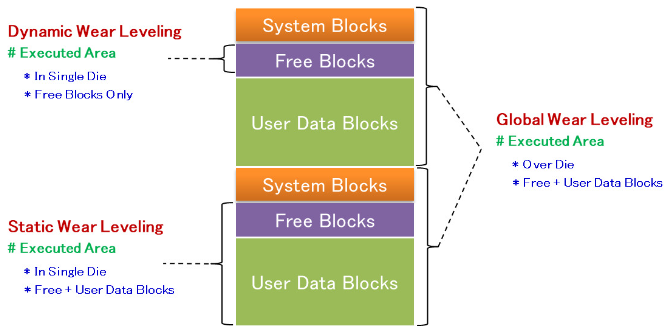

NAND閃存的應用中的磨損均衡

淺析NAND閃存工藝

淺析NAND閃存工藝

評論