今天來看下SpinalHDL Pipeline組件里的resulting及overloaded的使用

》resulting

在Stage中的數據結構中,有四種類型:

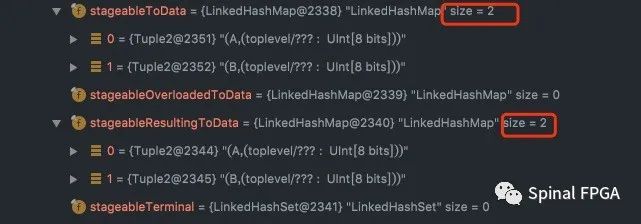

val stageableToData = mutable.LinkedHashMap[StageableKey, Data]() val stageableOverloadedToData = mutable.LinkedHashMap[StageableKey, Data]() val stageableResultingToData = mutable.LinkedHashMap[StageableKey, Data]() val stageableTerminal = mutable.LinkedHashSet[StageableKey]()

關于stageableToData,在之前的文章中已有介紹,今天來看下stageableOverloadedToData以及stageableResultingToData的作用。在提供的API中,相關的注冊函數有:

stageableOverloadedToData注冊:

defoverloaded(key : StageableKey):Data = {

internals.stageableOverloadedToData.getOrElseUpdate(key, ContextSwapper.outsideCondScope{

key.stageable()//.setCompositeName(this, s"${key}_overloaded")

})

}

stageableResultingToData注冊:

def resulting(key : StageableKey) : Data = {

internals.stageableResultingToData.getOrElseUpdate(key, ContextSwapper.outsideCondScope{

key.stageable()//.setCompositeName(this, s"${key}_overloaded")

})

}

def resulting[T <: Data](key : Stageable[T]) : T = {

????resulting(StageableKey(key.asInstanceOf[Stageable[Data]], null)).asInstanceOf[T]

??}

def resulting[T <: Data](key : Stageable[T], key2 : Any) : T = {

????resulting(StageableKey(key.asInstanceOf[Stageable[Data]], key2)).asInstanceOf[T]

}

字如其名,resulting可以理解為獲取Stageable的最終結果,而overload則是對數據的重載。不妨先來看看在pipeline中這兩種類型所起的作用:

在pipeline的build函數里,對于stageableResultingToData,其首先的處理方式代碼如下:

for(s <- stagesSet){

???for(key <- s.internals.stageableResultingToData.keys){

?????s.apply(key)

???}

}

這里對于每個stage中stageableResultingToData里所注冊的每種類型StageableKey,其都會調用Stage的apply函數將其注冊到StageableToData中,也就意味著如果前級也有該對應的StageableKey,那么在連接階段兩者是可以建立連接關系的。

隨后,在internal conntection階段,對于stageableResultingToData中的變量,采用的賦值邏輯為:

for((key, value) <-?s.internals.stageableResultingToData){

???value := s.internals.outputOf(key)

}

而outputOf的賦值邏輯為:

def outputOf(key : StageableKey) = stageableOverloadedToData.get(key) match {

caseSome(x) => x

caseNone => stageableToData(key)

}

可以看出,這里的處理方式為,如果該變量在stageableOverloadedToData中存在,那么會將stageableOverloadedToData中的值賦值驅動stageableResultingToData中對應的變量,否則將會從stageableToData中尋找對應的變量進行驅動(上一步已經將對應的StageableKey注冊進stageableToData中)。

》Show Me The Code

分析完了源代碼,上一個簡單的example:

caseclassTest3() extendsComponent{

val io=newBundle{

val data_in=slave(Flow(Vec(UInt(8bits),4)))

val data_out=master(Flow(UInt(8bits)))

}

noIoPrefix()

val A,B=Stageable(UInt(8bits))

val pip=newPipeline{

val stage0=newStage{

this.internals.input.valid:=io.data_in.valid

A:=io.data_in.payload(0)+io.data_in.payload(1)

B:=io.data_in.payload(2)+io.data_in.payload(3)

}

val stage1=newStage(Connection.M2S()){

io.data_out.payload:=resulting(A)+resulting(B)

io.data_out.valid:=this.internals.output.valid

}

}

pip.build()

}

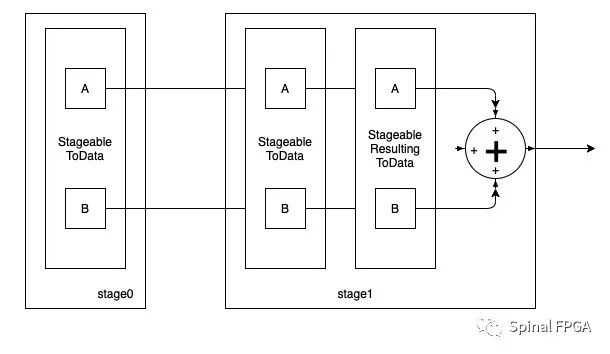

在這個例子里,在stage1中僅用到了resulting語句。按前面所述,stage1中最終stageableResultingToData中會包含兩個變量,build階段也會向其stageableToData階段注冊兩個變量A、B:

在這里,由于stage0中也包含A、B,故這里最終的驅動關系為:

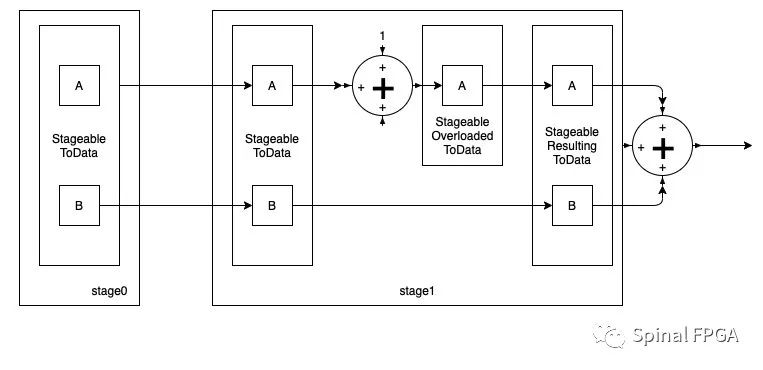

再來看一個resulting和overlaoded共用的代碼:

caseclass Test4() extends Component{

val io=newBundle{

val data_in=slave(Flow(Vec(UInt(8bits),4)))

val data_out=master(Flow(UInt(8bits)))

}

noIoPrefix()

val A,B=Stageable(UInt(8bits))

val pip=newPipeline{

val stage0=newStage{

this.internals.input.valid:=io.data_in.valid

A:=io.data_in.payload(0)+io.data_in.payload(1)

B:=io.data_in.payload(2)+io.data_in.payload(3)

}

val stage1=newStage(Connection.M2S()){

io.data_out.payload:=resulting(A)+B

io.data_out.valid:=this.internals.output.valid

overloaded(A):=A+1

}

}

pip.build()

}

這里在stage1中對A調用了overloaded重載,結合上面的賦值順序,最終的驅動關系為:

看到這里,可能會有一個疑問:為什么不能直接寫成A:=A+1的形式呢?主要在于A本身處于StageableToData,在進行Stage之間的連接時已經對齊進行賦值驅動,這里如果直接寫成A:=A+1相當于對電路進行重復驅動,從而導致報錯。

》總結

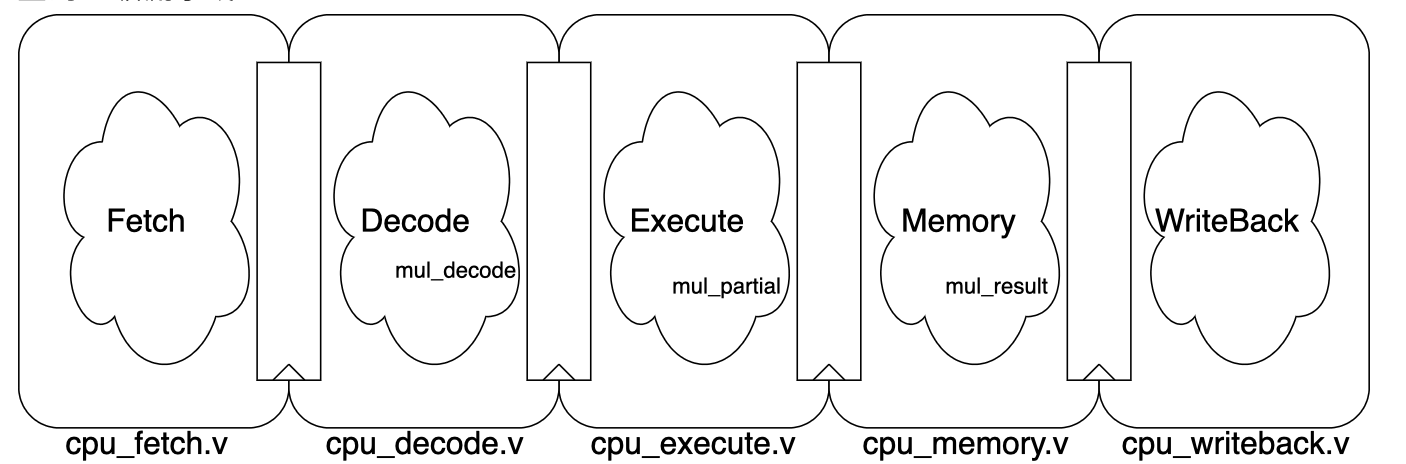

resulting&overloaded主要用于在某個Stage階段對電路在結合上一Stage基礎上需做一些額外判斷對該階段的相應電路做新的賦值驅動時進行處理。如在NaxRsicV中Cache里的一些電路處理:

overloaded(BANK_BUSY)(bankId) := BANK_BUSY(bankId) || bank.write.valid && REDO_ON_DATA_HAZARD

在流水線的某一階段在保持Stageable語義而不必新增Stageable情況下通過overlaoded、resulting來進行Stage內的電路對象驅動。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19160瀏覽量

229115 -

驅動器

+關注

關注

52文章

8155瀏覽量

145999 -

Pipeline

+關注

關注

0文章

28瀏覽量

9345 -

HDL語言

+關注

關注

0文章

46瀏覽量

8909 -

cache技術

+關注

關注

0文章

41瀏覽量

1047

原文標題:pipeline高端玩法(六)—resulting&overloaded

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在SpinalHDL里switch方法有何用處呢

在SpinalHDL里實現優雅的添加待跟蹤波形信號

談談SpinalHDL中StreamCCByToggle組件設計不足的地方

在SpinalHDL中關于casez的使用

分享一個在SpinalHDL里apply的有趣用法

SpinalHDL是如何讓仿真跑起來的

如何在SpinalHDL里啟動一個仿真

SpinalHDL里時鐘域中的定制與命名

SpinalHDL里用于跨時鐘域處理的一些手段方法

SpinalHDL運行VCS+Vivado相關仿真

SpinalHDL里如何實現Sobel邊緣檢測

SpinalHDL里pipeline的設計思路

怎樣使用SpinalHDL Pipeline組件里的resulting及overloaded?

怎樣使用SpinalHDL Pipeline組件里的resulting及overloaded?

評論