本篇文章將講述如何在Cadence IC中使用ADE GXL對電路進行優化設計。

按照慣例,首先講述一下大致的操作流程:

詳細步驟

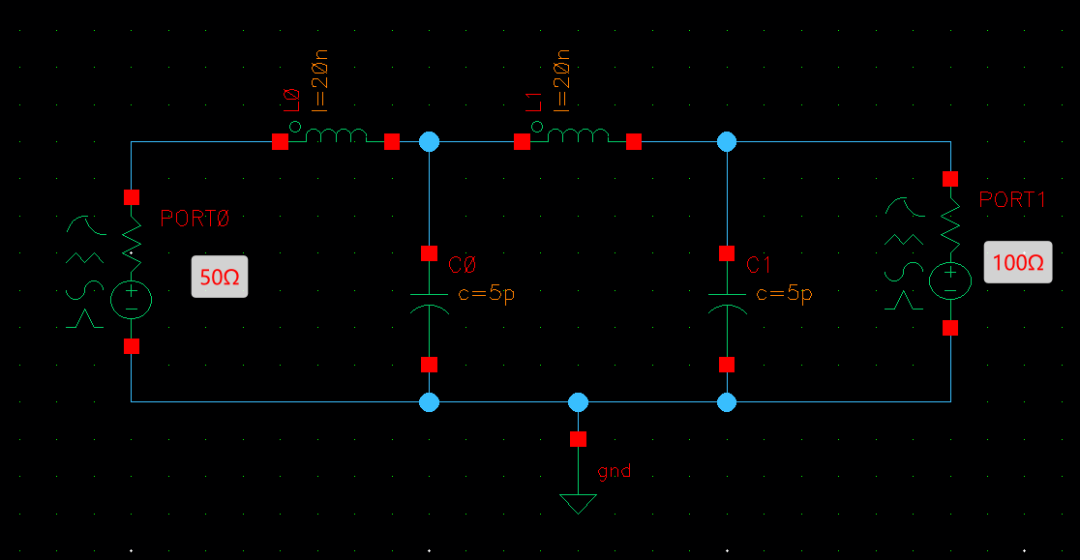

這次優化的例子是一個阻抗匹配電路,50Ω到100Ω,用電感和電容網絡進行匹配。

使用analogLib中的元件搭建電路圖,兩個PORT的阻抗分別設置為50Ω和100Ω,匹配網絡的具體參數如下:

初始電路(未匹配)

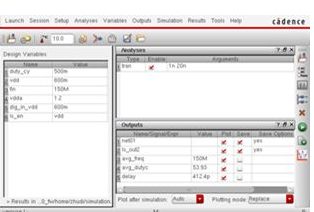

運行仿真(Launch>ADE L),運行S參數仿真,頻率為100M-500M,僅查看S11參數,設置如下(注意保存仿真設置):

仿真設置

運行仿真后發現S11在部分范圍大于-10dB,說明匹配效果不好(這里以小于-10dB表示匹配良好),需要修改參數。

初始電路仿真后的S11

要對電路進行優化,在原理圖編輯窗口中打開ADE GXL。

打開ADE GXL

打開后顯示歡迎界面,在Outputs處點擊鏈接以打開Outputs Setup標簽。之后添加Tests。

添加Tests

在ADE L窗口中加載剛才保存的仿真設置,Outputs Setup標簽自動添加優化目標參數。

添加優化目標參數

接下來需要設置優化目標參數的目標值,在Details欄中修改剛剛導入的目標參數為ymax(db(spm('sp 1 1))),這是因為目標參數不能是波形,必須是點,所以修改為S11的最大值,在spec欄中選擇<-10,Weight表示權重,這里填寫1.這些設置表示優化目標是 S11的最大值小于-10dB。

設置優化目標

通過上圖所示標號4添加要優化的元件參數。

創建參數

設置參數的范圍

修改參數的范圍

選擇Global Optimization,設置參考態。對電路進行優化需要設置一個參考態,目的是給優化提供一個起始狀態。

設置參考態

點擊綠色按鈕運行優化,當達到要求后會自動停止。

優化完成

可以右擊某一參數點擊Backannotate將參數值返回到原理圖。

優化后的電路

對優化后的電路進行仿真,發現達到要求(在目標頻段內均小于-10dB)。

最終仿真結果

說明:

- 本例子在Cadence IC618上完成,不同版本可能有差異。

- 電路優化過程相比ADS比較慢。

-

IC

+關注

關注

36文章

5906瀏覽量

175244 -

電路設計

+關注

關注

6665文章

2430瀏覽量

203361 -

Cadence

+關注

關注

64文章

915瀏覽量

141883 -

仿真

+關注

關注

50文章

4044瀏覽量

133423 -

ade

+關注

關注

0文章

29瀏覽量

15445

發布評論請先 登錄

相關推薦

ALLEGRO PCB SI GXL

基于Cadence的IC設計

ADE7752/ADE7752A具有脈沖輸出的多相電能計量ic

ADE7854/ADE7858/ADE7868/ADE7878:集成諧波和基波信息的多相多功能電能計量IC

ADE5166/ADE5169/ADE5566/ADE5569:帶8052 MCU、RTC和LCD驅動器數據表的單相電能測量IC

ADE7854A/ADE7858A/ADE7868A/ADE7878A:多相多功能電能計量IC數據表

UG-545:評估ADE7854A/ADE7858A/ADE7868A/ADE7878A電能計量IC

在Cadence IC中使用ADE GXL優化電路設計

在Cadence IC中使用ADE GXL優化電路設計

評論