模塊雖小但是要有新意,首先寫一個同步FIFO,這是一個爛大街的入門級項目,但是我肯定不會寫的那么簡單,需求如下:

和大多數文章所寫描述的同步FIFO的需求不一樣的地方在于最后一個需求,內部例化的sram的讀取動作不是讀及讀出的操作。因此基于這種sram,又要兼顧FIFO的標準協議,以及需要FIFO邏輯速度到達最優,需要對設計進行一些小的處理

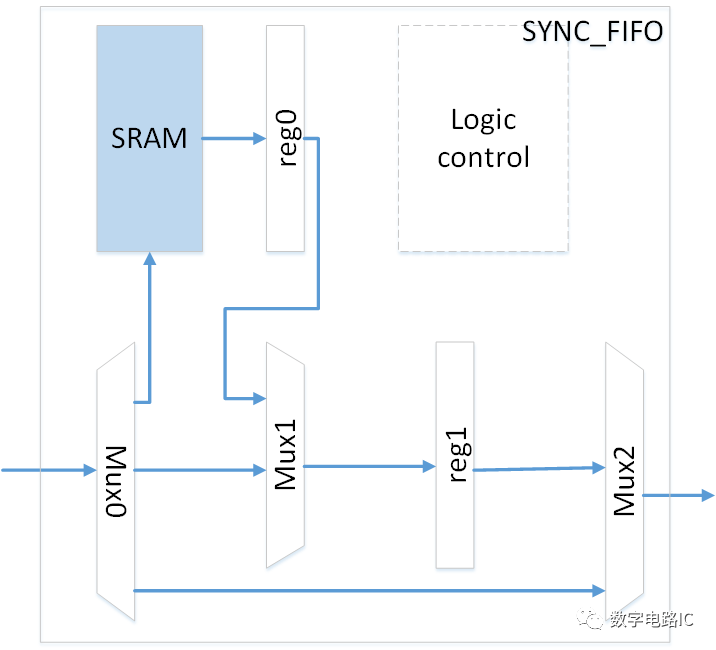

下圖為本次同步FIFO設計的框圖:

設計分析:

- 使用reg0的原因

由于sram延時一拍讀出,因此就需要有reg0處理延時,既只要reg0為空,寄存器就向sram讀數,達到提前取數,消除延時的效果。(一般sram有幾拍延時就有幾個reg0) - 使用reg1的原因

reg1用于處理邊界條件,在sram和reg0為空時,沒有讀使能的情況下寫入第一個數,此時第一個數如果存入sram,則讀取流程將變成sram-reg0-output,中間延遲過長,但是假如使用reg1用于存儲第一個數據,則可以把這一拍數據延時解決掉。(且同上述,一般有幾個reg0就有幾個reg1) - 使用mux2的原因

mux2也是用于處理邊界條件,在sram和所有寄存器都為空時,寫使能和讀使能同時來到,則數據bypass通過SYNC_FIFO模塊。 - mux0和mux1則用于處理上述邏輯關于數據通道切換的處理。

- 關于sram存取、各種空滿信號的判斷,就不再一一敘述,想了解這方面設計可以參見網上各種同步FIFO設計。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5317瀏覽量

120003 -

sram

+關注

關注

6文章

763瀏覽量

114633 -

fifo

+關注

關注

3文章

387瀏覽量

43548 -

同步FIFO

+關注

關注

0文章

5瀏覽量

5340 -

FIFO設計

+關注

關注

0文章

7瀏覽量

4962

發布評論請先 登錄

相關推薦

同步FIFO設計詳解及代碼分享

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

發表于 06-27 10:24

?2023次閱讀

可靠性設計分析系統

要求,需要按照可靠性工作要求開展各種各樣的可靠性設計分析工作。其實,這些可靠性工作,目的解決產品可靠性工程問題,嚴格控制和降低產品質量風險。最近,看到有一個可靠性設計分析系統PosVim,功能還比較

發表于 12-08 10:47

異步FIFO的設計分析及詳細代碼

本文首先對異步 FIFO 設計的重點難點進行分析,最后給出詳細代碼。 一、FIFO簡單講解 FIFO的本質是RAM, 先進先出 重要參數:fifo

發表于 11-15 12:52

?8565次閱讀

FIFO設計—同步FIFO

FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

發表于 05-26 16:12

?1488次閱讀

一個簡單的RTL同步FIFO設計

FIFO 是FPGA設計中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機制,是設計人員將數據從一個模塊傳輸到另一個模塊的常用選擇。

發表于 06-14 08:59

?437次閱讀

基于寄存器的同步FIFO

? FIFO 是FPGA設計中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機制,是設計人員將數據從一個模塊傳輸到另一個模塊的常用選擇。 在這篇文章中,展示了一個簡單的 RTL 同

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過?

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過? 異步FIFO中讀地址同步在寫時鐘域時序分析

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用? 1.

同步FIFO和異步FIFO區別介紹

1. FIFO簡介 FIFO是一種先進先出數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,使用起來非常簡單,缺點是只能順序讀寫,而不能隨機讀寫。 2. 使用場景 數據緩沖:也就是數據寫入過快

同步FIFO設計分析

同步FIFO設計分析

評論