引言

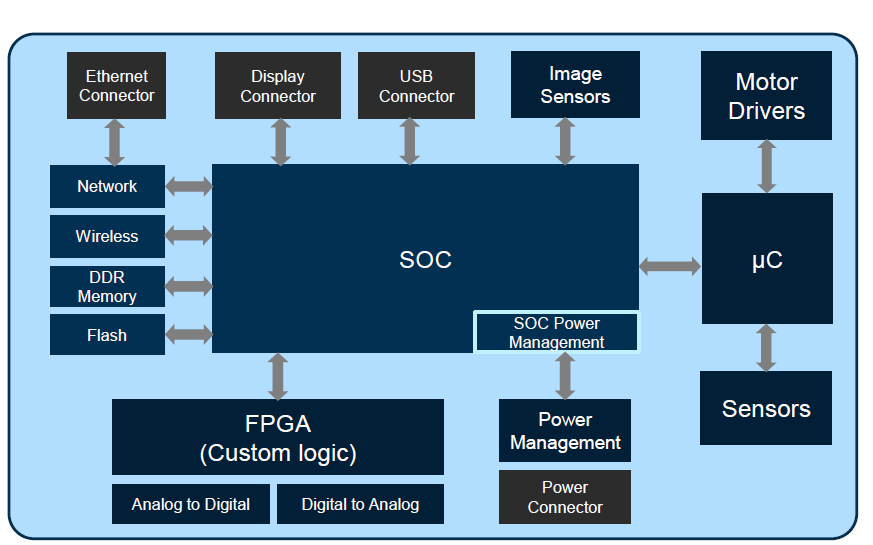

在系統芯片(SoC)設計中, DDR模塊是一種重要的組成部分。它不僅在提高系統性能方面起著關鍵作用,還對于優(yōu)化系統功耗管理具有重要意義。本文將詳細介紹DDR模塊在SoC設計中的應用,包括其定義、作用、設計原則和注意事項。

DDR模塊的定義與作用

DDR(Double Data Rate)模塊是一種高速緩存存儲器,它通過在時鐘的上升和下降沿讀取和寫入數據,從而實現更高的數據傳輸速率。在SoC設計中,DDR模塊主要作為外部存儲器接口,連接CPU和其他組件,以提供大容量、高速的數據存儲和訪問能力。

DDR模塊的作用主要包括以下幾點:

提高系統性能:DDR模塊能夠提供比傳統靜態(tài)隨機存取存儲器(SRAM)更高的數據傳輸速率,從而加快了數據訪問的速度,提高了系統的響應速度和整體性能。

優(yōu)化系統功耗管理:DDR模塊的功耗相對較低,通過使用DDR模塊作為外部存儲器,可以降低整個系統的功耗。

擴展系統容量:DDR模塊具有更高的存儲密度,可以在有限的物理空間內提供更大的存儲容量,滿足系統對數據存儲的需求。

DDR模塊的設計原則

在SoC設計中,DDR模塊的設計需要遵循以下原則:

單通道與雙通道:DDR模塊既可以使用單通道模式,也可以使用雙通道模式。在單通道模式下,數據在每個時鐘周期傳輸一次;而在雙通道模式下,數據在每個時鐘周期傳輸兩次。因此,雙通道模式能夠提供更高的數據傳輸速率。但是,雙通道模式需要更多的功耗和硬件資源,因此在設計時應根據實際需求進行選擇。

像素分配:在針對圖像和視頻處理應用的SoC設計中,DDR模塊應支持像素分配(Pixel Dump)模式。這種模式下,多個像素值可以打包成一個數據塊進行傳輸,從而提高了數據傳輸的效率。

內存帶寬:在設計DDR模塊時,需要考慮內存帶寬的分配。如果內存帶寬不足,將導致數據傳輸延遲,影響系統的整體性能。因此,需要根據系統需求和各個組件的優(yōu)先級來合理分配內存帶寬。

注意事項

在設計DDR模塊時,還需要注意以下問題:

寄存器的選取:在DDR模塊中,需要使用寄存器來存儲配置參數和狀態(tài)信息。因此,寄存器的選取對于DDR模塊的性能和穩(wěn)定性至關重要。應選取具有快速響應速度和低功耗的寄存器,以確保DDR模塊的正常運行。

輸入輸出映射方式:DDR模塊具有多種輸入輸出映射方式,包括位交織(Bit Interleaved)、字節(jié)交織(Byte Interleaved)等。不同的映射方式會影響數據傳輸的效率,因此在設計時應根據實際需求選擇合適的映射方式。

時序要求:DDR模塊對時序要求非常嚴格,需要保證數據在規(guī)定的時間內傳輸完成。如果時序不滿足要求,可能會導致數據傳輸錯誤,甚至損壞DDR模塊。因此,在設計中需要仔細考慮時序問題,確保各個組件之間的數據傳輸時序配合得當。

ECC校驗:為了提高系統的可靠性,DDR模塊通常支持錯誤檢測與糾正(ECC)功能。通過使用ECC校驗,可以檢測并糾正存儲在DDR模塊中的數據錯誤,保證數據的完整性和準確性。在設計時,需要根據實際應用需求來確定是否需要使用ECC校驗功能。

電源管理:DDR模塊的電源管理也是設計中需要考慮的重要問題。為了優(yōu)化系統性能和功耗,需要仔細規(guī)劃DDR模塊的電源分布和電壓降分配。此外,還需要考慮電源噪聲對DDR模塊性能的影響,并采取相應的措施來抑制噪聲干擾。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

電源管理

+關注

關注

115文章

6159瀏覽量

144257 -

DDR

+關注

關注

11文章

711瀏覽量

65237 -

SoC設計

+關注

關注

1文章

148瀏覽量

18764 -

SRAM存儲器

+關注

關注

0文章

88瀏覽量

13281

原文標題:soc 設計中的 DDR 模塊

文章出處:【微信號:快樂的芯片工程師,微信公眾號:快樂的芯片工程師】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

Rockchip SoC上的圖像信號處理模塊基本知識介紹

DDR SDRAM控制器的設計與實現

關于DDR應用的一般注意要點的詳細介紹

PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用

外設SPI在SOC設計中的應用

DDR4時序參數介紹

DDR Inline ECC在Jacinto7 SoC中的應用

詳細介紹DDR模塊在SoC設計中的應用

詳細介紹DDR模塊在SoC設計中的應用

評論